Design integrado com FPGAs:Construindo um projeto

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas:

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas:1:Recursos de hardware

2:Linguagens de implementação

3:Processo de desenvolvimento

4:Construindo um projeto (este artigo)

5:Implementação

Adaptado de Architecting High-Performance Embedded Systems, de Jim Ledin.

Desenvolvendo seu primeiro projeto FPGA

Nesta seção, iremos desenvolver e implementar um projeto simples, mas completo, usando um dispositivo Xilinx Artix-7 FPGA instalado em uma placa de desenvolvimento Digilent Arty A7. Esta placa vem em duas variantes, uma versão de baixo custo (US $ 129) com um número de modelo terminando em -35T e uma versão mais capaz, mas mais cara (US $ 249) com um número de modelo terminando em -100T. A única diferença entre as duas placas é o modelo do FPGA Artix-7 instalado na placa. Como era de se esperar, o -35T tem menos recursos disponíveis do que o -100T.

Você pode usar a variante -35T ou -100T para este projeto. A única diferença no processo de desenvolvimento é especificar o modelo correto de placa sempre que houver necessidade. No entanto, em capítulos posteriores, a variante -100T será necessária devido aos requisitos de recursos do design do projeto do osciloscópio digital de exemplo, portanto, a placa mais capaz é recomendada.

As placas Arty A7 estão disponíveis para compra em https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ e em outras fontes, como a Amazon.

Para o propósito deste projeto, os recursos da placa de interesse são o próprio dispositivo FPGA, bem como as quatro chaves, quatro botões e cinco LEDs. Este projeto irá demonstrar como instalar o conjunto de ferramentas Vivado, criar um projeto, inserir o código HDL, testar o código e, finalmente, produzir um bitstream e fazer o download para a placa. Depois de baixar o fluxo de bits para a placa, você poderá testar manualmente o funcionamento do sistema. Você também verá como programar a imagem FPGA na memória flash da placa Arty A7 para que ela carregue e execute cada vez que a placa for ligada.

Descrição do projeto

Este projeto implementará um somador binário de quatro bits no FPGA. Este é um design intencionalmente muito simples porque o foco aqui é configurar as ferramentas e aprender como usá-las, e não implementar um modelo HDL complexo.

As quatro chaves na placa representam um número binário de 4 bits e os quatro botões representam outro número de 4 bits. A lógica do FPGA executará continuamente uma operação de adição entre esses dois números e exibirá o resultado como um número binário de 4 bits em quatro LEDs com um quinto LED representando o bit de transporte.

O código adicionador de 4 bits é baseado no circuito adicionador completo de um bit descrito nas Linguagens de design de hardware seção do Capítulo 1 , Arquitetura de sistemas incorporados de alto desempenho .

Instalando as ferramentas Vivado

Usaremos a suíte Xilinx Vivado de ferramentas de desenvolvimento FPGA para este projeto e para projetos em capítulos futuros. Essas ferramentas estão disponíveis gratuitamente e são compatíveis com os sistemas operacionais Windows e Linux. Você pode instalar as ferramentas em qualquer sistema operacional. A descrição nesta seção cobre a versão Windows das ferramentas, mas se você estiver instalando no Linux, as diferenças devem ser óbvias. Trabalhar com as ferramentas Vivado deve ser quase idêntico nos diferentes sistemas operacionais:

- Se ainda não tiver uma, crie uma conta de usuário Xilinx em https://www.xilinx.com/registration/create-account.html.

- Visite https://xilinx.com e faça login em sua conta de usuário. Uma vez conectado, vá para a página de download de ferramentas em https://www.xilinx.com/support/download.html.

- Faça download do Instalador unificado Xilinx:instalador da Web de extração automática do Windows . Você provavelmente deve selecionar a versão mais recente disponível, mas se quiser acompanhar a versão usada neste livro, selecione a versão 2020.1 .

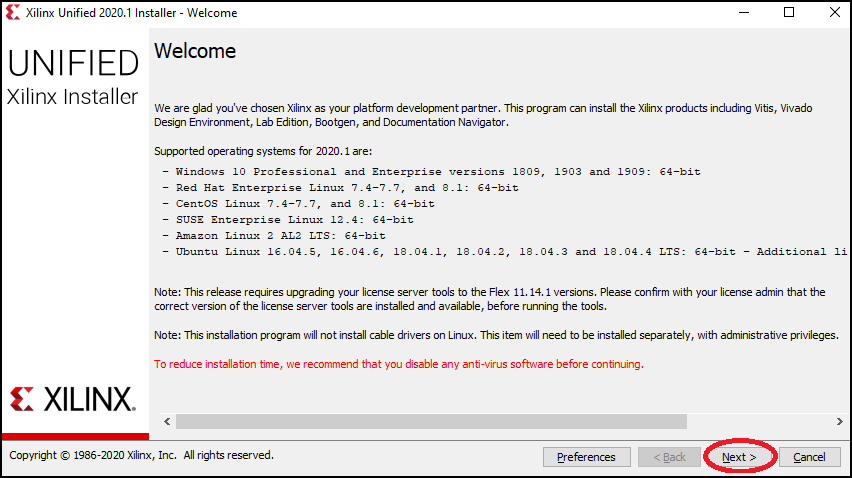

- O arquivo do instalador terá um nome semelhante a Xilinx_ 1_0602_1208_Win64.exe. Localize esse arquivo no diretório de downloads e execute-o. Se uma caixa de diálogo avisar sobre a instalação de um aplicativo que não seja verificado pela Microsoft, clique em Instalar mesmo assim .

- Quando o Bem-vindo tela aparecer, clique em Avançar :

Figura 4.3 - Caixa de diálogo de boas-vindas do instalador

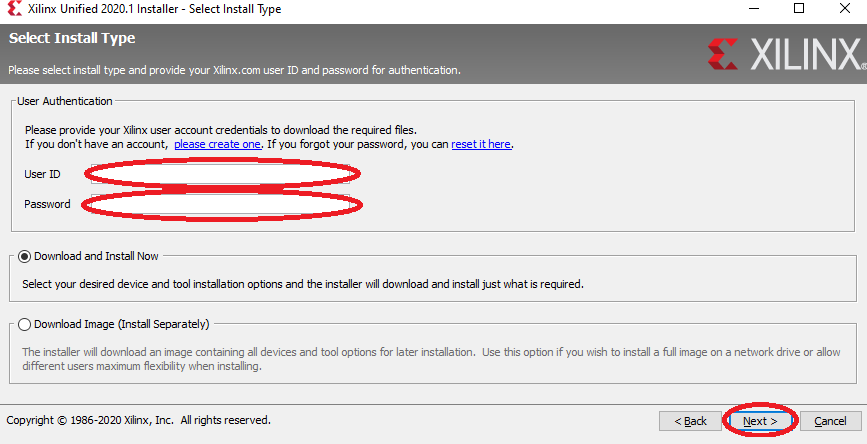

- Na tela a seguir, insira seu ID de usuário e senha xilinx.com e clique em Avançar :

Figura 4.4 - Caixa de diálogo de login do instalador

- A próxima caixa de diálogo solicita que você aceite alguns contratos de licença. Marque as caixas que dizem Concordo e clique em Avançar .

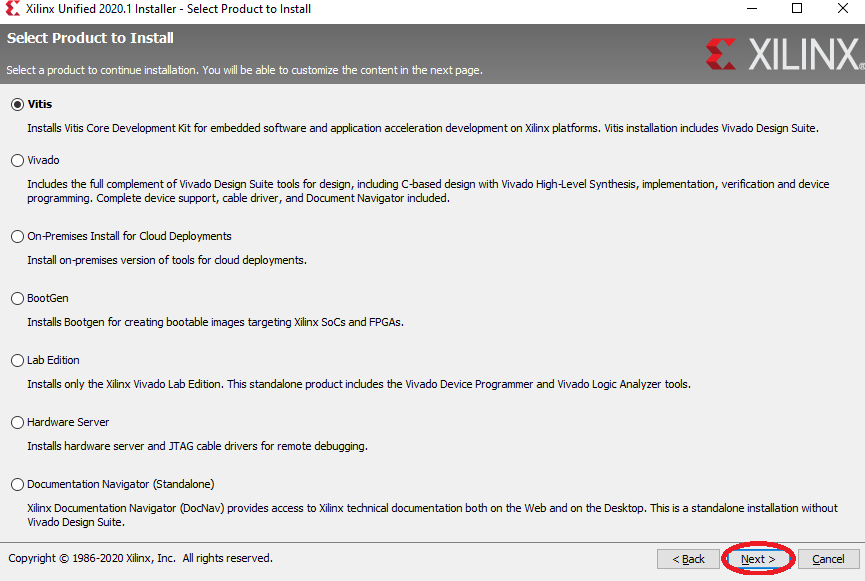

- Na próxima caixa de diálogo, saia de Vitis selecionado como o produto a ser instalado e clique em Avançar . Vitis inclui o conjunto de ferramentas Vivado junto com uma coleção de outras ferramentas de desenvolvimento Xilinx:

Figura 4.5 - Caixa de diálogo de seleção do produto do instalador

- A próxima caixa de diálogo permite que você selecione os componentes de software a serem instalados. Deixe as seleções com seus valores padrão e clique em Avançar .

- A próxima caixa de diálogo permite que você selecione um diretório de destino e especifique as opções de atalho do programa. Um diretório de destino de C:\ Xilinx é um local adequado. Crie este diretório se ele não existir. Clique em Avançar .

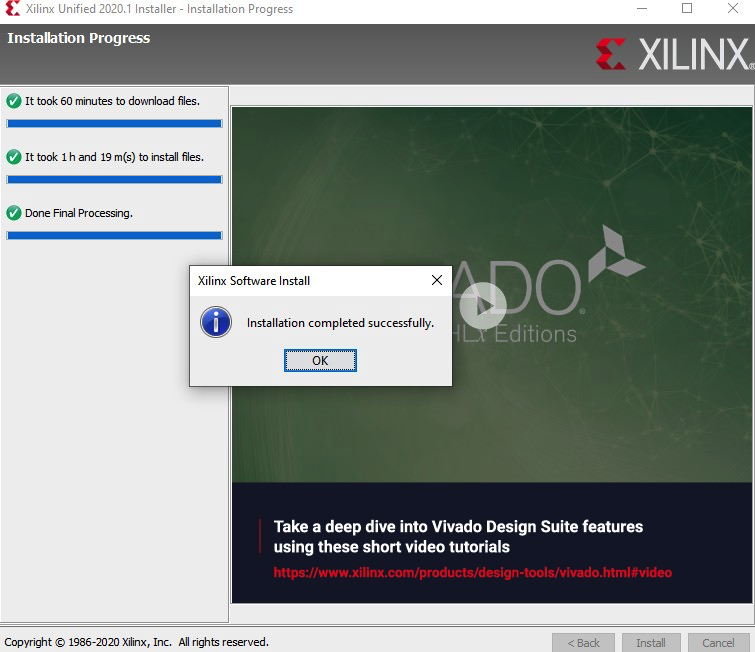

- A próxima caixa de diálogo exibe um resumo das opções de instalação. Clique em Instalar para prosseguir com a instalação. Dependendo da velocidade do seu computador e da sua conexão com a Internet, a instalação pode levar algumas horas para ser concluída:

Figura 4.6 - Diálogo de instalação completa

Concluída a instalação, criaremos em seguida nosso primeiro projeto.

Criando um projeto

Siga estas etapas para criar e construir o projeto de somador binário de 4 bits para a placa Arty A7:

- Localize o ícone da área de trabalho intitulado Vivado 2020.1 (ou procure o número da sua versão, se for diferente) e clique duas vezes nele.

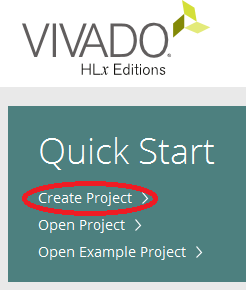

- Quando o Vivado exibir sua tela principal, clique em Criar projeto no Início Rápido seção:

Figura 4.7 - Caixa de diálogo de início rápido do Vivado

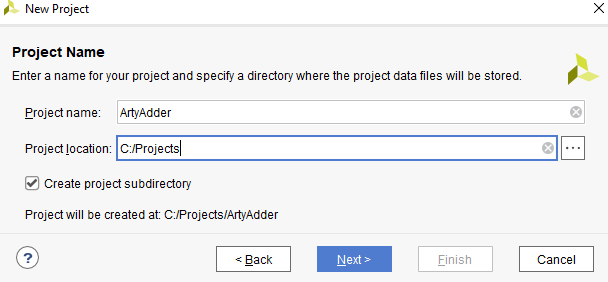

- Isso iniciará o Criar um novo projeto Vivado bruxo. Clique em Avançar para chegar ao Nome do Projeto página e insira ArtyAdder como o nome do projeto. Selecione um local de diretório apropriado para o projeto, marque a caixa para criar um subdiretório e clique em Avançar . Os exemplos neste livro usarão o diretório C:\ Projects como o local para todos os projetos:

Figura 4.8 - Caixa de diálogo Nome do Projeto

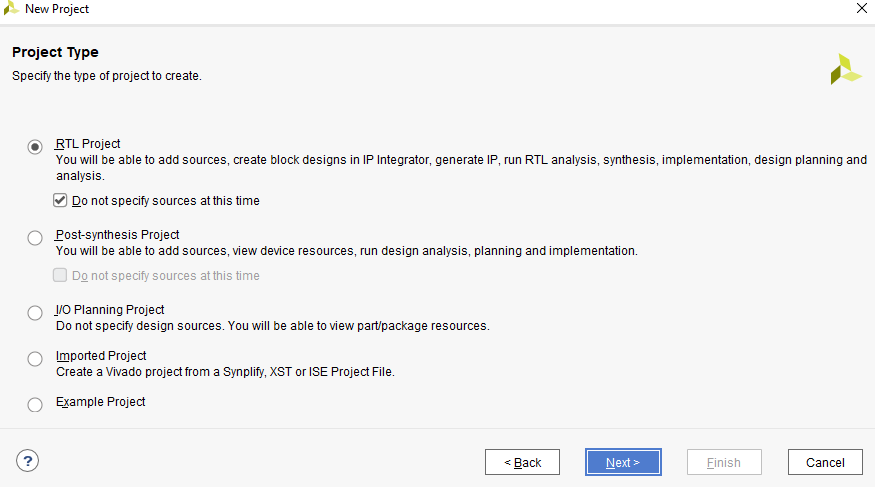

- No tipo de projeto caixa de diálogo, selecione Projeto RTL e marque a caixa ao lado de Não especificar fontes neste momento . Clique em Avançar :

Figura 4.9 - Caixa de diálogo Tipo de Projeto

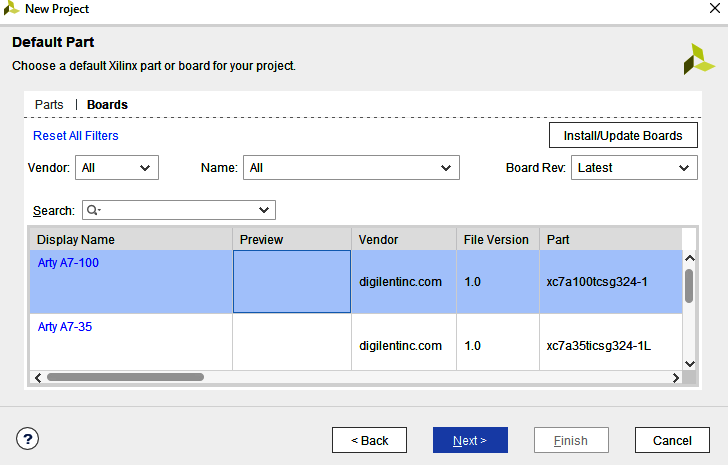

- Na parte padrão caixa de diálogo, clique em Quadros guia e digite Arty em Pesquisar campo. Dependendo do tipo de placa que você possui (ou se ainda não tiver uma placa), selecione Arty A7-100 ou Arty A7-35 e clique em Avançar :

Figura 4.10 - Caixa de diálogo Parte Padrão

- No Resumo do Novo Projeto caixa de diálogo, clique em Concluir .

Agora criamos um projeto vazio. Na próxima seção, criaremos arquivos de origem VHDL contendo o projeto do circuito lógico para este projeto.

Criando arquivos de origem VHDL

As etapas a seguir descrevem o processo de criação de arquivos de origem VHDL, inserção do código-fonte e compilação do design FPGA:

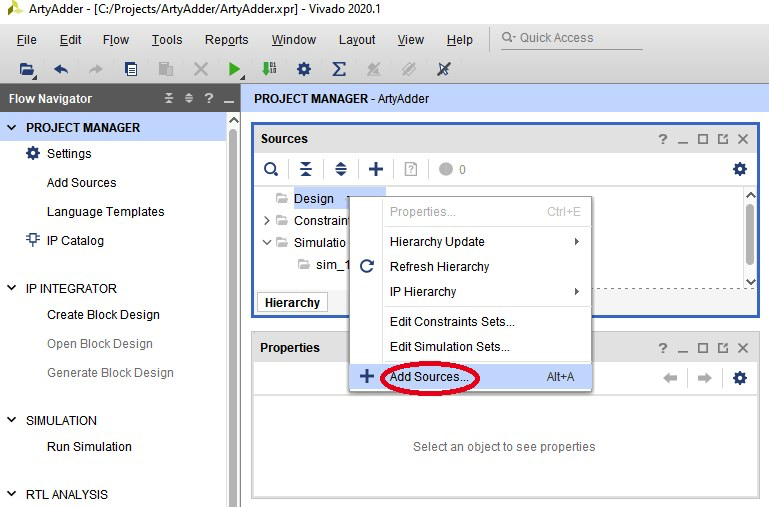

- Em Fontes subjanela, clique com o botão direito em Design Sources e selecione Adicionar fontes… :

Figura 4.11 - Adicionar fontes… seleção do menu

- Em Adicionar fontes caixa de diálogo, certifique-se de Adicionar ou criar fontes de design for selecionado e clique em Avançar .

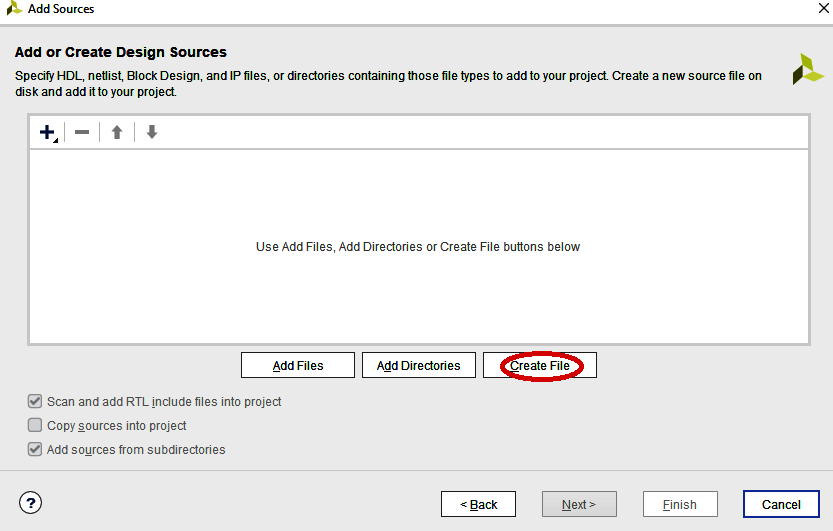

- Em Adicionar ou criar fontes de design caixa de diálogo, clique em Criar arquivo :

Figura 4.12 - Caixa de diálogo Adicionar ou Criar Fontes de Projeto

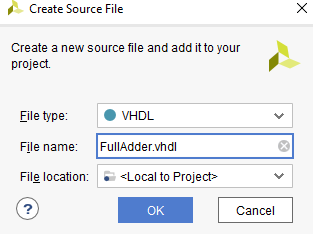

- Digite o nome do arquivo FullAdder.vhdl e clique em OK :

Figura 4.13 - Caixa de diálogo Criar arquivo de origem

- Repita as duas etapas anteriores para criar outro arquivo chamado Adder4.vhdl e clique em Concluir em Adicionar ou criar fontes de design diálogo.

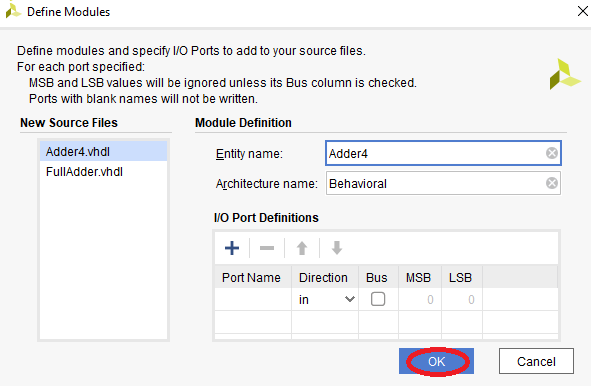

- O Definir Módulos a caixa de diálogo aparecerá em seguida. Não entraremos em nada aqui. Clique em OK para fechar isso Você será perguntado se tem certeza de que deseja usar esses valores. Clique em Sim :

Figura 4.14 - Caixa de diálogo Definir Módulos

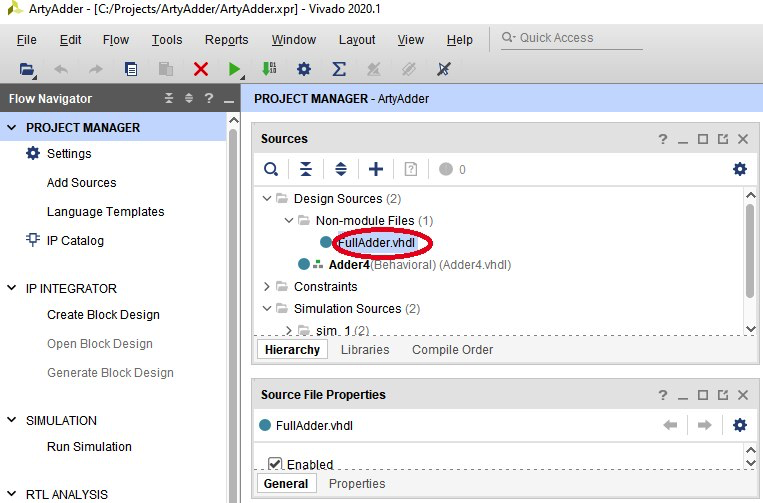

- Expanda os Arquivos não modulares em Fontes de Design e clique duas vezes em FullAdder.vhdl. Uma janela do editor será aberta exibindo o arquivo FullAdder.vhdl vazio:

Figura 4.15 - Arquivo fonte recém-criado

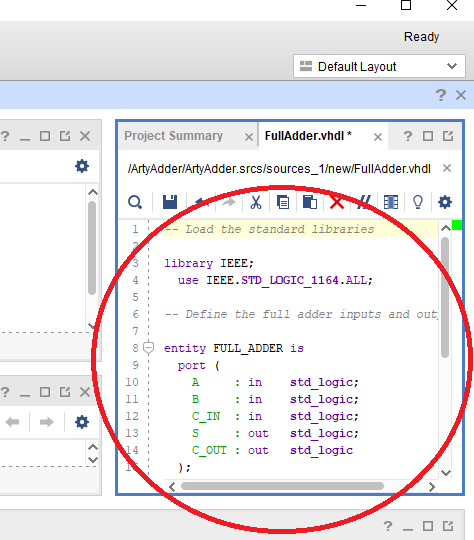

- Insira o seguinte código VHDL na janela do editor FullAdder.vhdl:

- Carrega a biblioteca de bibliotecas padrão IEEE; use IEEE.STD_LOGIC_1164.ALL; - Defina as entradas do somador completo e a entidade de saída FULL_ADDER é a porta (A:em std_logic; B:em std_logic; C_IN:em std_logic; S:fora de std_logic; C_OUT:em std_logic de saída); entidade final FULL_ADDER; - Definir o comportamento da arquitetura completa BEHAVIORAL de FULL_ADDER isbegin S <=(A XOR B) XOR C_IN; C_OUT <=(A AND B) OR ((A XOR B) AND C_IN); arquitetura final COMPORTAMENTE;

Este é o mesmo código de somador completo de um único bit que examinamos nas Linguagens de design de hardware seção do Capítulo 1, Arquitetura de sistemas incorporados de alto desempenho . Figura 4.16 mostra o código na janela do editor Vivado:

Figura 4.16 - Código-fonte FullAdder.vhdl

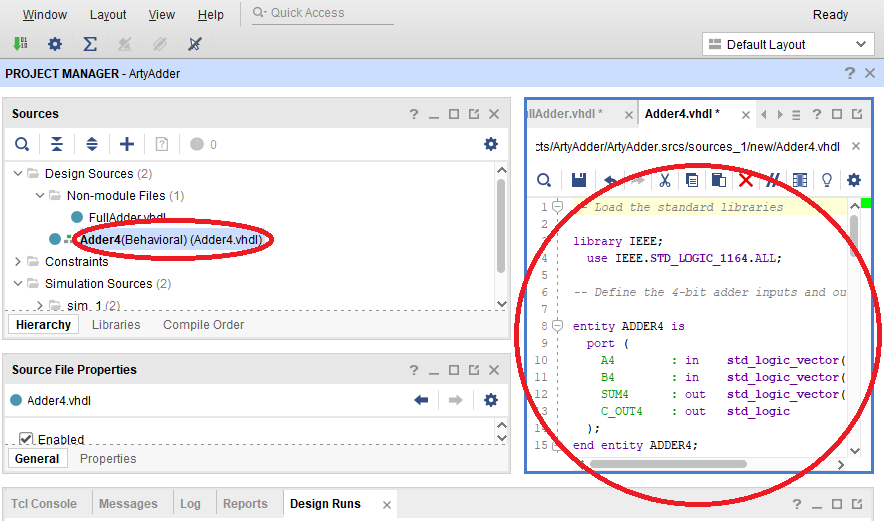

- Da mesma maneira, clique duas vezes em Adder4 (Behavioral) (Adder4.vhdl) em Fontes de Design . Exclua o conteúdo preenchido automaticamente de Adder4.vhdl janela do editor e insira o seguinte código no Adder4.vhdl editor:

- Carrega a biblioteca de bibliotecas padrão IEEE; use IEEE.STD_LOGIC_1164.ALL; - Defina as entradas do somador de 4 bits e a entidade de saída ADDER4 é a porta (A4:em std_logic_vector (3 em 0); B4:em std_logic_vector (3 em 0); SUM4:fora de std_logic_vector (3 em 0) ); C_OUT4:out std_logic); entidade final ADDER4; - Definir o comportamento da arquitetura adderarquitetura de 4 bits BEHAVIORAL de ADDER4 é - Referência a definição anterior do componente adicionador completo FULL_ADDER é a porta (A:em std_logic; B:em std_logic; C_IN:em std_logic; S:out std_logic; C_OUT:out std_logic); componente final; - Defina os sinais usados internamente no sinal adicionador de 4 bits c0, c1, c2:std_logic; begin - A entrada de transporte para o primeiro adicionador é definida como 0 FULL_ADDER0:mapa de porta FULL_ADDER (A => A4 (0), B => B4 (0), C_IN => '0', S => SUM4 (0), C_OUT => c0); FULL_ADDER1:Mapa da porta FULL_ADDER (A => A4 (1), B => B4 (1), C_IN => c0, S => SUM4 (1), C_OUT => c1); FULL_ADDER2:Mapa da porta FULL_ADDER (A => A4 (2), B => B4 (2), C_IN => c1, S => SUM4 (2), C_OUT => c2); FULL_ADDER3:mapa da porta FULL_ADDER (A => A4 (3), B => B4 (3), C_IN => c2, S => SUM4 (3), C_OUT => C_OUT4); arquitetura final COMPORTAMENTO;

Este código instancia quatro cópias do somador completo de bit único. O transporte para o adicionador menos significativo é definido como zero e o transporte de cada adicionador ondula para o próximo adicionador mais significativo. O resultado da adição de dois números de 4 bits é um resultado de 4 bits e um transporte de um único bit:

Figure 4.17 – Adder4.vhdl source code

The next article will show how to test the design and implement our design for the Arty board.

Reprinted with permission from Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin is the CEO of Ledin Engineering, Inc. Jim is an expert in embedded software and hardware design, development, and testing. He is also accomplished in embedded system cybersecurity assessment and penetration testing. He has a B.S. degree in aerospace engineering from Iowa State University and an M.S. degree in electrical and computer engineering from Georgia Institute of Technology. Jim is a registered professional electrical engineer in California, a Certified Information System Security Professional (CISSP), a Certified Ethical Hacker (CEH), and a Certified Penetration Tester (CPT).

Jim Ledin is the CEO of Ledin Engineering, Inc. Jim is an expert in embedded software and hardware design, development, and testing. He is also accomplished in embedded system cybersecurity assessment and penetration testing. He has a B.S. degree in aerospace engineering from Iowa State University and an M.S. degree in electrical and computer engineering from Georgia Institute of Technology. Jim is a registered professional electrical engineer in California, a Certified Information System Security Professional (CISSP), a Certified Ethical Hacker (CEH), and a Certified Penetration Tester (CPT). Related Contents:

- Embedded design with FPGAs:Hardware resources

- Embedded design with FPGAs:Implementation languages

- Embedded design with FPGAs:Development process

- Open-source tools help simplify FPGA programming

- Implementing floating-point algorithms in FPGAs or ASICs

- Leveraging FPGAs for deep learning

- Software tools migrate GPU code to FPGAs for AI applications

- FPGAs displace ASICs in Subaru Eyesight vision-based ADAS

For more Embedded, subscribe to Embedded’s weekly email newsletter.

Integrado

- Fabricação de aditivos líquidos:Construindo objetos 3D com líquido

- O que é design de sistema incorporado:etapas no processo de design

- Transformando big data em dados inteligentes com IA incorporado

- Arrow Electronics lança concurso europeu de desenvolvedores FPGA

- O kit de design mede a pressão arterial com sensor óptico

- Estreia FPGA de defesa com acesso antecipado

- Construindo robôs com Raspberry Pi e Python

- Construindo um segway com Raspberry Pi

- GoPiGo v2 com Windows IoT

- All in com aditivo