Como usar uma instrução Case-When em VHDL

A instrução Case-When fará com que o programa pegue um dentre vários caminhos diferentes, dependendo do valor de um sinal, variável ou expressão. É uma alternativa mais elegante para uma instrução If-Then-Elsif-Else com vários Elsif's.

Outras linguagens de programação têm construções semelhantes, usando palavras-chave como switch , caso , ou selecione . Entre outras coisas, as instruções Case-When são comumente usadas para implementar multiplexadores em VHDL. Continue lendo ou assista ao vídeo para descobrir como!

Esta postagem do blog faz parte da série de tutoriais básicos de VHDL.

A sintaxe básica para a instrução Case-When é:

case <expression> is

when <choice> =>

code for this branch

when <choice> =>

code for this branch

...

end case; O

<expression> geralmente é uma variável ou um sinal. A instrução Case pode conter vários when opções, mas apenas uma opção será selecionada. O

<choice> pode ser um valor único como "11" :when "11" => Ou pode ser um intervalo como

5 to 10 :when 5 to 10 => Ele pode conter vários valores como

1|3|5 :when 1|3|5 => E o mais importante, o

others escolha. Ele é selecionado sempre que nenhuma outra opção for correspondida:when others => O

others escolha é equivalente ao Else ramo na instrução If-Then-Elsif-Else. Exercício

Neste tutorial em vídeo, aprenderemos como criar um multiplexador usando a instrução Case-When em VHDL:

O código final que criamos neste tutorial:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T14_CaseWhenTb is

end entity;

architecture sim of T14_CaseWhenTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output1 : unsigned(7 downto 0);

signal Output2 : unsigned(7 downto 0);

begin

-- Stimuli for the selector signal

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

-- MUX using if-then-else

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

if Sel = "00" then

Output1 <= Sig1;

elsif Sel = "01" then

Output1 <= Sig2;

elsif Sel = "10" then

Output1 <= Sig3;

elsif Sel = "11" then

Output1 <= Sig4;

else -- 'U', 'X', '-' etc.

Output1 <= (others => 'X');

end if;

end process;

-- Equivalent MUX using a case statement

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output2 <= Sig1;

when "01" =>

Output2 <= Sig2;

when "10" =>

Output2 <= Sig3;

when "11" =>

Output2 <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output2 <= (others => 'X');

end case;

end process;

end architecture;

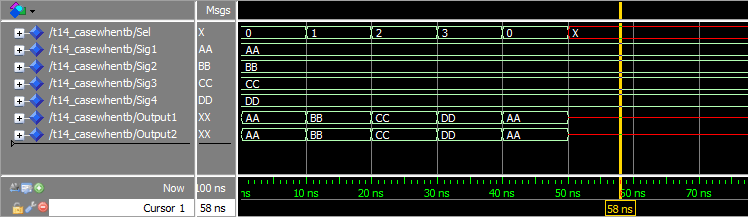

A janela de forma de onda no ModelSim depois que pressionamos executar e ampliamos a linha do tempo:

A saída para o console do simulador quando pressionamos o botão de execução no ModelSim:

VSIM 2> run # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb # ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE # Time: 50 ns Iteration: 1 Instance: /t14_casewhentb

Análise

Primeiro, criamos um processo usando If-Then-Elsif-Else que encaminharia um dos sinais

Sig1 , Sig2 , Sig3 , ou Sig4 , com base no valor do sinal seletor Sel . Em seguida, criamos um processo que fazia exatamente o mesmo, usando a instrução Case-When. Podemos ver pela forma de onda que os sinais de saída dos dois processos,

Output1 e Output2 , se comportam exatamente da mesma forma. Em nosso exemplo, o

Sel sinal tem apenas quatro valores legais. Mas se houvesse um número maior de possibilidades, podemos ver facilmente que a instrução Case-When pode ajudar a tornar o código mais legível. Essa é a maneira preferida de criar esse componente pela maioria dos designers de VHDL. Compreensão do multiplexador foi o ponto de bônus deste exercício. Multiplexadores, ou MUX, são componentes centrais no design digital. É simplesmente uma chave que seleciona uma das várias entradas e a encaminha para a saída.

Esta é uma ilustração de como nosso MUX encaminha o sinal de entrada selecionado:

Usamos o

others cláusula para capturar todos os valores de Sel que não eram uns ou zeros. Como aprendemos no tutorial std_logic, esses sinais podem ter vários valores que não são '0' ou '1' . É uma boa prática de design lidar com esses valores emitindo 'X' . Isso indica um valor desconhecido neste sinal e também será visível na lógica downstream. Podemos ver pela forma de onda que quando o

Sel sinal ficou vermelho, Output1 e Output2 também mudou para "XX" . Este é when others => em ação. Além disso, a saída do console no ModelSim mostra um aviso devido ao

Sel sinal sendo definido como "UU" . As mensagens “** Warning:NUMERIC_STD.”=”:metavalor detectado, retornando FALSE” aparecem no tempo de simulação de 50 ns, que é exatamente quando os sinais ficam vermelhos.

Retirada

- Case-When pode ser usado em vez de várias instruções If-Then-Elsif

- O

when others =>pode ser usado para implementar uma escolha padrão - Os multiplexadores são criados preferencialmente usando instruções Case-When

Ir para o próximo tutorial »

VHDL

- Declaração de Procedimento - Exemplo de VHDL

- Como usamos o molibdênio?

- Como criar uma lista de strings em VHDL

- Como parar a simulação em um testbench VHDL

- Como criar um controlador PWM em VHDL

- Como gerar números aleatórios em VHDL

- Como usar um procedimento em um processo em VHDL

- Como usar uma função impura em VHDL

- Como usar uma função em VHDL

- Como usar um moedor de corte