Como usar o tipo de VHDL mais comum:std_logic

O tipo mais comum usado em VHDL é o

std_logic . Pense nesse tipo como um único bit, a informação digital transportada por um único fio físico. O std_logic nos dá um controle mais refinado sobre os recursos em nosso design do que o integer type, que temos usado nos tutoriais anteriores. Normalmente, queremos que um fio em uma interface digital tenha o valor

'1' ou '0' . Esses dois valores são os únicos valores que um bit, um dígito binário, pode ter. Mas, na realidade, um sinal digital físico pode estar em vários estados, que o std_logic type faz um bom trabalho emulando. Portanto, é o tipo mais usado em VHDL. Esta postagem do blog faz parte da série de tutoriais básicos de VHDL.

O

std_logic type pode ter os seguintes valores:| '1' | Lógica 1 |

| '0' | Lógica 0 |

| 'Z' | Alta impedância |

| 'W' | Sinal fraco, não sei se 0 ou 1 |

| 'L' | 0 fraco, suspenso |

| 'H' | Fraco 1, pullup |

| '-' | Não importa |

| 'U' | Não inicializado |

| 'X' | Desconhecido, vários drivers |

Isso pode parecer muitos estados diferentes para um tipo que deve modelar um único valor binário. Não se preocupe, não usaremos todos esses tipos nesta série de tutoriais. Usaremos

'1' e '0' é claro. E também veremos 'U' e 'X' , o que nos ajudará a identificar erros em nosso design. Os outros valores são recursos VHDL avançados que podem ser usados para coisas como modelagem de comunicação com, por exemplo, I

2

dispositivos C, ou para criar barramentos de três estados. Se vários processos estão tentando escrever valores diferentes em um sinal, dizemos que ele tem vários drivers . Se um

std_logic signal tiver vários drivers, não será um erro de compilação ou de tempo de execução, pelo menos não no simulador. Isso porque std_logic é um tipo resolvido , o que significa que seu valor será determinado por uma função de resolução. O valor de um

std_logic sinal com dois drivers será determinado com base nesta tabela de resolução:| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

Exercício

Neste tutorial em vídeo, aprenderemos como usar declarar e mostrar

std_logic sinais em uma forma de onda:O código final que criamos neste tutorial:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

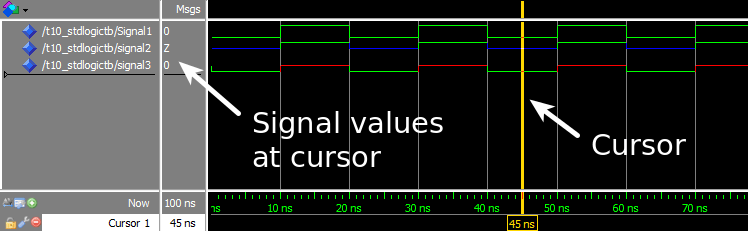

A janela de forma de onda no ModelSim depois que pressionamos executar e ampliamos a linha do tempo:

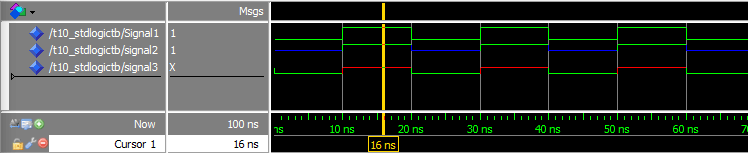

A forma de onda com o cursor posicionado na outra parte do ciclo de sinal repetido:

Análise

O exercício demonstrou como a função de resolução do VHDL funciona com o

std_logic modelo. Ao trabalhar com lógica digital, geralmente é mais prático estudar a linha do tempo em uma forma de onda em vez de usar impressões. Portanto, usamos a forma de onda ModelSim para verificar os valores do sinal neste exercício. O primeiro processo e

Signal1 é usado apenas para alterar o valor que o terceiro processo está direcionando em Signal2 e Signal3 . O segundo processo, Driver A, tentará conduzir um

'Z' para Signal2 , e um '0' para Signal3 constantemente. O terceiro processo, Motorista B, alternará entre dirigir

'1' e 'Z' em ambos Signal2 e Signal3 . Vemos nas capturas de tela da forma de onda que

Signal1 está mudando entre '0' e '1' , porque há apenas um processo tentando conduzir este sinal. Também podemos ver que os vários sinais de driver são resolvidos de acordo com a tabela de resolução postada nos comentários do código VHDL:| Sinal | Motorista A | Motorista B | Resultado |

|---|---|---|---|

| Sinal2 | 'Z' | 'Z' | 'Z' |

| Sinal2 | 'Z' | '1' | '1' |

| Sinal3 | '0' | 'Z' | '0' |

| Sinal3 | '0' | '1' | 'X' |

Retirada

std_logicé o tipo mais comum usado para armazenar um único valor de bit em VHDL- Pense em um

std_logicsinal como um fio físico em nosso design digital - Se vários processos tentarem direcionar um

std_logicsinal, seu valor é determinado por uma tabela de resolução

Ir para o próximo tutorial »

VHDL

- Os gargalos mais comuns do fluxo de trabalho de impressão 3D - e como corrigi-los

- Os problemas mais comuns do sistema de refrigeração de automóveis

- Como aproveitar ao máximo seus dados

- Como criar uma lista vinculada em VHDL

- Como usar um procedimento em um processo em VHDL

- Como usar uma função impura em VHDL

- Como usar uma função em VHDL

- Como usar com segurança um guincho de motor no local de trabalho

- As causas mais comuns de acidentes com guindastes (e como evitá-los)

- As aplicações mais comuns de um286