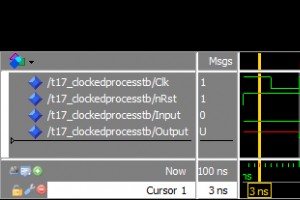

A grande maioria dos designs de VHDL usa lógica com clock , também conhecido como lógica síncrona ou lógica sequencial . Um processo cronometrado é acionado apenas por um sinal de relógio mestre, não quando qualquer um dos outros sinais de entrada muda. O bloco de construção básico da lógica com c

Teste seu progresso com este quiz VHDL depois de completar os tutoriais 12-17 da série Basic VHDL Tutorial! Qual afirmação é verdadeira sobre o tipo assinado? Eles podem representam valores mais altos do que os tipos sem sinal Se o bit mais à esquerda é 1 o valor deve ser negativo O estou

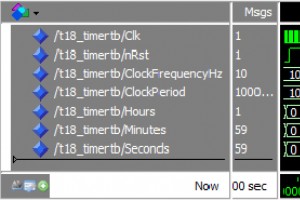

Em tutoriais anteriores, usamos o wait for instrução para atrasar o tempo na simulação. Mas e os módulos de produção? O wait for declaração não pode ser usada para isso. Isso só funciona em simulação porque não podemos simplesmente dizer aos elétrons em um circuito para pausar por um determinado tem

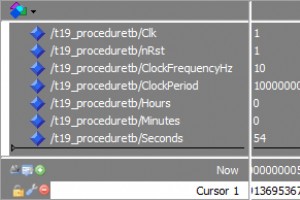

Um procedimento é um tipo de subprograma em VHDL que pode nos ajudar a evitar a repetição de código. Às vezes surge a necessidade de realizar operações idênticas em vários lugares ao longo do projeto. Embora a criação de um módulo possa ser um exagero para operações menores, um procedimento geralmen

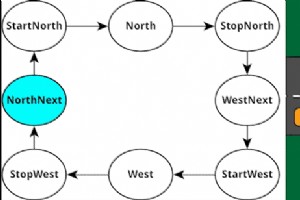

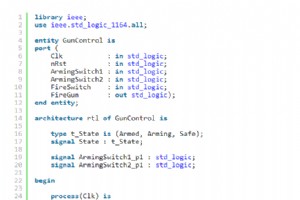

Uma máquina de estado finito (FSM) é um mecanismo cuja saída depende não apenas do estado atual da entrada, mas também dos valores passados de entrada e saída. Sempre que você precisar criar algum tipo de algoritmo dependente do tempo em VHDL, ou se você se deparar com o problema de implementar

Funções são subprogramas em VHDL que podem ser usados para implementar algoritmos usados com frequência. Uma função recebe zero ou mais valores de entrada e sempre retorna um valor. Além do valor de retorno, o que diferencia uma função de um procedimento é que ela não pode conter instruções Wait

Uma função impura pode ler ou escrever qualquer sinal dentro de seu escopo, inclusive aqueles que não estão na lista de parâmetros. Dizemos que a função tem efeitos colaterais . O que queremos dizer com efeitos colaterais é que não é garantido que a função retornará o mesmo valor toda vez que for

É possível conduzir sinais externos de um procedimento. Desde que o sinal esteja dentro do escopo do procedimento, ele pode ser acessado para leitura ou escrita, mesmo que não esteja listado na lista de parâmetros. Os procedimentos que são declarados na região declarativa da arquitetura não podem

Teste seu progresso com este quiz VHDL depois de completar a parte 4 da série Basic VHDL Tutorial! Como medimos em tempo real em VHDL? Usando uma instrução aguarde 1 ns Por contagem períodos de relógio Explorando atraso de propagação Correto! Errado! - Qual afirmação é verdadeira Um

A lista vinculada é uma estrutura de dados dinâmica. Uma lista encadeada pode ser usada quando o número total de elementos não é conhecido antecipadamente. Ele cresce e diminui na memória, em relação ao número de itens que contém. As listas vinculadas são implementadas de maneira mais conveniente

Um testbench de autoverificação é um programa VHDL que verifica a exatidão do dispositivo em teste (DUT) sem depender de um operador para inspecionar manualmente a saída. O testbench de autoverificação é executado inteiramente por conta própria e imprime uma mensagem “OK” ou “Falha” no final. Cada

Um testbench interativo é uma configuração de simulador onde a entrada para o dispositivo em teste (DUT) é fornecida por um operador enquanto o testbench está em execução. Na maioria das vezes, isso significaria digitar comandos no console do simulador para fornecer estímulo ao DUT. Embora você de

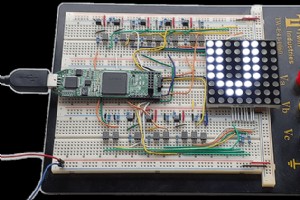

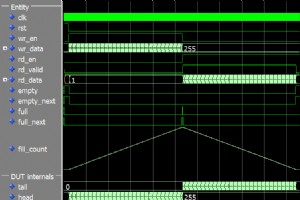

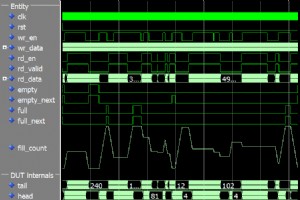

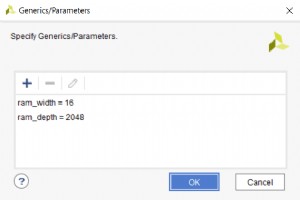

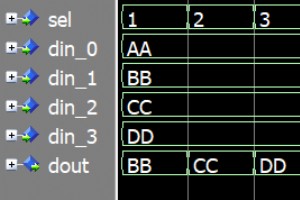

Buffers circulares são construções populares para criar filas em linguagens de programação sequenciais, mas também podem ser implementados em hardware. Neste artigo, vamos criar um ring buffer em VHDL para implementar um FIFO na RAM do bloco. Existem muitas decisões de projeto que você terá que to

A verificação aleatória restrita é uma estratégia de testbench que se baseia na geração de transações pseudo-aleatórias para o dispositivo em teste (DUT). O objetivo é alcançar a cobertura funcional de uma série de eventos predefinidos por meio de interação aleatória com o DUT. A Open Source VHDL

Tenho o prazer de anunciar que o curso de VHDL e FPGA no qual venho trabalhando nos últimos seis meses está começando a ficar completo. O curso está em beta no momento, e estou planejando lançá-lo pela primeira vez neste outono. Para quem é o curso FPGA? O curso de FPGA é destinado ao desenvolvedo

Fiquei um pouco incomodado com as peculiaridades da interface AXI na primeira vez que tive que criar lógica para interfacear um módulo AXI. Em vez dos sinais de controle regulares ocupado/válido, cheio/válido ou vazio/válido, a interface AXI usa dois sinais de controle denominados “pronto” e “válido

Uma maneira conveniente de preencher a RAM do bloco com valores iniciais é ler literais binários ou hexadecimais de um arquivo ASCII. Essa também é uma boa maneira de criar uma ROM (memória somente leitura) em VHDL. Afinal, RAM e ROM são a mesma coisa em FPGAs, ROM é uma RAM que você só lê. Os exe

A leitura de valores de sinal do arquivo é uma forma alternativa de gerar estímulos para o dispositivo em teste (DUT). A sequência e o tempo do testbench são codificados em um arquivo de estímulo que é lido pelo testbench VHDL, linha por linha. Isso permite que você altere facilmente o padrão da for

Converter o arquivo de imagem em um formato de bitmap torna a maneira mais fácil de ler uma imagem usando VHDL. O suporte para o formato de arquivo de imagem de gráficos raster BMP está embutido no sistema operacional Microsoft Windows. Isso torna o BMP um formato de imagem adequado para armazenar f

Este vídeo é uma apresentação introdutória sobre FPGA e tecnologia de lógica programável. Fiz esta palestra de 45 minutos em um evento organizado pela 7 Peaks Software em Bangkok, Tailândia, em 19 de novembro de 2019. Os destaques da apresentação incluem: 05:07 Quem usa FPGAs? 09:06 O que é um F

VHDL