Sincronização e distribuição de redefinição assíncrona - desafios e soluções

A falta de coordenação entre reinicializações assíncronas e relógios lógicos síncronos leva a falhas intermitentes na inicialização. Nesta série de artigos, discutimos os requisitos e desafios do reset assíncrono e exploramos soluções avançadas para projetos ASIC vs FPGA.

Reinicializações assíncronas são tradicionalmente empregadas em projetos VLSI para trazer o circuito síncrono a um estado conhecido após a inicialização. A operação de liberação de reinicialização assíncrona deve ser coordenada com o sinal de relógio lógico síncrono para eliminar falhas de sincronização devido à possível contenção entre a reinicialização e o relógio. A falta dessa coordenação leva a falhas intermitentes na inicialização. O problema se agrava quando grandes projetos de domínio de múltiplos relógios são considerados. Além dos problemas de sincronização, a distribuição de um reset assíncrono para milhões de flip-flops é um desafio, exigindo técnicas semelhantes ao CTS (Clock Tree Synthesis) e exigindo área e recursos de roteamento semelhantes.

Os requisitos e desafios da reinicialização assíncrona são revisados, com foco nos problemas de sincronização e distribuição. As desvantagens das soluções clássicas para redefinir a sincronização (redefinir a sincronização da origem da árvore) e distribuição (redefinir a síntese da árvore) são discutidas. Soluções avançadas para convergência de temporização mais rápida e simples e sincronização e distribuição de reset mais confiáveis são apresentadas. Diferentes abordagens para projetos ASIC e FPGA são detalhadas.

A Parte 1 (este artigo) descreve os problemas relacionados às redefinições assíncronas e descreve abordagens para resolvê-los. A Parte 2 discute soluções adicionais para o reset assíncrono correto em ASIC e FPGA. Alguns casos especiais úteis são discutidos na Parte 3.

1 Desafios de redefinição assíncrona

Uma função de reinicialização é normalmente incluída em projetos VLSI digitais para trazer a lógica a um estado conhecido. A reinicialização é necessária principalmente para a lógica de controle e pode ser eliminada da lógica do caminho de dados, reduzindo a área lógica. O reset pode ser síncrono ou assíncrono em relação ao sinal do relógio.

A reconfiguração síncrona requer um relógio ativo, incorre em certa latência relacionada ao ciclo do relógio e pode impactar o tempo dos caminhos de dados. Por outro lado, resets síncronos são determinísticos e não incorrem em metaestabilidade.

O reset assíncrono não requer um relógio ativo para trazer os flip-flops a um estado conhecido, tem uma latência mais baixa do que um reset síncrono e pode explorar pinos de entrada de flip-flop especiais que não afetam o tempo do caminho dos dados. No entanto, as redefinições assíncronas têm uma série de desvantagens:

-

Eles podem causar metaestabilidade em flip-flops, levando a um comportamento não determinístico.

-

As redefinições assíncronas devem ser acessíveis diretamente para habilitar o DFT.

-

Os resets assíncronos podem incorrer em problemas de confiabilidade em aplicações rad-hard, sendo suscetíveis a fenômenos Single Event Transient (SET) [1].

Deixando de lado a discussão sobre qual tipo de reinicialização é melhor [2], neste artigo nos concentramos em questões e soluções relacionadas a reinicializações assíncronas. Algumas das técnicas apresentadas neste artigo são aplicáveis a reconfigurações assíncronas e síncronas.

Reinicializações assíncronas são amplamente utilizadas em projetos digitais. Os drivers típicos de reinicializações assíncronas são portas externas, dependendo do status da fonte de alimentação (circuitos RC, dispositivos watchdog), botões de reinicialização manual e mestres externos, como microprocessadores.

Em muitos casos, as redefinições assíncronas podem ser substituídas por outras síncronas, mas existem algumas situações em que a funcionalidade de redefinição assíncrona é obrigatória. Um exemplo é um projeto síncrono que não obtém nenhum relógio ativo na inicialização (o relógio é instável ou bloqueado para redução de energia), mas requer um certo estado conhecido para suas interfaces externas. Outro exemplo é o projeto de baixa potência que é necessário para minimizar a potência durante o processo de inicialização, sem relógios ativos.

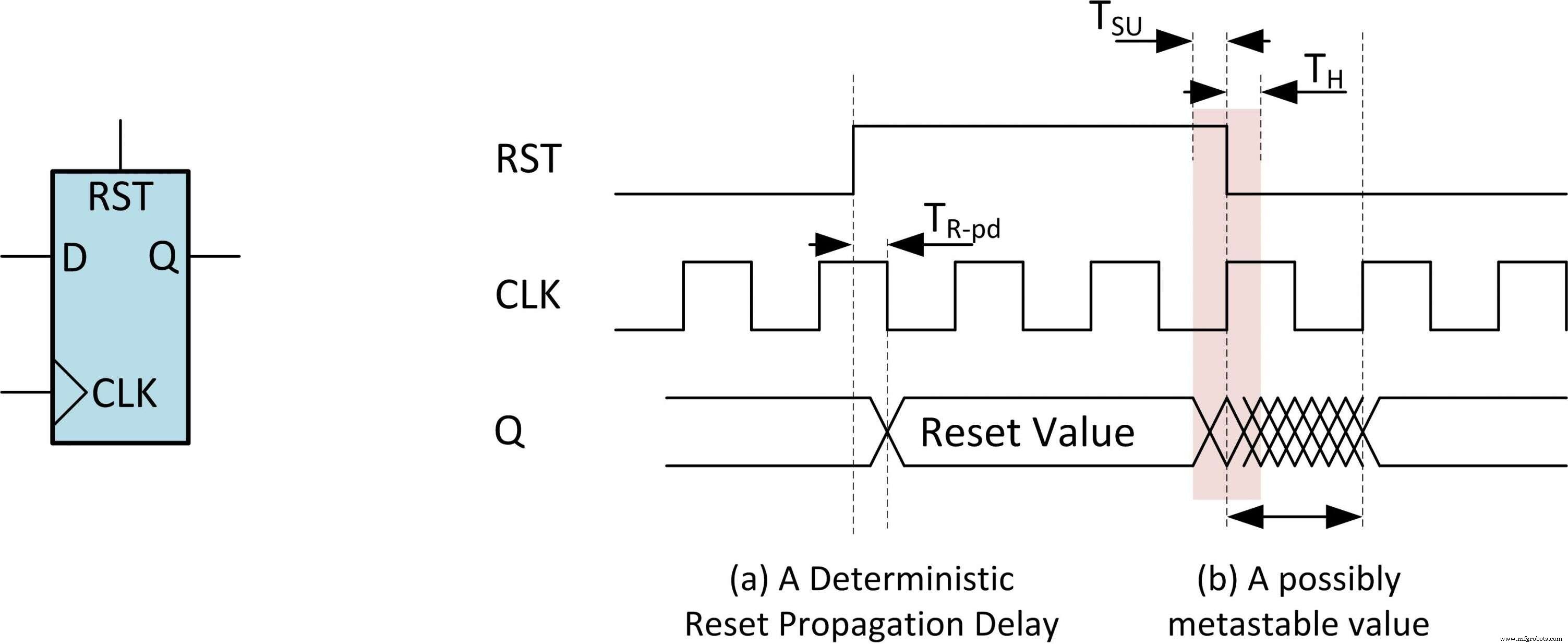

O emprego de reinicialização assíncrona não é simples. Embora o tempo relativo entre o relógio e a reinicialização possa ser ignorado durante a confirmação da reinicialização, a liberação da reinicialização deve ser sincronizada com o relógio. Evitar a sincronização da borda de liberação de redefinição pode levar à metaestabilidade. Referindo-se à Figura 1, um reset alto assíncrono ativo é mostrado. A asserção de reset (a) afeta a saída do flip-flop Q dentro de um tempo limitado deterministicamente (retardo de propagação, T R-pd ) e independentemente do sinal de relógio CLK. Durante a liberação de redefinição (b), as condições de configuração e retenção devem ser satisfeitas para a porta RST em relação à porta CLK do relógio. Uma violação das condições de configuração e retenção para a porta RST (também conhecida como recuperação de redefinição e tempo de remoção) pode fazer com que o flip-flop se torne metaestável, causando falha de design devido à mudança para um estado desconhecido. Observe que esta situação é semelhante à violação das condições de configuração e retenção para a porta de dados do flip-flop, D.

clique para ampliar a imagem

Figura 1:Asserção e liberação de redefinição altamente assíncrona ativa. (a) Uma afirmação de reinicialização assíncrona (b) Uma liberação de reinicialização assíncrona com violação de tempo. (Fonte:circuitos vSync)

Integrado

- Atualizações over-the-air:cinco desafios e soluções típicas

- Principais tendências e desafios de PCBs

- Anvo-Systems e Mouser assinam acordo de distribuição

- Swissbit:soluções de segurança baseadas em hardware para proteger dados e dispositivos

- Rutronik e AP Memory assinam acordo de distribuição global

- Tendências e desafios da IIoT a serem observados

- Segurança de IoT industrial:desafios e soluções

- Desafios de fabricação automotiva e soluções de IoT

- 5 principais desafios e soluções de logística para a indústria de manufatura

- Desafios de projeto de PCB de alta velocidade sobre integridade do sinal e suas soluções