Chip AI acelera o reconhecimento da imagem

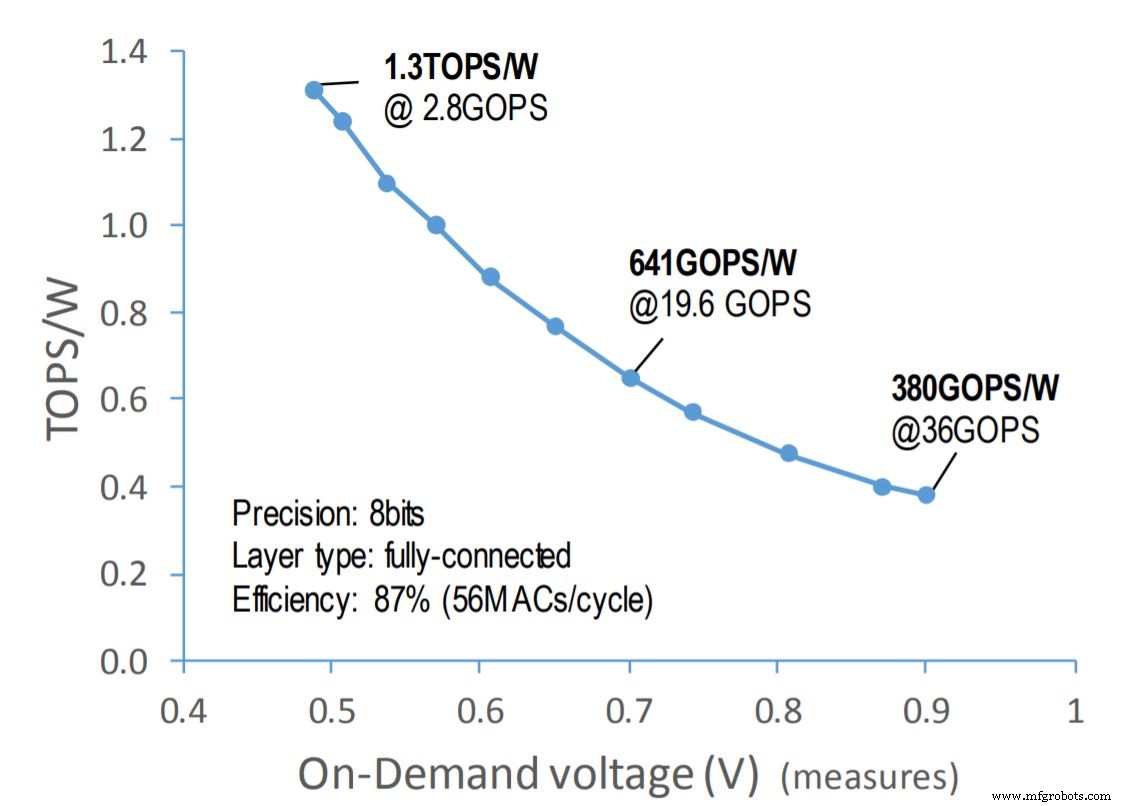

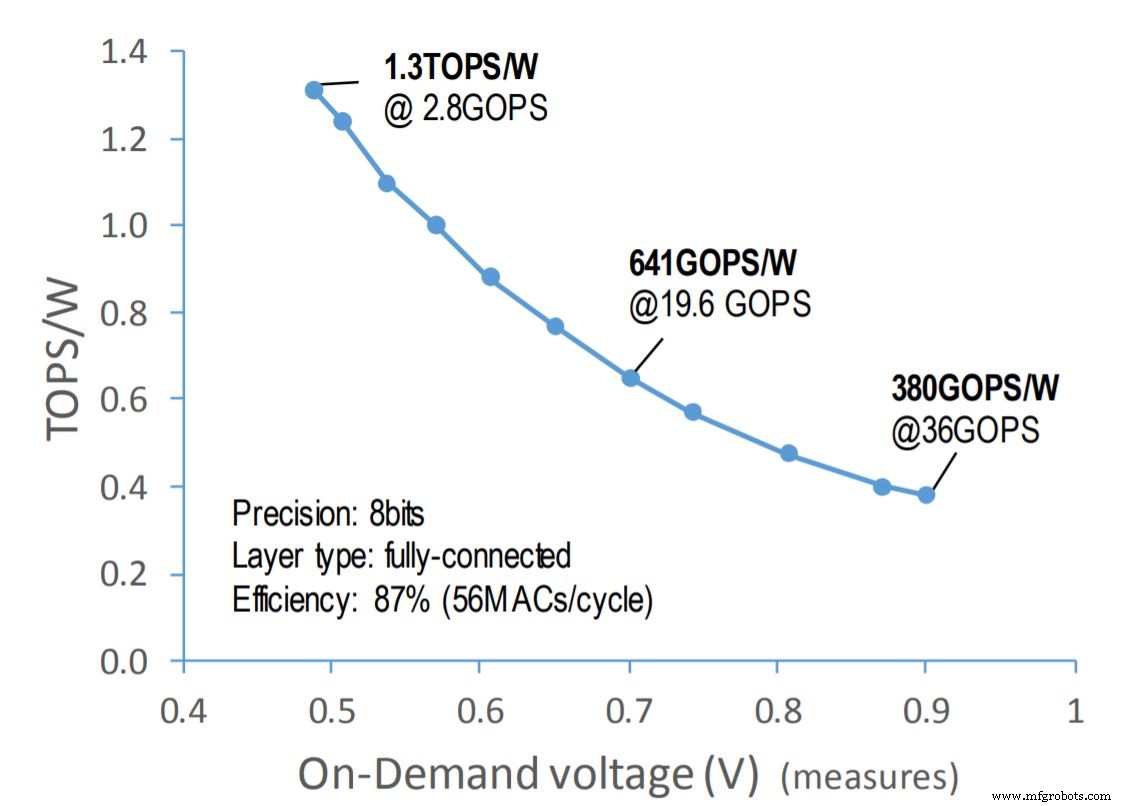

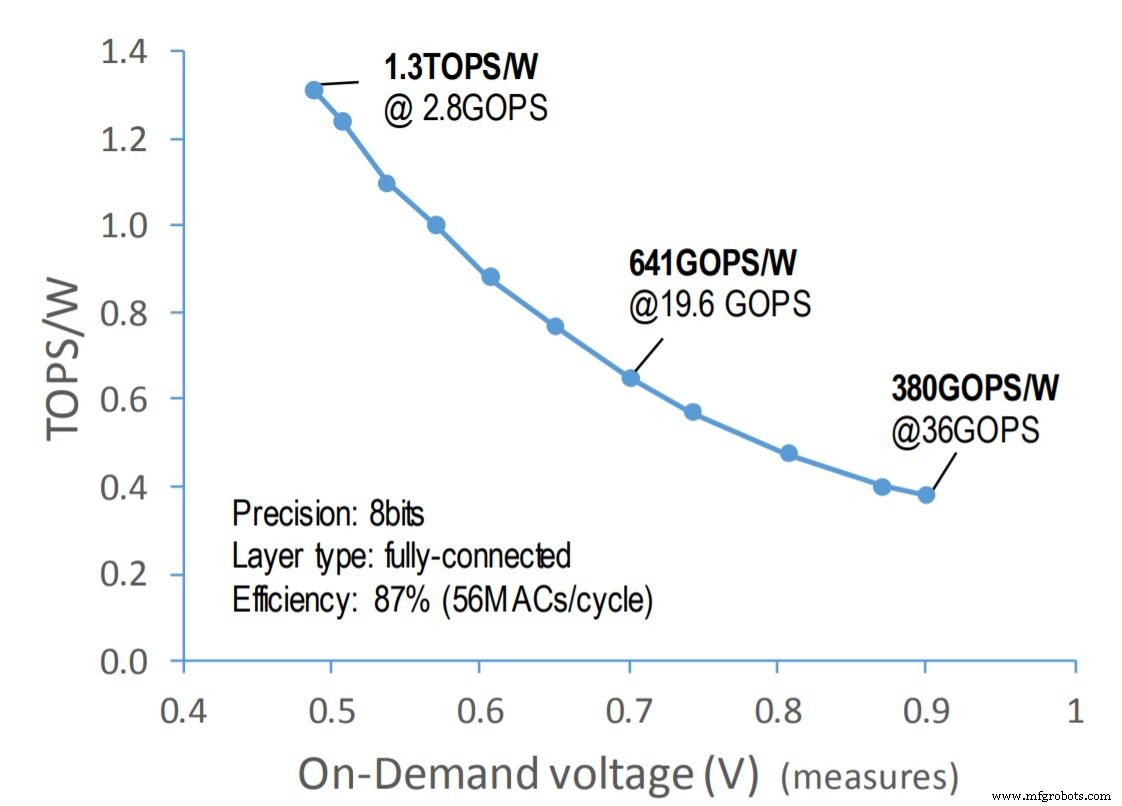

Um chip de prova de conceito dos institutos de pesquisa franceses CEA-Leti e LIST, apresentado no VLSI Symposium 2020, incorpora um nó de IoT de baixa potência e um acelerador de AI e demonstra um tempo de ativação ultrarrápido com 15.000X de pico a redução do consumo de energia ocioso. O nó oferece até 1,3 tera de operações por segundo por Watt (TOPS / W) ou 36 GOPS para tarefas de aprendizado de máquina.

O chip, denominado SamurAI, foi testado em um sistema de detecção de ocupação com componentes prontos para uso, incluindo um sensor PIR, câmera preto e branco de 224 × 224 pixels, FeRAM e um rádio de baixa potência. O consumo médio diário de energia do sistema foi de 105µW, com o SamurAI consumindo 26% desse orçamento. O sistema utilizou o sensor PIR com intervalo de 5s durante a ocupação da sala 8 horas por dia, a câmera a 1 quadro por segundo e o rádio 10x por dia.

Sistema SamurAI

SamurAI usa dois subsistemas no chip:um controlador de despertar acionado por evento sem relógio de baixa potência que pode inicializar em 207 ns, e um subsistema sob demanda que compreende uma CPU RISC-V com modo de hibernação mais acelerador PNeuro AI e aceleradores de criptografia.

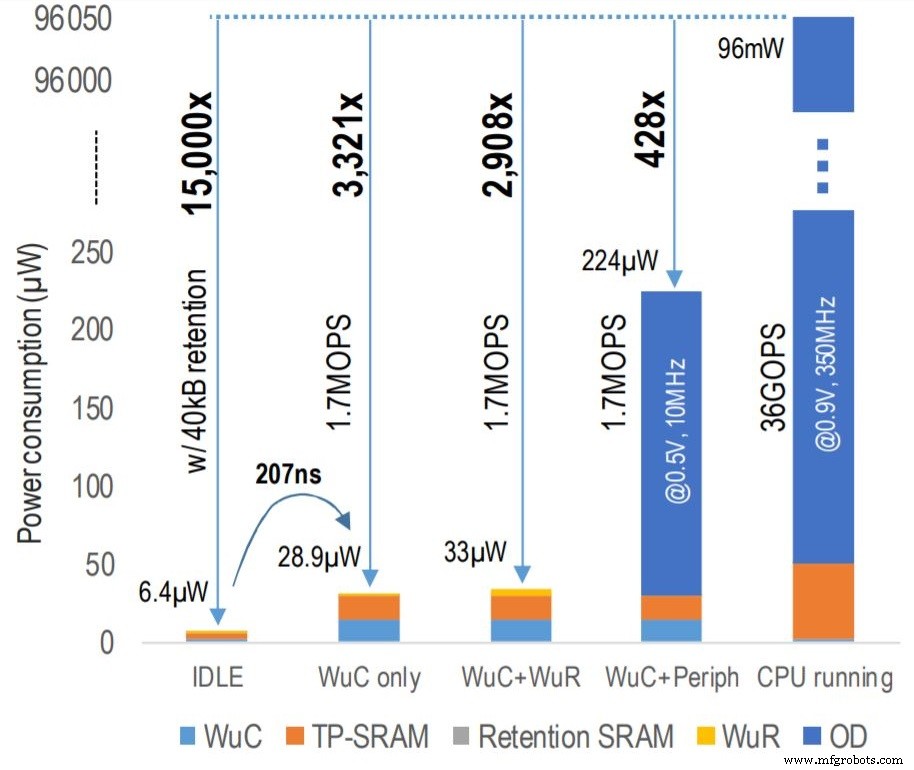

Este esquema de subsistema duplo permite uma relação de potência de pico para inatividade de 15.000 vezes. A figura abaixo mostra o consumo de energia durante os diferentes modos; o modo inativo consome apenas 6,4 µW. Com a CPU e o acelerador AI funcionando, o consumo de energia é de 96 mW.

O chip é construído no processo de silício totalmente empobrecido em isolador (FD-SOI) da STMicro de 28 nm e os valores de potência são fornecidos sem polarização do corpo. O silício tem 4,5 mm 2 e tem 6 domínios de potência comutáveis.

Medições de consumo de energia SamurAI por modos de energia (os modos são LR:ocioso, controlador de despertar (WuC) apenas, controlador de despertar e rádio de despertar (WuR), controlador de despertar e periféricos, e CPU em execução (Imagem:CEA-Leti)

Acelerador AI

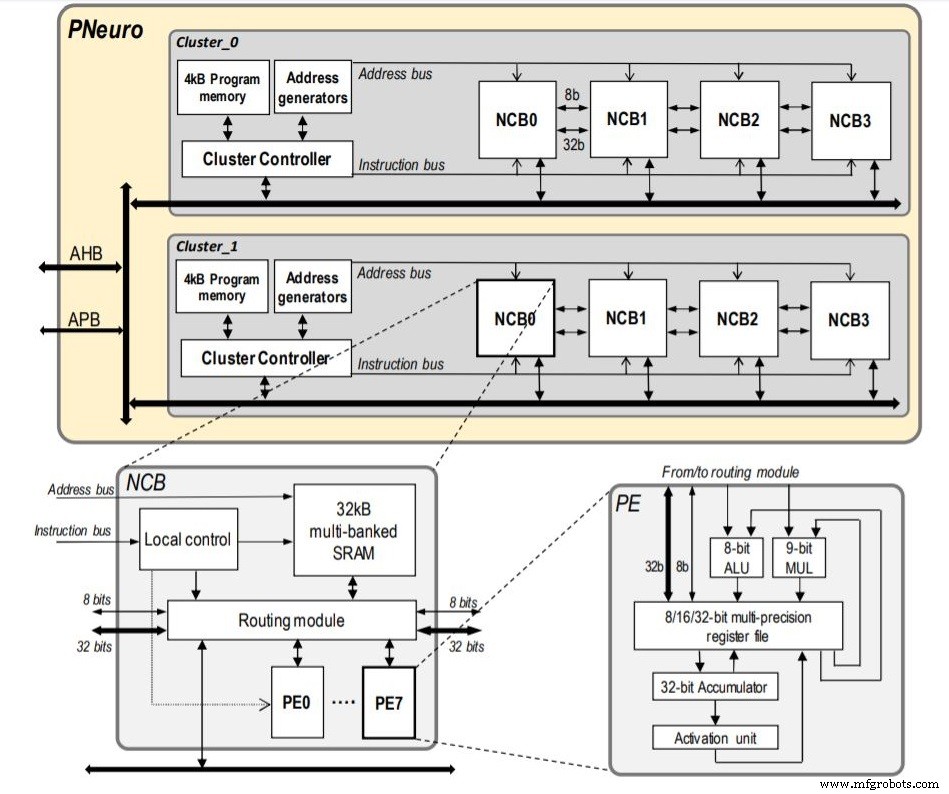

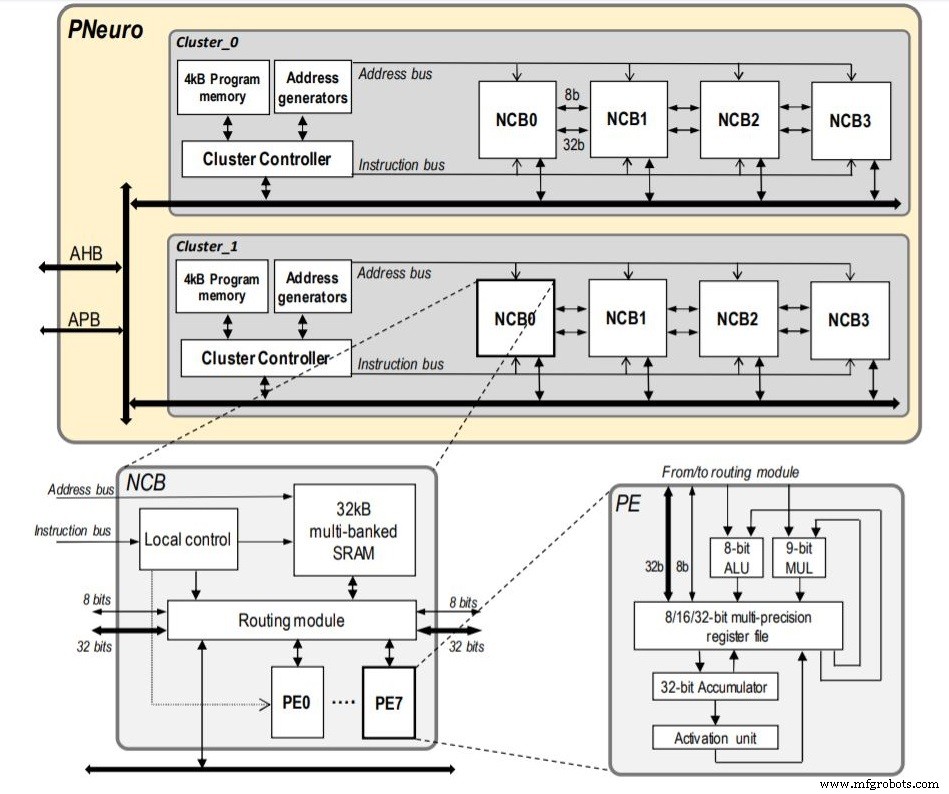

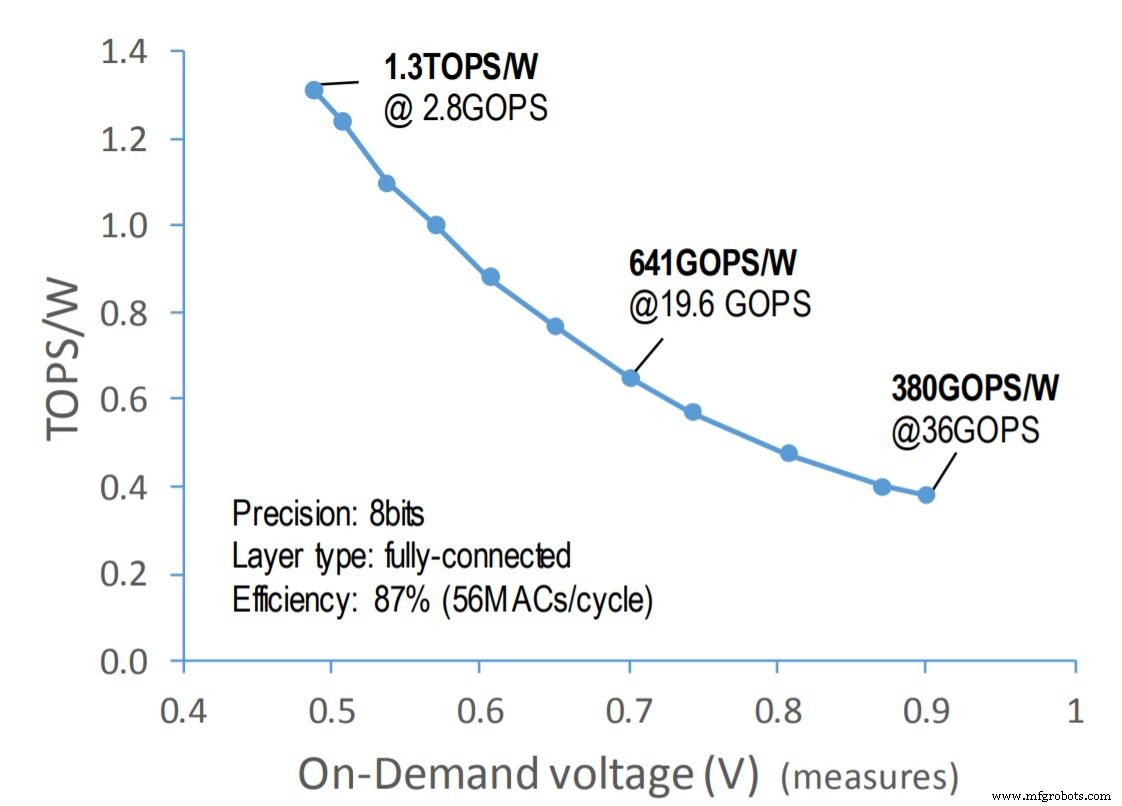

O acelerador de IA do chip, um design que a equipe chama de PNeuro, é um acelerador programável de instrução única e dados múltiplos (SIMD). É composto por 2 clusters de elementos de processamento de 8 bits de 32x com SRAM multibancos de 264kB. Ele pode realizar até 64 multiplicação-acumula (MACs) por ciclo. O bloco PNeuro pode atingir 1,3 TOPS / W a 2,8 GOPS / 0,48V. Ele pode fazer até 36 GOPS a 0,9 V para camadas de rede neural totalmente conectadas de 8 bits.

Usar o acelerador PNeuro reduziu o consumo total de energia do sistema por um fator de 2,3 em comparação com o uso do núcleo do controlador RISC-V para computação de ML.

O design se destina a aplicativos de IoT que precisam de potência de computação esporádica entre longos períodos de “hibernação”. Em vez de se conectar à nuvem, se o nó puder processar a carga de trabalho de AI em si, isso geralmente pode ser concluído mais rápido e não há implicação de privacidade, pois os dados não são compartilhados fora do sistema. Isso pode incluir aplicações como detecção de pessoas ou identificação de cena usando câmeras ou outros sensores.

>> Este artigo foi publicado originalmente em nosso site irmão, EE Times Europe.

Integrado