Design integrado com FPGAs:Linguagens de implementação

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas:

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas: 1:Recursos de hardware

2:Linguagens de implementação (este artigo)

3:Processo de desenvolvimento

4:Construindo um projeto

5:Implementação

Adaptado de Architecting High-Performance Embedded Systems, de Jim Ledin.

Linguagens de implementação FPGA

A implementação de um design para um FPGA, em última análise, se resume ao uso de uma ou mais linguagens de programação de software para definir a funcionalidade do dispositivo.

As linguagens tradicionais usadas para desenvolvimento FPGA são VHDL e Verilog.

As ferramentas de desenvolvimento FPGA da geração atual geralmente oferecem suporte a ambas as linguagens, juntamente com a capacidade de definir as configurações do sistema usando técnicas de diagramação de blocos. Alguns conjuntos de ferramentas também suportam a definição de funcionalidade FPGA usando as linguagens de programação C e C ++ tradicionais.

VHDL

Linguagem de descrição de hardware VHSIC ( VHDL ), onde VHSIC significa Muito Circuito Integrado de Alta Velocidade , tem uma sintaxe que lembra a linguagem de programação Ada. O VHDL foi desenvolvido sob a orientação do Departamento de Defesa dos Estados Unidos a partir de 1983.

Como Ada, VHDL tende a ser bastante prolixo e rigidamente estruturado. Em termos de linguagem de programação, VHDL é fortemente tipado. A linguagem contém um conjunto predefinido de tipos de dados básicos, principalmente booleano, bit, bit_vector, caractere, string, inteiro, real, tempo e array. Todos os outros tipos de dados são definidos em termos dos tipos de base.

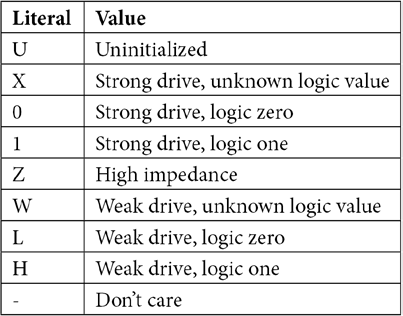

Um conjunto de bibliotecas VHDL foi definido pelo Instituto de Engenheiros Elétricos e Eletrônicos ( IEEE ) e formalizado como o padrão IEEE 1164, Multivalue Logic System for Interoperabilidade do modelo VHDL . Essas bibliotecas definem o conjunto de valores lógicos a serem usados na linguagem VHDL. Esta biblioteca inclui um tipo denominado std_logic, que representa um sinal de 1 bit. Os valores lógicos no tipo std_logic são representados pelos literais de caracteres mostrados na tabela a seguir:

Os valores “fortes” 0 e 1 na figura anterior representam sinais direcionados ao estado binário especificado. Os sinais “fracos” representam sinais dirigidos em um ônibus com múltiplos motoristas, onde qualquer motorista pode se afirmar no ônibus, sobrepondo-se aos outros motoristas. O valor Z representa uma saída CMOS no estado de alta impedância, onde ao invés de conduzir o barramento para um estado 0 ou 1, a saída é efetivamente desconectada do barramento e não o conduz de forma alguma. O estado U representa os valores padrão para todos os sinais. Ao realizar a simulação do circuito, qualquer sinal no estado U será detectado, o que provavelmente indica que um valor não inicializado está sendo usado acidentalmente. O estado X está associado a fios que não possuem nenhuma saída acionando-os. O estado - representa entradas que não são utilizadas e, portanto, não importa em que estado elas estão.

Os projetos de circuito VHDL geralmente começam importando as bibliotecas IEEE 1164 por meio das seguintes instruções:

biblioteca IEEE;

use IEEE.std_logic_1164.all;

Usaremos VHDL em nosso exemplo de projeto posteriormente neste capítulo. Isso não tem a intenção de representar uma forte preferência por VHDL em vez de Verilog. Ambas as linguagens de definição de hardware são totalmente capazes de representar essencialmente qualquer projeto que possa ser sintetizado para um FPGA.

Verilog

A linguagem de descrição de hardware da Verilog ( HDL ) foi introduzido em 1984 e tornou-se padronizado como IEEE 1364 em 2005. Em 2009, o padrão Verilog foi combinado com o SystemVerilog padrão para produzir o padrão IEEE 1800-2009. SystemVerilog contém recursos abrangentes para realizar a verificação do sistema, além dos recursos de design de hardware presentes no Verilog.

Verilog foi projetado para se assemelhar à linguagem de programação C, incluindo precedência de operador semelhante e o uso de algumas das mesmas palavras-chave de fluxo de controle, incluindo if, else, for e while.

Verilog usa o conceito de fio para representar os estados do sinal. Um valor de sinal pode assumir qualquer um dos valores 0, 1, irrelevante (x) ou alta impedância (z) e pode ter um forte ou fraco sinal de força.

Tanto VHDL quanto Verilog definem subconjuntos de linguagem que podem ser usados para projetar circuitos lógicos. Esses subconjuntos são chamados de sintetizável subconjuntos de linguagem. Recursos de linguagem adicionais, além dos subconjuntos sintetizáveis, estão disponíveis para oferecer suporte a tarefas como simulação de circuito. Veremos um exemplo disso posteriormente neste capítulo.

Construções de linguagem não sintetizável tendem a se comportar mais como linguagens de programação de software tradicionais. Por exemplo, um loop for não sintetizável itera através de um bloco de código sequencialmente o número especificado de vezes, assim como em uma linguagem de programação regular. Um loop for sintetizável, por outro lado, torna-se efetivamente desenrolado para gerar uma coleção de construções de hardware replicadas que são executadas em paralelo, representando cada iteração do loop.

Diagramas de blocos

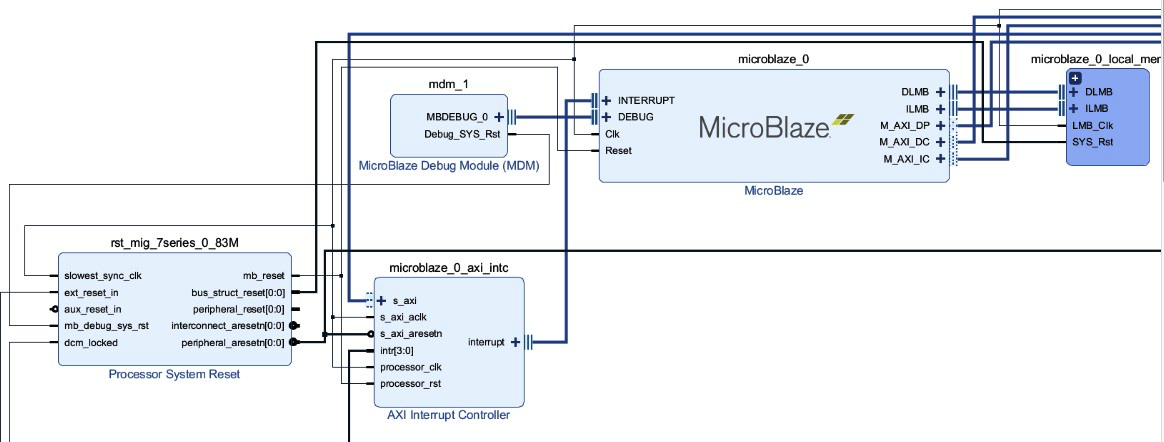

Em um nível de abstração acima dos HDLs baseados em texto, os conjuntos de ferramentas de desenvolvimento FPGA modernos suportam a configuração rápida de projetos de sistema que incorporam componentes lógicos complexos, como microprocessadores e dispositivos de E / S sofisticados usando um formato de estrutura de bloco. Figura 4.2 é um exemplo de uma parte de um diagrama de blocos para um design Xilinx FPGA que incorpora um processador de software MicroBlaze:

clique para ver a imagem em tamanho real

Figura 4.2 - Diagrama de blocos contendo um microprocessador soft MicroBlaze

O processador MicroBlaze é um núcleo de processador fornecido com o conjunto de ferramentas Xilinx Vivado para uso em designs FPGA em famílias de processadores, incluindo o Artix-7.

Embora o uso de diagramas de blocos forneça uma maneira visualmente intuitiva de organizar a instanciação e interconexão de elementos lógicos complexos em um projeto FPGA, é importante lembrar que, por trás do diagrama, a ferramenta de desenvolvimento gera código VHDL ou Verilog para definir os componentes e seus conexões. O diagrama de blocos é simplesmente uma interface de usuário para gerenciar a configuração desses componentes.

Depois de desenvolver um diagrama de blocos, você pode examinar o código HDL gerado, que estará contido nos arquivos associados ao projeto. No diagrama da Figura 4.2 , um arquivo denominado design_1_microblaze_0_0_stub.vhdl é produzido a partir do diagrama. Este arquivo começa com o seguinte código VHDL:

biblioteca IEEE;

use IEEE.STD_LOGIC_1164.ALL;

design de entidade_1_microblaze_0_0 é

Porta (

Clk:em STD_LOGIC;

Reiniciar:em STD_LOGIC;

Interromper:em STD_LOGIC;

Interrupt_Address:em STD_LOGIC_VECTOR (0 a 31);

Interrupt_Ack:out STD_LOGIC_VECTOR (0 a 1);

Instr_Addr:out STD_LOGIC_VECTOR (0 a 31);

Instr:em STD_LOGIC_VECTOR (0 a 31);

Este código começa com uma referência à biblioteca padrão IEEE 1164 e, em seguida, define uma interface para o processador MicroBlaze que expõe os sinais que você esperaria em um microprocessador, incluindo o relógio do sistema, reset, solicitação de interrupção e entradas de vetor de interrupção; reconhecimento de interrupção e saídas de endereço de instrução; e um barramento para as instruções recuperadas da memória.

Este código faz uso dos tipos de dados da biblioteca IEEE 1164 para sinais de bit único (STD_LOGIC) e para sinais de barramento de vários bits (STD_LOGIC_VECTOR).

O código na lista define a interface para o processador MicroBlaze, mas não contém a definição HDL do próprio processador. Projetos complexos de HDL para componentes como microprocessadores são considerados propriedade intelectual valiosa ( IP ) e as entidades comerciais que desenvolvem esses projetos geralmente tomam medidas para garantir que eles não sejam usados sem o licenciamento apropriado. Quando os fornecedores distribuem IP para uso de seus clientes, ele pode ser fornecido em um formato compilado que é opaco para os usuários finais. Isso permite que os usuários incorporem o IP em seus projetos, mas não podem examinar o HDL usado para desenvolvê-lo. Isso é conceitualmente semelhante a desenvolvedores de software que lançam uma biblioteca na forma compilada, mas não fornecem o código-fonte.

C / C ++

Vários fornecedores oferecem ferramentas de software que traduzem linguagens de programação de alto nível tradicionais, geralmente C e C ++, em código HDL para uso no desenvolvimento de FPGA. Essa abordagem pode ser atraente se você tiver um algoritmo complexo em C ou C ++ que gostaria de acelerar em uma implementação FPGA. Essas ferramentas também permitem que os desenvolvedores de software familiarizados com C / C ++ comecem imediatamente a implementar o código para uso em FPGA, sem a necessidade de aprender um dos HDLs.

Enquanto as ferramentas de desenvolvimento FPGA para essas linguagens de alto nível são capazes de otimização significativa da implementação FPGA resultante do algoritmo de código C / C ++, ainda há algo de desconexão porque o modelo de execução C / C ++ envolve a execução sequencial de instruções enquanto o ambiente FPGA nativo consiste em componentes de hardware paralelos. O projeto FPGA resultante do código C / C ++ normalmente se assemelha a uma coleção de máquinas de estado que gerenciam a execução sequencial das operações definidas nas instruções da linguagem de programação. Dependendo da disponibilidade de oportunidades para execução paralela dentro do código C / C ++, uma implementação FPGA pode fornecer um aprimoramento de desempenho significativo em comparação com a execução do mesmo código em um processador tradicional.

Em suítes de ferramentas de desenvolvimento FPGA modernas, todos os métodos de implementação de FPGA descritos nesta seção (VHDL, Verilog, diagramas de blocos e C / C ++) podem ser combinados em um único projeto, se necessário. Por causa disso, um membro da equipe pode preferir trabalhar em VHDL enquanto outro usa Verilog. Pode haver motivos de gerenciamento de projeto para desencorajar o uso de multi-HDL em um único projeto, mas as próprias linguagens funcionam juntas em um único design sem problemas. Uma razão pela qual um gerente de projeto pode desejar evitar o uso de vários HDLs é que a sustentação futura do esforço exigirá a participação de desenvolvedores com habilidades nas duas linguagens.

Da mesma forma, é possível definir uma arquitetura de alto nível para um projeto em termos de um diagrama de blocos e, em seguida, implementar a funcionalidade detalhada do subsistema usando o HDL de escolha. No mesmo projeto, também é possível integrar HDL gerado a partir de um algoritmo C / C ++. Os arquitetos e desenvolvedores de sistemas embarcados devem considerar cuidadosamente as implicações e selecionar o método de implementação apropriado para cada parte de um projeto FPGA.

A próxima seção irá apresentar as etapas do processo de desenvolvimento de FPGA padrão.

Reimpresso com permissão da Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin é o CEO da Ledin Engineering, Inc. Jim é um especialista em software embarcado e design, desenvolvimento e teste de hardware. Ele também tem experiência em avaliação de segurança cibernética de sistemas embarcados e testes de penetração. Ele tem um B.S. formado em engenharia aeroespacial pela Iowa State University e um M.S. graduado em engenharia elétrica e da computação pelo Georgia Institute of Technology. Jim é um engenheiro elétrico profissional registrado na Califórnia, um Certified Information System Security Professional (CISSP), um Certified Ethical Hacker (CEH) e um Certified Penetration Tester (CPT).

Jim Ledin é o CEO da Ledin Engineering, Inc. Jim é um especialista em software embarcado e design, desenvolvimento e teste de hardware. Ele também tem experiência em avaliação de segurança cibernética de sistemas embarcados e testes de penetração. Ele tem um B.S. formado em engenharia aeroespacial pela Iowa State University e um M.S. graduado em engenharia elétrica e da computação pelo Georgia Institute of Technology. Jim é um engenheiro elétrico profissional registrado na Califórnia, um Certified Information System Security Professional (CISSP), um Certified Ethical Hacker (CEH) e um Certified Penetration Tester (CPT). Conteúdos Relacionados:

- Design integrado com FPGAs:recursos de hardware

- Ferramentas de código aberto ajudam a simplificar a programação FPGA

- Implementação de algoritmos de ponto flutuante em FPGAs ou ASICs

- Ferramentas de software migram código GPU para FPGAs para aplicativos de IA

- FPGAs substituem ASICs em ADAS baseado em visão Subaru Eyesight

- Como os FPGAs baseados em flash simplificam os requisitos de segurança funcional

- Aproveitando os benefícios dos FPGAs instantâneos

- Configuração FPGA usando flash NOR de alta velocidade

- Como a tecnologia FPGA está evoluindo para atender aos novos requisitos de sistema de médio porte

Para obter mais informações sobre o Embedded, assine o boletim informativo semanal da Embedded por e-mail.

Integrado

- O que é programação de sistema incorporado e seus idiomas

- O que é design de sistema incorporado:etapas no processo de design

- Transformando big data em dados inteligentes com IA incorporado

- Desafios de implementação da porta USB Type-C e soluções de design

- As principais tendências da indústria estão moldando o design incorporado

- Acelerador FPGA para câmeras MIPI de visão incorporada

- Clientron:terminal PDV multifuncional com impressora integrada

- O kit de design mede a pressão arterial com sensor óptico

- Estreia FPGA de defesa com acesso antecipado

- All in com aditivo