O processamento acústico em tempo real bem-sucedido requer um planejamento cuidadoso

O processamento acústico em tempo real de baixa latência é um fator chave em muitas aplicações de processamento embarcado, entre elas pré-processamento de voz, reconhecimento de voz e cancelamento de ruído ativo (ANC). À medida que os requisitos de desempenho em tempo real aumentam constantemente nesses domínios de aplicativo, os desenvolvedores precisam adotar uma mentalidade estratégica para acomodar adequadamente essas necessidades. Dado o desempenho substancial oferecido por muitos sistemas maiores em chips, pode ser tentador simplesmente carregar esses dispositivos com quaisquer tarefas adicionais que surjam, mas é importante entender que a latência e o determinismo são elementos críticos que podem facilmente levar a um grande sistema em tempo real problemas se não forem considerados cuidadosamente. Este artigo explorará as questões que os designers devem considerar ao escolher entre um SoC e um DSP de áudio dedicado para evitar surpresas desagradáveis em seus sistemas acústicos em tempo real.

Os sistemas acústicos de baixa latência cobrem uma ampla gama de aplicações. Por exemplo, no espaço automotivo sozinho, a baixa latência é crítica para zonas de áudio pessoais, cancelamento de ruído de estrada e sistemas de comunicação dentro do carro, para citar alguns.

Com a tendência emergente de eletrificação de veículos, o ANC se torna ainda mais importante porque não há motor de combustão gerando ruído perceptível. Portanto, os sons associados à interface carro-estrada tornam-se muito mais perceptíveis e ofensivos. A redução desse ruído não apenas cria uma experiência de pilotagem mais confortável, mas também reduz a fadiga do motorista. Existem inúmeros desafios associados à implementação de um sistema acústico de baixa latência em um SoC em oposição a um DSP de áudio dedicado. Isso inclui problemas de latência, escalabilidade, capacidade de atualização, considerações de algoritmo, aceleração de hardware e suporte ao cliente. Vamos examinar cada um deles.

Latência

A questão da latência em sistemas de processamento acústico em tempo real é importante. Se o processador não consegue acompanhar a movimentação de dados em tempo real e as demandas computacionais do sistema, podem ocorrer quedas de áudio inaceitáveis.

Normalmente, os SoCs têm pequenas SRAMs no chip e, portanto, devem contar com o cache para a maioria dos acessos à memória local. Isso introduz disponibilidade não determinística de código e dados e também aumenta a latência de processamento. Para um aplicativo em tempo real como o ANC, isso por si só pode ser um fator decisivo. No entanto, há também o fato de que os SoCs executam sistemas operacionais em tempo não real que gerenciam cargas multitarefa pesadas. Isso amplifica a característica de operação não determinística do sistema, tornando muito difícil suportar o processamento acústico relativamente complexo em um ambiente multitarefa.

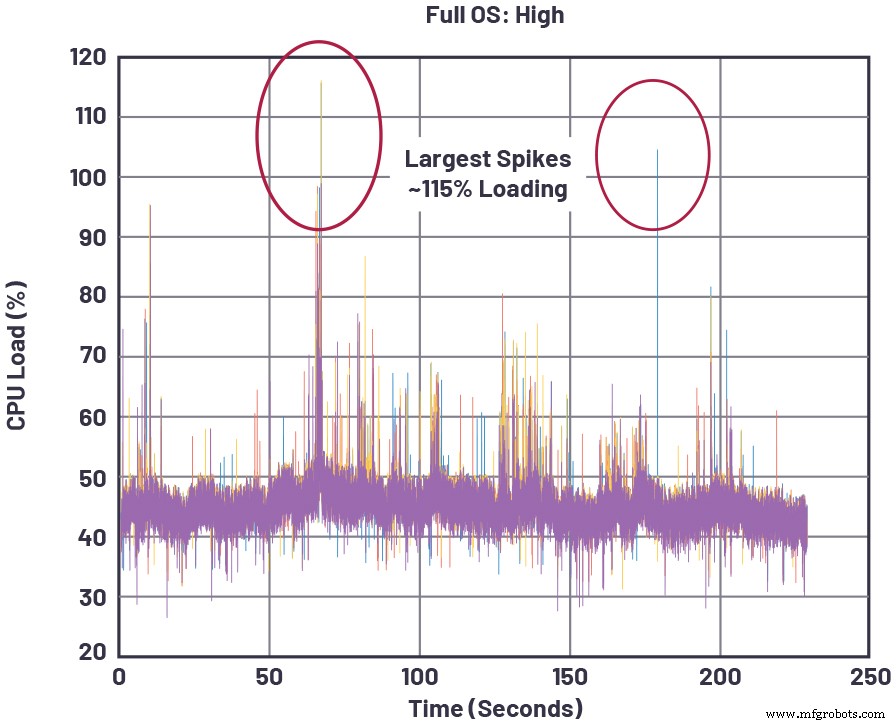

A Figura 1 mostra um exemplo concreto de um SoC executando uma carga de processamento de áudio em tempo real, em que o carregamento da CPU aumenta conforme as tarefas de SoC de prioridade mais alta são atendidas. Esses picos podem ocorrer, por exemplo, devido a atividades centradas em SoC, como renderização de mídia, navegação ou execução de aplicativo no sistema. Sempre que os picos ultrapassam 100% da carga da CPU, o SoC não está mais operando em tempo real e isso resultará em falhas de áudio.

clique para ver a imagem em tamanho real

Figura 1:Cargas instantâneas da CPU para um SoC representativo executando alto processamento de memória de áudio, além de outras tarefas [1]. (Fonte:Dispositivos analógicos)

Os DSPs de áudio, por outro lado, são arquitetados para baixa latência em todo o caminho de processamento do sinal, desde a entrada de áudio amostrada até a saída de alto-falante composto (por exemplo, áudio + anti-ruído). A instrução L1 e a SRAM de dados, a memória de ciclo único mais próxima do núcleo do processador, é ampla o suficiente para suportar muitos algoritmos de processamento sem descarregar dados intermediários para a memória fora do chip. Além disso, a memória L2 no chip (mais distante do núcleo, mas ainda com acesso muito mais rápido do que a DRAM fora do chip) ajuda a fornecer um buffer para operações de dados intermediários quando o armazenamento L1 SRAM é excedido. Finalmente, os DSPs de áudio normalmente executam um sistema operacional em tempo real (RTOS) que garante que os dados de entrada possam ser processados e enviados ao seu destino antes que novos dados de entrada cheguem, garantindo assim que os buffers de dados não estourem durante a operação em tempo real.

A latência real na inicialização do sistema - geralmente medida pela disponibilidade de tempo para áudio - também pode ser uma métrica importante, especialmente em sistemas automotivos onde avisos sonoros devem ser transmitidos dentro de uma determinada janela a partir da inicialização. No mundo do SoC, onde é comum ter uma longa sequência de inicialização que envolve o sistema operacional de todo o dispositivo, pode ser difícil ou impossível atender a esse requisito de inicialização. Por outro lado, um DSP de áudio autônomo executando seu próprio RTOS não afetado por outras prioridades estranhas do sistema pode ser otimizado para inicialização rápida que satisfaça confortavelmente os requisitos de tempo para áudio.

Escalabilidade

Embora as preocupações com latência sejam problemáticas para SoCs em aplicações como controle de ruído, outra lacuna importante para SoCs que desejam realizar processamento acústico é a escalabilidade. Em outras palavras, SoCs que controlam grandes sistemas (como unidades automotivas head-end e clusters) com muitos subsistemas díspares não podem escalar facilmente das necessidades de áudio de gama baixa para alta porque há conflito constante entre as necessidades de escalabilidade de cada componente do subsistema, exigindo compensações na utilização geral do SoC. Por exemplo, se um SoC head-end se conecta a um sintonizador remoto e, em modelos automotivos, esse sintonizador precisa ser escalonado de alguns canais para muitos canais, cada configuração de canal amplificará as preocupações em tempo real mencionadas anteriormente. Isso se deve ao fato de cada recurso adicional sob o controle do SoC alterar o comportamento em tempo real do SoC e a disponibilidade de recursos dos principais componentes arquitetônicos usados por várias funções. Esses recursos incluem aspectos como largura de banda da memória, ciclos de núcleo do processador e slots de arbitragem de malha de barramento de sistema.

Além da preocupação com outros subsistemas que se conectam ao SoC multitarefa, o próprio subsistema acústico tem seus próprios problemas de escalabilidade. Há um escalonamento de ponta a ponta (por exemplo, aumentando o número de canais de microfone e alto-falante em um aplicativo ANC), e também existe o escalonamento da experiência de áudio, da decodificação básica de áudio e reprodução estéreo até a virtualização 3D e outros recursos premium. Embora esses requisitos não compartilhem as restrições de tempo real dos sistemas ANC, eles estão diretamente relacionados à escolha do processador de áudio de um sistema.

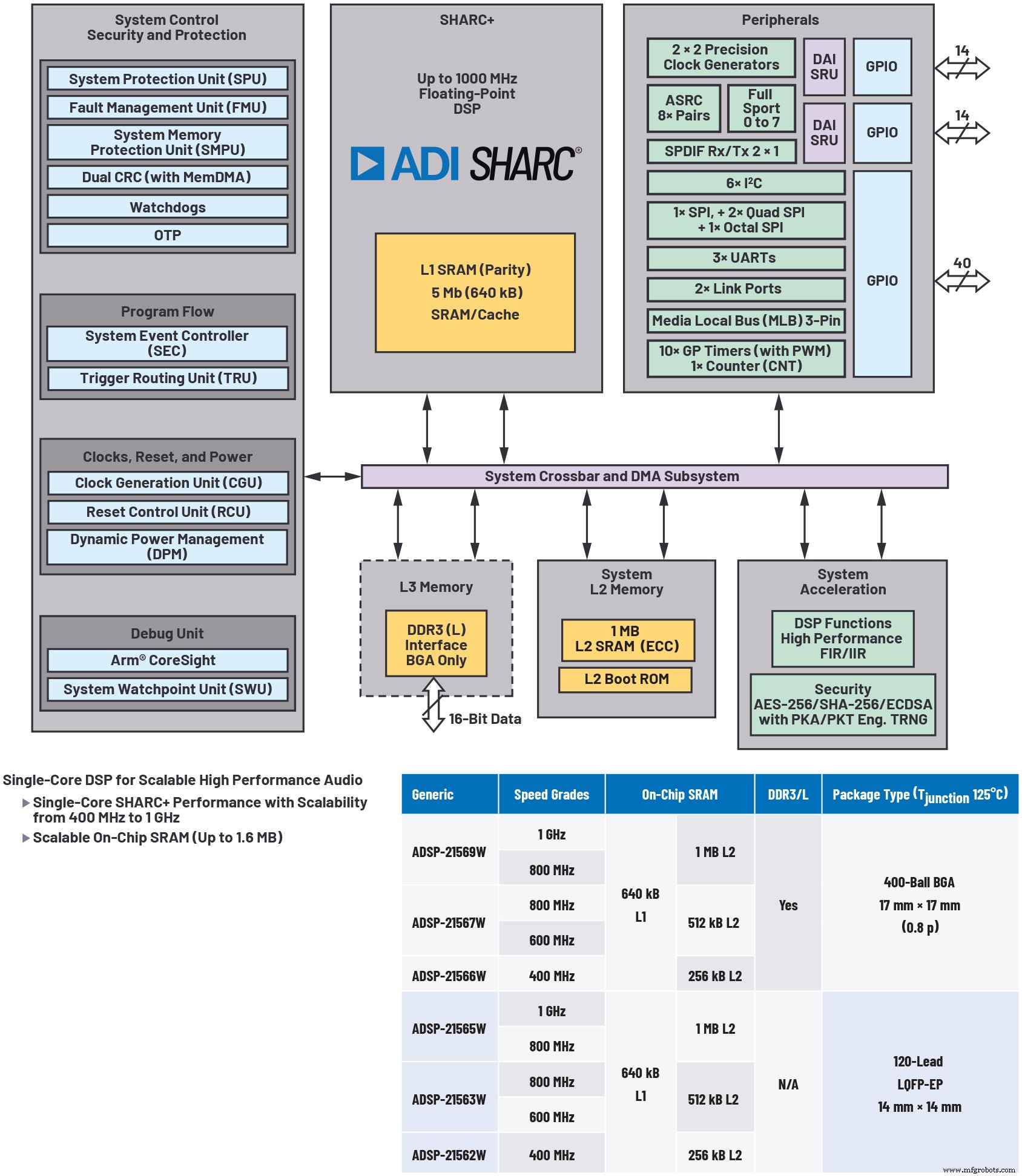

Utilizar um DSP de áudio separado como um coprocessador para um SoC ajuda a resolver o problema de escalabilidade de áudio, permite o design de sistema modular e otimiza o custo (consulte a Figura 2). O SoC pode se concentrar muito menos nas necessidades de processamento acústico em tempo real do sistema maior, em vez de transferir esse processamento para o DSP de áudio de baixa latência. Além disso, os DSPs de áudio que oferecem vários níveis diferentes de preço / desempenho / memória em um roteiro abrangente compatível com códigos e pinos oferecem flexibilidade máxima para designers de sistema para dimensionar corretamente a oferta de desempenho de áudio para uma determinada camada de produto.

clique para ver a imagem em tamanho real

Figura 2:ilustrativa de um processador de áudio altamente escalonável. Utilizar um processador de áudio separado, como o ADSP-2156x DSP mostrado aqui, ajuda a resolver o problema de escalabilidade de áudio, permite o design de sistema modular e otimiza o custo. (Fonte:Dispositivos analógicos)

Capacidade de atualização

À medida que as atualizações de firmware over-the-air se tornam mais comuns nos veículos de hoje, a capacidade de atualização para emitir patches críticos ou fornecer novas funcionalidades torna-se cada vez mais importante. Isso pode causar grandes problemas para um SoC devido ao aumento das dependências entre seus vários subsistemas. Primeiro, nos SoCs, vários segmentos de processamento e movimentação de dados estão disputando recursos. Isso aumenta a competição por MIPS do processador e memória quando novos recursos são adicionados, especialmente durante picos de atividade. Da perspectiva do áudio, as adições de recursos em outros domínios de controle do SoC podem ter um efeito imprevisível no desempenho acústico em tempo real. Um efeito colateral dessa situação é que a nova funcionalidade deve ser testada em todos os planos operacionais, resultando em uma miríade de permutações entre os vários modos operacionais dos subsistemas concorrentes. Assim, a verificação do software aumenta exponencialmente para cada pacote de atualização.

Visto de um ângulo diferente, pode-se dizer que as melhorias no desempenho de áudio do SoC dependem do SoC MIPS disponível, além dos roteiros de recursos para os outros subsistemas controlados pelo SoC.

Desenvolvimento e desempenho de algoritmos

Deve ficar claro que, quando se trata de desenvolver algoritmos acústicos em tempo real, os DSPs de áudio são desenvolvidos especificamente para a tarefa. Como um diferenciador significativo para SoCs, os DSPs de áudio autônomos podem oferecer ambientes de desenvolvimento gráfico que permitem que engenheiros com experiência mínima de codificação DSP adicionem processamento acústico de qualidade em seus projetos. Esse tipo de ferramenta pode diminuir os custos de desenvolvimento, reduzindo o tempo de desenvolvimento sem sacrificar a qualidade ou o desempenho.

Como exemplo, o ambiente de desenvolvimento de áudio gráfico SigmaStudio da ADI oferece uma ampla variedade de algoritmos de processamento de sinal integrados em uma interface de usuário gráfica intuitiva (GUI), permitindo a criação de fluxos de sinal de áudio complicados (ver Figura 3). Ele também suporta configuração gráfica A2B para transporte de áudio, ajudando muito a catalisar o desenvolvimento do sistema acústico em tempo real.

clique para ver a imagem em tamanho real

Figura 3:Ambientes de desenvolvimento gráfico de áudio, como o SigmaStudio da Analog Devices, fornecem acesso a uma ampla variedade de algoritmos de processamento de sinal integrados em uma interface gráfica de usuário (GUI) intuitiva, simplificando a criação de complicados fluxos de sinal de áudio. (Fonte:Dispositivos analógicos)

Recursos de hardware compatíveis com áudio

Além de uma arquitetura de núcleo de processador projetada especificamente para cálculos de ponto flutuante paralelo eficientes e acessos de dados, os DSPs de áudio costumam ter aceleradores multicanal dedicados para primitivos de áudio comuns, como transformadas rápidas de Fourier (FFTs), resposta de impulso finita e infinita (FIR e IIR ) filtragem e conversão assíncrona de taxa de amostragem (ASRC). Isso permite filtragem de áudio em tempo real, amostragem e conversão de domínio de frequência fora do núcleo da CPU, aumentando o desempenho efetivo do núcleo. Além disso, eles podem facilitar um modelo de programação flexível e amigável devido à sua arquitetura otimizada e recursos de gerenciamento de fluxo de dados.

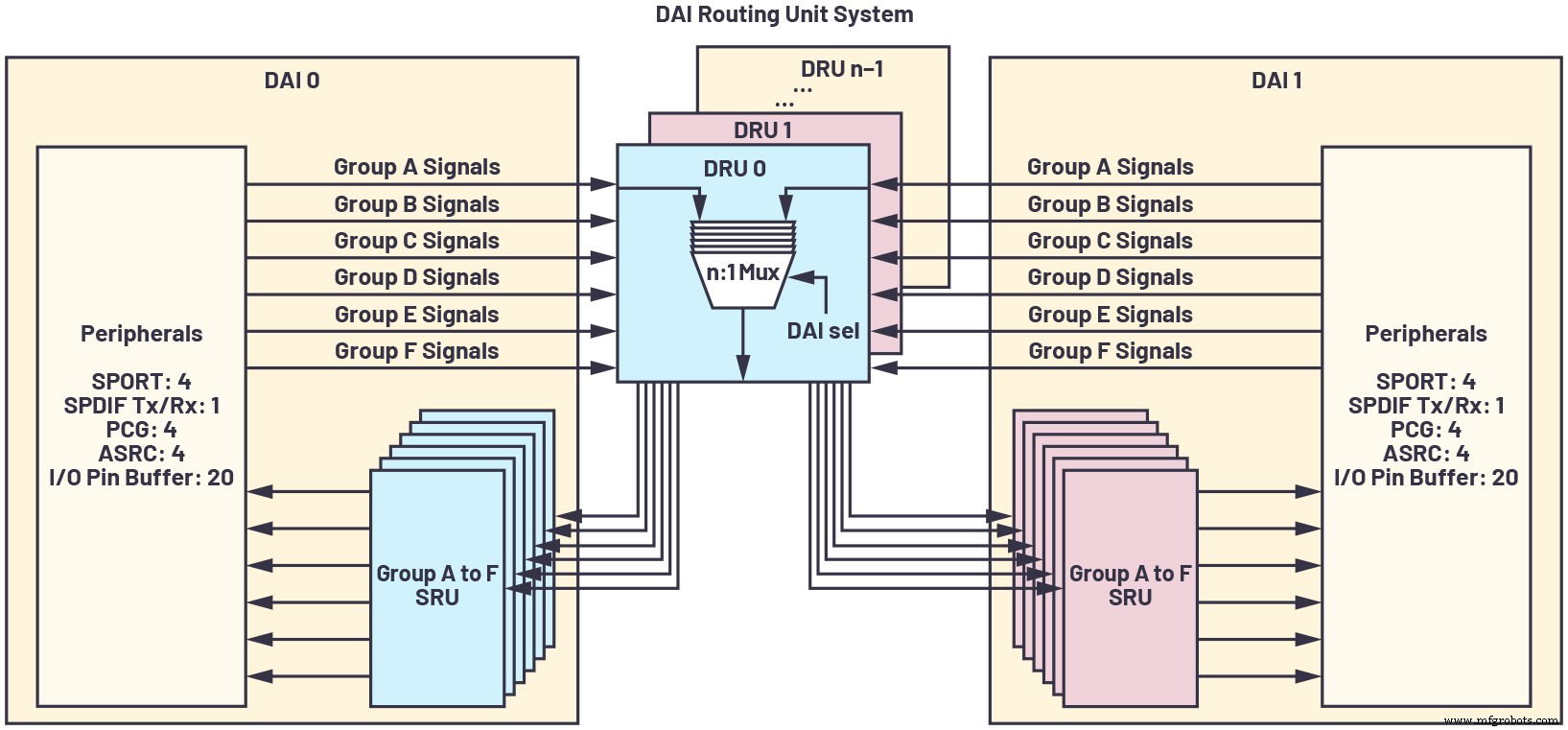

Por causa da proliferação de contagens de canais de áudio, fluxos de filtro, taxas de amostragem e similares, é importante ter uma interface de pinos configurável ao máximo que permite conversão de taxa de amostragem em linha, clock de precisão e portas seriais síncronas de alta velocidade para rotear dados de forma eficiente e evitar latência adicional ou lógica de interface externa. A interconexão de áudio digital (DAI) dos processadores da família SHARC da ADI ilustra essa capacidade, conforme mostrado na Figura 4.

clique para ver a imagem em tamanho real

Figura 4:Uma interconexão de áudio digital (DAI) é uma interface de pino configurável ao máximo que permite conversão de taxa de amostragem em linha, clock de precisão e portas seriais síncronas de alta velocidade para rotear dados de maneira eficiente e evitar latência adicional ou lógica de interface externa. (Fonte:Dispositivos analógicos)

Suporte ao Cliente

Um aspecto frequentemente esquecido do desenvolvimento com um processador embutido é o suporte ao cliente para o dispositivo.

Embora os fornecedores de SoC promovam a execução de algoritmos acústicos em seus produtos DSP integrados, isso acarreta várias desvantagens na prática. Por um lado, o suporte do fornecedor é geralmente mais complexo, uma vez que a experiência acústica não é normalmente o domínio do desenvolvimento de aplicativos SoC. Consequentemente, tende a haver suporte fraco para clientes que buscam desenvolver seus próprios algoritmos acústicos na tecnologia DSP on-chip do SoC. Em vez disso, o fornecedor pode oferecer algoritmos padrão e cobrar um NRE significativo para portar algoritmos acústicos para um ou mais núcleos do SoC. Mesmo assim, não há garantia de sucesso, especialmente se o fornecedor não oferece um software de estrutura maduro e de baixa latência. Finalmente, o ecossistema de terceiros para processamento acústico baseado em SoC tende a ser bastante frágil, uma vez que não é um foco do SoC, mas sim um recurso com suporte oportunista.

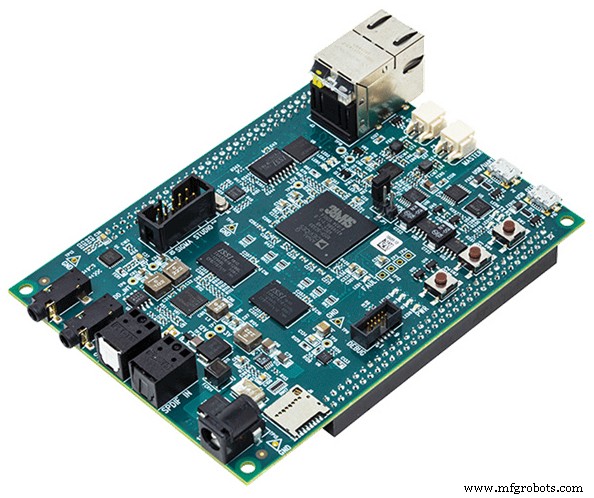

Um DSP de áudio desenvolvido para um propósito traz consigo um ecossistema muito mais forte para o desenvolvimento de sistemas acústicos complexos, de bibliotecas de algoritmo otimizadas e drivers de dispositivo a sistemas operacionais em tempo real e ferramentas de desenvolvimento fáceis de usar. Plataformas de referência focadas em áudio (como a plataforma de módulo de áudio SHARC da ADI, mostrada na Figura 5) que aceleram o tempo de lançamento no mercado são uma raridade para SoCs, mas bastante comuns no domínio DSP de áudio autônomo.

Figura 5:DSPs geralmente fornecem plataforma de desenvolvimento focada em áudio como o mostrado aqui módulo de áudio SHARC (SAM). (Fonte:Dispositivos analógicos)

O projeto de sistemas acústicos em tempo real envolve o planejamento estratégico deliberado dos recursos do sistema e não pode ser gerenciado simplesmente através da alocação de sobra de espaço de processamento em um SoC multitarefa. Em vez disso, um DSP de áudio autônomo otimizado para processamento de baixa latência provavelmente levará a uma maior robustez, menor tempo de desenvolvimento e escalabilidade ideal para acomodar as necessidades futuras do sistema e níveis de desempenho.

Referência

[1] Paul Beckmann. “Processadores SOC multicore:desempenho, análise e otimização.” 2017 AES International Conference on Automotive Audio, agosto de 2017.

David Katz tem 30 anos de experiência em design de sistemas analógicos, digitais e embarcados. Ele é diretor de arquitetura de sistemas para entretenimento informativo automotivo na Analog Devices, Inc. Ele publicou internacionalmente cerca de 100 artigos de processamento incorporado e apresentou vários artigos em conferências na área. Anteriormente, ele trabalhou na Motorola, Inc., como engenheiro de design sênior em grupos de modem a cabo e automação de fábrica. David possui tanto um B.S. e um M.Eng. em engenharia elétrica pela Cornell University. Ele pode ser contatado em [email protected].

David Katz tem 30 anos de experiência em design de sistemas analógicos, digitais e embarcados. Ele é diretor de arquitetura de sistemas para entretenimento informativo automotivo na Analog Devices, Inc. Ele publicou internacionalmente cerca de 100 artigos de processamento incorporado e apresentou vários artigos em conferências na área. Anteriormente, ele trabalhou na Motorola, Inc., como engenheiro de design sênior em grupos de modem a cabo e automação de fábrica. David possui tanto um B.S. e um M.Eng. em engenharia elétrica pela Cornell University. Ele pode ser contatado em [email protected]. Conteúdos Relacionados:

- Combinação de hardware e software para um áudio melhor

- Como os processadores de ponta de áudio permitem a integração de voz em dispositivos IoT

- AI encontra sua voz na cadeia de áudio

- As soluções ANC adaptáveis trazem recursos aprimorados de áudio

- Considerações de design para sistemas de comando de voz sempre ativos e com baixo consumo de energia

Para obter mais informações sobre o Embedded, assine o boletim informativo semanal da Embedded por e-mail.

Integrado

- ST:MCUs STM32WB dual-core wireless fornecem desempenho em tempo real de ultra-baixo consumo de energia

- Logic-X lança nova marca de produtos de processamento de sensores COTS

- Relógio em tempo real Maxim nanoPower estende a vida da bateria em wearables, POS

- A arquitetura do chip AI visa o processamento do gráfico

- Usar vários chips de inferência exige um planejamento cuidadoso

- Processador multicore integra unidade de processamento neural

- Relógios automotivos em tempo real apresentam ampla faixa de temperatura

- Seco:sistemas de processamento heterogêneos baseados em Xilinx Zynq Ultrascale + MPSoCs

- Planejamento de movimento em tempo real para carro autônomo em várias situações , sob ambiente urbano simulado

- Iniciativas digitais de chão de fábrica se beneficiam de um planejamento cuidadoso