Ferramentas de software migram código GPU para FPGAs para aplicativos AI

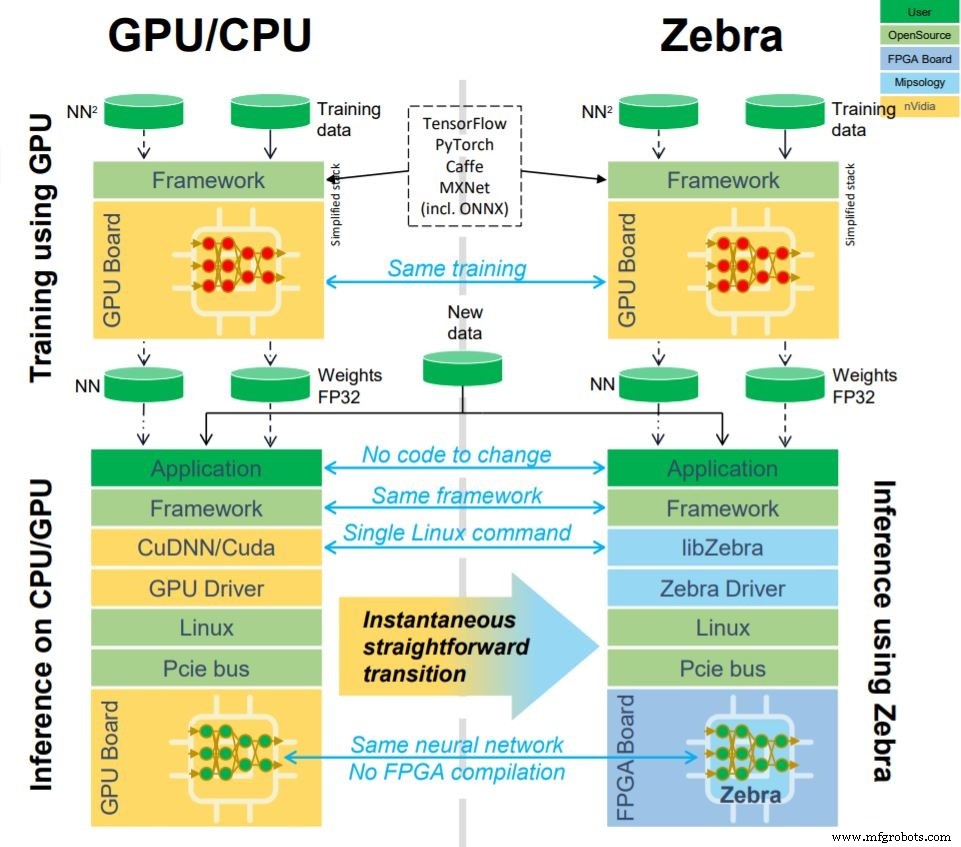

Inicialização do software AI A Mipsology está trabalhando com o Xilinx para permitir que os FPGAs substituam as GPUs em aplicativos do acelerador AI usando apenas um único comando adicional. O software de "esforço zero" da Mipsology, Zebra, converte o código da GPU para rodar no motor de computação AI da Mipsology em um FPGA sem qualquer alteração de código ou retreinamento necessário.

A Xilinx anunciou hoje que está enviando a Zebra com a última construção de seus cartões Alveo U50 para o data center. Zebra já suporta aceleração de inferência em outras placas Xilinx, incluindo Alveo U200 e Alveo U250.

A última construção da placa aceleradora de data center Alveo U50 da Xilinx agora vem com o software Zebra da Mipsology para conversão de código de IA de GPU para execução em FPGAs (Imagem:Xilinx)

“O nível de aceleração que a Zebra traz para nossos cartões Alveo deixa os aceleradores de CPU e GPU no chinelo”, disse Ramine Roane, vice-presidente de marketing da Xilinx. “Combinado com o Zebra, o Alveo U50 atende às necessidades de flexibilidade e desempenho das cargas de trabalho de IA e oferece vantagens de desempenho de alto rendimento e baixa latência para qualquer implantação.”

Plug-and-play

Os FPGAs historicamente eram vistos como notoriamente difíceis de programar para não especialistas, mas a Mipsology quer transformar os FPGAs em uma solução plug-and-play tão fácil de usar quanto uma CPU ou GPU. A ideia é tornar o mais fácil possível a mudança de outros tipos de aceleração para FPGA.

“A melhor maneira de ver [Mipsology] é fazendo o software que vai além dos FPGAs para torná-los transparentes da mesma forma que a Nvidia fez Cuda CuDNN para tornar a GPU completamente transparente para usuários de IA,” disse o CEO da Mipsology Ludovic Larzul , em entrevista ao EE Times .

Crucialmente, isso pode ser feito por não especialistas, sem profundo conhecimento de IA ou habilidades em FPGA, já que nenhum retreinamento de modelo é necessário para a transição.

“A facilidade de uso é muito importante, porque quando você olha para os projetos de IA das pessoas, muitas vezes elas não têm acesso à equipe de IA que projeta a rede neural”, disse Larzul. “Normalmente, se alguém instala um sistema de robôs ou um sistema de vigilância por vídeo ... eles têm outras equipes ou outras partes desenvolvendo as redes neurais e os treinando. E depois de obter [o modelo treinado], eles não querem mudá-lo porque não têm o conhecimento. ”

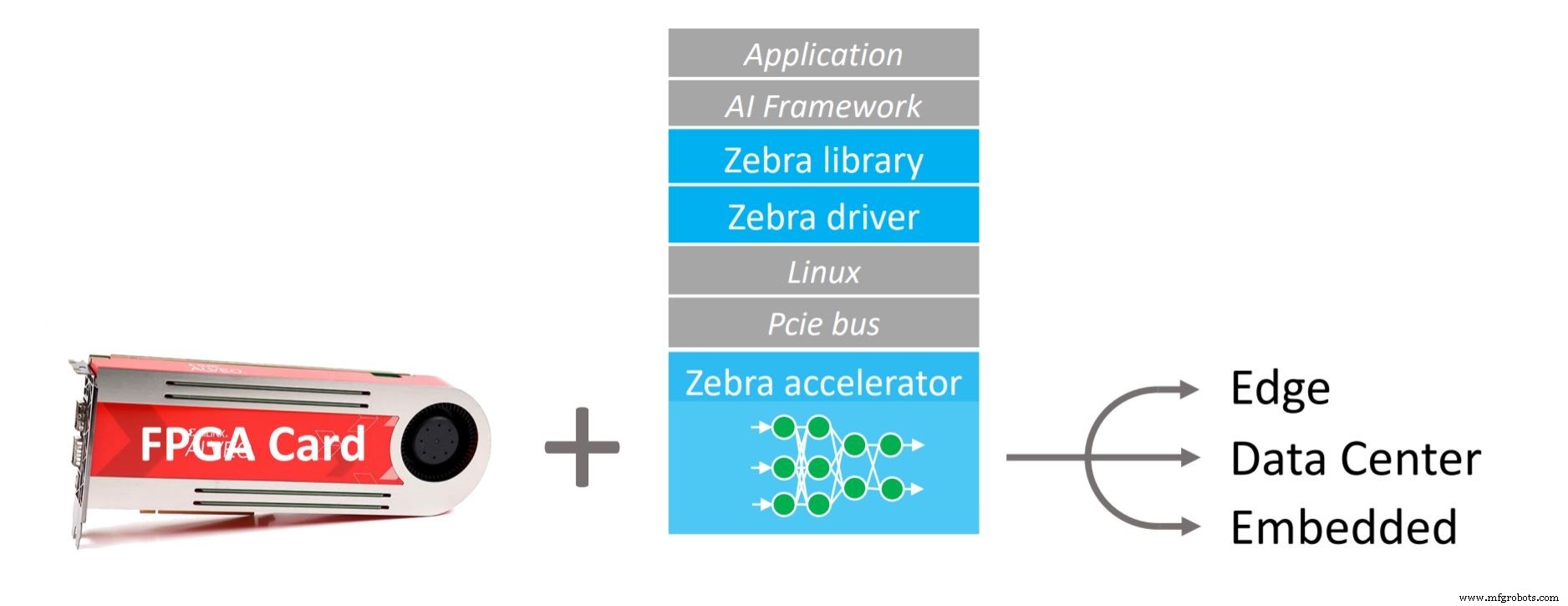

Pilha da Zebra. A tecnologia é aplicável em data centers, aplicativos de ponta e incorporados (Imagem:Mipsology)

Versus Vitis

Por que o Xilinx daria suporte a software de terceiros quando já tem uma solução abrangente destinada a tornar FPGAs acessíveis para cientistas de dados e desenvolvedores de software (ou seja, Vitis)?

“O argumento de venda em uma frase é:estamos nos saindo melhor”, disse Larzul. “Outra frase seria:nossos trabalhos.”

A Mipsology não usa nenhuma parte do Vitis ou se vincula a ele de forma alguma, nem usa XDNN, o mecanismo acelerador de rede neural da Xilinx. A Mipsology tem seu próprio mecanismo de computação dentro da Zebra, que oferece suporte aos modelos de rede neural convolucional (CNN) existentes dos clientes, ao contrário do XDNN, que Larzul disse ter suporte para muitas demos, mas é menos adequado para redes neurais personalizadas. Isso, disse ele, tornou "doloroso" colocar as redes personalizadas em funcionamento com o XDNN. Enquanto o XDNN pode competir em aplicativos onde não há ameaça de GPUs, o objetivo da Zebra é permitir que os FPGAs enfrentem as GPUs de frente com base no desempenho, custo e facilidade de uso.

Pilha da Zebra em detalhes. O objetivo é tornar os FPGAs uma troca mais simples de GPUs ou CPUs para aceleração de IA, ocultando o hardware o máximo possível (Imagem:Mipsologia)

A motivação da maioria dos clientes para mudar de soluções de GPU é o custo, disse Larzul.

“Eles querem reduzir o custo do hardware, mas não querem ter que redesenhar a rede neural”, disse ele. “Há um custo não recorrente [que é evitado] porque somos capazes de substituir GPUs de forma transparente e não há nenhum retreinamento ou modificação da rede neural.”

FPGAs também oferecem confiabilidade, em parte porque são menos agressivos em propriedades de silício e geralmente funcionam mais frios do que outros tipos de aceleradores, incluindo GPUs, de acordo com Larzul. Isso é especialmente importante no data center, onde os custos de manutenção de longo prazo são significativos.

“O custo total de propriedade não é apenas o preço do conselho”, disse Larzul. “Também existe o preço de garantir que o sistema esteja instalado e funcionando.”

A Zebra também tem como objetivo fazer os FPGAs competirem em desempenho. Embora os FPGAs normalmente ofereçam menos TOPS (operações tera por segundo) do que outros aceleradores, eles são capazes de usar esses TOPS com mais eficiência graças ao mecanismo de computação cuidadosamente projetado da Zebra, disse Larzul.

Ludovic Larzul (Imagem:Mipsologia)

“Isso é algo que a maioria das start-ups ASIC que aceleram a IA esqueceram - eles estão fazendo uma grande peça de silício, tentando embalar mais TOPS, mas não pensaram em como mapear sua rede para ser eficiente ”, Disse ele, observando que o mecanismo baseado em FPGA da Zebra é capaz de processar mais imagens por segundo do que uma GPU com 6x a quantidade de TOPS.

Como isso é feito? Embora Larzul não tenha dado detalhes exatos, ele disse que eles não dependem da poda, uma vez que a redução da precisão é muito grande para ser aceitável sem o retreinamento. Eles não usam quantização extrema (abaixo de 8 bits) pelo mesmo motivo.

O motor do Zebra acelera CNNs, que são usados principalmente por aplicativos de processamento de imagem e vídeo hoje, mas o Zebra também pode ser aplicado ao BERT (modelo de processamento de linguagem natural do Google), que usa conceitos matemáticos semelhantes. Futuras iterações do Zebra podem abranger outros tipos de rede neural, incluindo LSTM (memória de longo prazo) e RNNs (redes neurais recorrentes), mas isso é mais difícil de alcançar, pois os RNNs são matematicamente mais diversos.

Equipe de EVE

A Mipsology foi fundada em 2015, com cerca de 30 pessoas trabalhando em P&D na França e uma pequena equipe na Califórnia cobrindo principalmente o desenvolvimento de negócios. A empresa recebeu um financiamento total de US $ 7 milhões, dos quais US $ 2 milhões foram um prêmio de uma competição de inovação do governo francês em 2019.

A equipe principal da Mipsology é da EVE - uma empresa de emulação ASIC adquirida pela Synopsys em 2012 para seus produtos de verificação assistida por hardware ZeBu (Zero Bug), na época um concorrente da plataforma de verificação Palladium da Cadence. De acordo com Larzul, a tecnologia EVE foi usada por quase todas as principais empresas de ASIC para verificar ASICs durante o ciclo de design; esta tecnologia contou com milhares de FPGAs conectados para reproduzir o comportamento ASIC.

A Mipsology tem 12 patentes pendentes e trabalha em estreita colaboração com a Xilinx, além de ser compatível com cartões aceleradores de terceiros, como cartões Western Digital de fator de forma pequeno (SFF U.2) e cartões Advantech, como o Vega-4001.

>> Este artigo foi publicado originalmente em nosso site irmão, EE Times.

Integrado

- ST:kit de avaliação de elemento seguro com software pronto para uso para aplicativos de TI e IoT

- PPA para aplicativos de E-Mobility

- Aplicações ideais para atuadores pneumáticos

- 4 tipos de ferramentas para aplicações de mineração

- Aplicações típicas para freios de pinça

- Aplicativos militares para ligas de bronze

- Aplicativos para Alumínio Bronze C63200

- Para que serve o Monel?

- Ferramentas de corte para usinagem de precisão

- A importância da interoperabilidade em aplicativos de software 3D