Primeiros passos com a linguagem de descrição de hardware Verilog

Neste artigo, estudaremos a estrutura básica de um módulo Verilog, veja alguns exemplos de uso do tipo de dados “wire” Verilog e seus forma vetorial e brevemente mencionando algumas diferenças entre VHDL e Verilog.

Neste artigo, estudaremos a estrutura básica de um módulo Verilog, examinaremos alguns exemplos de uso do tipo de dados "fio" Verilog e sua forma vetorial e abordaremos brevemente algumas diferenças entre VHDL e Verilog.

Verilog e VHDL são duas linguagens comumente usadas para descrever circuitos digitais. AAC tem uma série de artigos técnicos discutindo os conceitos básicos de VHDL. Este artigo funciona como um ponto de partida para nossa série sobre Verilog.

Preciso de Verilog e VHDL?

Antes de iniciar nossa discussão, vamos abordar uma questão óbvia:realmente precisamos conhecer essas duas linguagens?

Tanto o Verilog quanto o VHDL são ferramentas poderosas que podem ser usadas para projetar um circuito digital complexo. Embora existam algumas diferenças entre esses dois HDLs, você é livre para escolher qualquer um para dominar e usar. No entanto, acredito que em algum momento, você se beneficiará por ter pelo menos um conhecimento básico dos dois idiomas. Às vezes, como designers, precisamos de um segmento de código de amostra para ter uma ideia sobre a codificação de um projeto. Navegamos na internet por horas e finalmente encontramos o que precisamos, mas não faz sentido para nós - está escrito em HDL que é completamente desconhecido para nós. Sem ter um conhecimento básico da linguagem, podemos não ser capazes de compreender totalmente as técnicas.

Evolução Verilog

O Verilog foi projetado no início de 1984 pela Gateway Design Automation (cerca de três anos depois que o VHDL foi iniciado pelo Departamento de Defesa dos Estados Unidos). Com o suporte do DoD, o VHDL se tornou um padrão IEEE em 1987. O Verilog não entrou em cena até 1995. Hoje, tanto o VHDL quanto o Verilog são HDLs populares e as ferramentas de design de FPGA geralmente oferecem suporte a ambas as linguagens.

A palavra “Verilog” é uma maleta das palavras "verificação" e "lógica" porque a linguagem foi sugerida pela primeira vez como uma ferramenta de simulação e verificação. Vamos começar com os conceitos e sintaxe do Verilog.

Exemplo 1

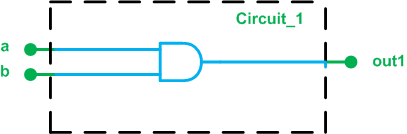

Como primeiro exemplo, vamos escrever o código Verilog para o circuito representado na Figura 1.

Figura 1. Circuit_1

Existem duas entradas e uma saída. As portas são todas com um pouco de largura. A funcionalidade do circuito é fazer o AND das duas entradas e colocar o resultado na porta out1.

Uma possível descrição Verilog para o módulo Circuit_1 é:

Linhas 1 e 8

Essas duas linhas usam as palavras-chave “módulo” e “módulo final” para especificar que todas as linhas intermediárias (linhas 2 a 7) descrevem um circuito denominado “Circuito_1”. Este nome é arbitrário e nos permite referir a este circuito mais tarde.

Linhas 2 a 6

Essas linhas especificam a interface de “Circuit_1” com seu ambiente circundante. As portas de entrada e saída são descritas usando as palavras-chave “entrada” e “saída”. Essas palavras-chave são seguidas por outra palavra-chave “fio” e, em seguida, o nome da porta (consulte a Figura 1). O que a palavra-chave “fio” especifica? “Fio” é um tipo de dados Verilog que representa um fio físico no projeto. Discutiremos os tipos de dados Verilog em mais detalhes em um artigo futuro, mas por enquanto, sabemos que haveria três fios chamados a, b e out1 em nosso módulo e, uma vez que são especificados na declaração de porta, eles correspondem a a interface do módulo.

Linha 7

Esta linha usa o operador bit a bit AND, ou seja, &, para descrever a funcionalidade do circuito. A palavra-chave “atribuir” coloca a &b na porta de saída out1. Este tipo de atribuição é denominado atribuição contínua. É chamado assim porque a atribuição está sempre ativa sempre que um operando no lado direito muda, a &b é avaliado e atribuído a out1. Podemos imaginar uma atribuição contínua como um circuito combinacional cuja saída é continuamente atualizada dependendo de suas entradas. Em nosso exemplo, este circuito combinacional é uma porta AND simples. Existem também atribuições procedimentais em Verilog HDL que serão discutidas em artigos futuros.

Agora, podemos usar um pacote de software como o Xilinx ISE para verificar o código acima. Você pode encontrar um tutorial deste software baseado em Verilog aqui (PDF).

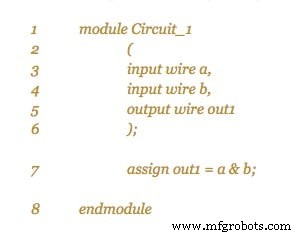

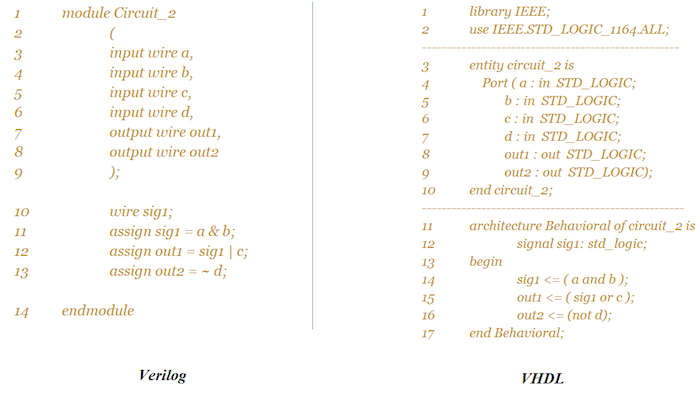

Comparando o Exemplo 1 com o Código VHDL

A Figura 2 abaixo mostra as descrições Verilog e VHDL para o módulo Circuit_1.

Figura 2. Comparação das descrições Verilog e VHDL para Circuit_1.

Como você pode ver, temos que incluir algumas bibliotecas ao codificar em VHDL. Essas bibliotecas fornecem a definição para os tipos de dados e operadores. Considerando o acréscimo dessas bibliotecas e o formato geral do VHDL, observamos que o código VHDL é mais detalhado. No entanto, esse detalhamento tem vantagens. Por exemplo, o recurso de gerenciamento de biblioteca de VHDL pode ser útil ao modelar sistemas de nível superior. Em artigos futuros, discutiremos ocasionalmente os prós e os contras desses dois HDLs.

Verilog tem um sistema de quatro valores

Existem quatro valores básicos usados na maioria dos tipos de dados Verilog. Os fios definidos na Listagem 1 podem assumir um dos seguintes valores:

- 0:para uma condição lógica baixa ou falsa

- 1:para uma condição lógica alta ou verdadeira

- z:para o estado de alta impedância (pode ser usado para descrever a saída de um buffer tri-state)

- x:para um valor irrelevante ou desconhecido (quando uma entrada não é inicializada ou duas ou mais saídas conflitantes estão conectadas).

O tipo de dados VHDL std_logic pode assumir nove valores diferentes, mas seus valores comumente usados são ‘0’, ‘1’, ‘Z’ e ‘-’ (‘-’ denota um não importa).

Exemplo 2

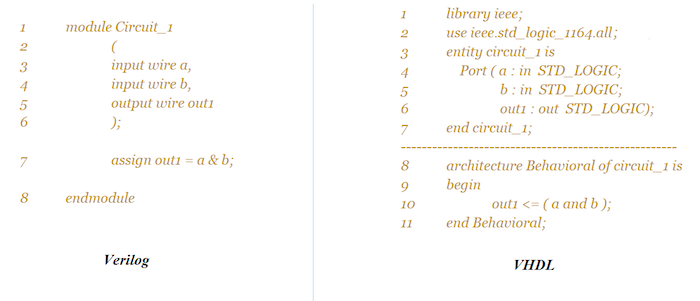

Como outro exemplo, vamos escrever o código Verilog para o circuito (que chamaremos de Circuit_2) mostrado na Figura 3.

Figura 3. Circuit_2

O seguinte código Verilog descreve este circuito:

Os elementos usados no código acima são semelhantes aos do Exemplo 1, exceto que um sinal interno é definido na linha 10 do código. A palavra-chave “fio” é usada para especificar o tipo de dados desta conexão. Conforme discutido acima, o tipo de dados “fio” seria traduzido em um fio físico no projeto.

O código acima também usa alguns novos operadores bit a bit Verilog:~ para NOT e | para operação OR. Outro operador bit a bit útil é ^ para a operação XOR. A Figura 4 mostra as descrições Verilog e VHDL para o módulo Circuit_2. Essas comparações podem ajudá-lo a ver as diferenças e semelhanças entre esses dois idiomas.

Figura 4. Comparação das descrições Verilog e VHDL para Circuit_2.

Exemplo 3

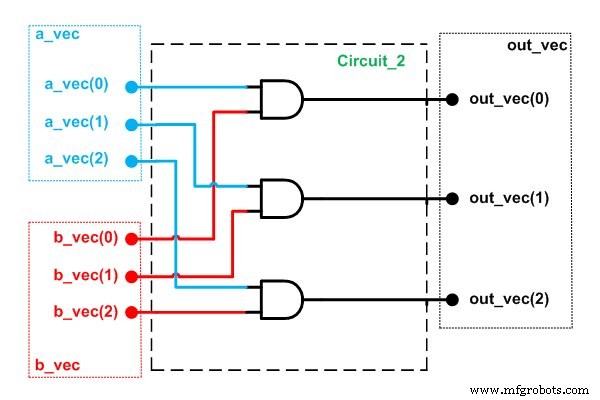

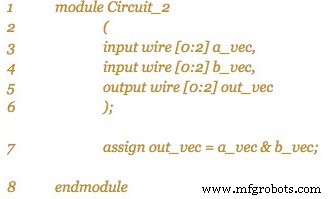

Para nosso terceiro e último exemplo, forneceremos o código Verilog para o esquema mostrado na Figura 5.

Figura 5. Esquema por exemplo 3.

Como você pode ver, há uma certa relação entre as portas de entrada azuis e as vermelhas:as entradas correspondentes são combinadas com o operador AND. O resultado é atribuído a uma porta de saída. Nesses casos, podemos agrupar os sinais e tratá-los como um vetor. Isso torna o código compacto e legível.

Usando o conceito de vetor em Verilog, podemos facilmente estender o código da Listagem 1 para descrever o circuito acima (consulte o código da Listagem 3 abaixo).

Observe que a faixa de índice dos vetores pode ser ascendente ([0:2] como usado acima) ou descendente ([2:0]). Embora o formato ascendente seja usado acima, geralmente é menos sujeito a erros usar o formato descendente. Isso se deve ao fato de que o estilo descendente corresponde à nossa percepção de que a posição mais à esquerda de um número binário tem o índice mais alto. Observe que os vetores também são usados em VHDL.

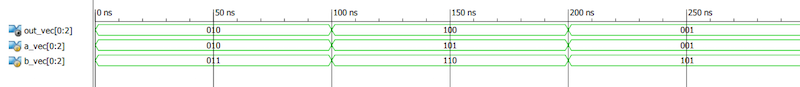

A Figura 6 abaixo mostra uma simulação ISE do código na Listagem 3.

Figura 6. Simulação ISE do código do Exemplo 3.

Neste artigo, discutimos que é uma boa ideia aprender VHDL e Verilog, estudamos a estrutura básica de um módulo Verilog e nos familiarizamos com o tipo de dados "fio" Verilog e sua forma vetorial. Também mencionamos brevemente algumas diferenças entre VHDL e Verilog. O próximo artigo em nossa série Verilog discutirá o projeto de circuitos combinacionais em Verilog.

Integrado

- Contêineres prontos para código:Introdução às ferramentas de automação de processos na nuvem

- Introdução à impressão 3D em cerâmica

- Introdução ao TJBot

- Introdução ao RAK 831 Lora Gateway e RPi3

- Primeiros passos com o RAK831 LoRa Gateway e RPi3

- Como começar com a inferência de IA na borda

- Introdução ao Grupo Eagle:o que você precisa saber

- Introdução ao My.Cat.com

- Node-RED e introdução ao Docker

- Começando com Go no PLCnext