Introdução ao Verilog

Verilog é um tipo de linguagem de descrição de hardware (HDL). Verilog é uma das duas linguagens usadas pela educação e negócios para projetar FPGAs e ASICs. Se você não está familiarizado com o funcionamento de FPGAs e ASICs, leia esta página para obter uma introdução aos FPGAs e ASICs. Verilog e VHDL são os dois HDLs mais populares usados. Comparado às linguagens de software tradicionais, como Java ou C, o Verilog funciona de maneira muito diferente. Vamos começar olhando para um exemplo simples.

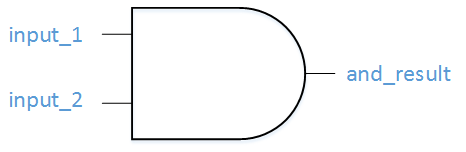

Primeiro vamos criar um arquivo Verilog que descreve um E Portão. Para relembrar, um And Gate simples tem duas entradas e uma saída. A saída é igual a 1 somente quando ambas as entradas são iguais a 1. Abaixo está uma imagem do And Gate que descreveremos com Verilog.

An And Gate

An And Gate Vamos lá! Uma unidade fundamental do Verilog é chamada de fio. Por enquanto vamos supor que um fio só pode ser 0 ou 1. Aqui está uma lógica básica de fio:

wire and_temp; assign and_temp = input_1 & input_2;

Estamos criando um fio chamado and_temp na primeira linha de código. Na segunda linha do código, estamos pegando o fio que criamos e estamos atribuindo o fio. Para atribuí-lo, estamos usando a função booleana AND que em Verilog é o E comercial (&). Se você descrevesse o código mostrado acima, poderia dizer:"O sinal and_temp obtém input_1 E-ed com input_2."

Input_1 e Input_2 são entradas para este código Verilog. Vamos mostrar a lista completa de entradas e saídas. Isso é feito no módulo definição. Module é uma palavra-chave reservada em Verilog que mostra a criação de um bloco de código com entradas e saídas definidas.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

Este é o seu módulo básico. Ele define nosso módulo chamado example_and_gate e 3 sinais, 2 entradas e 1 saída. Vamos juntar tudo para terminar o arquivo. A única coisa que está faltando é a atribuição da saída and_result . Uma outra nota, // em Verilog é usada para um comentário.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

Parabéns! Você criou seu primeiro arquivo Verilog.

Parece que você teve que escrever muito código apenas para criar um portão estúpido? Em primeiro lugar, e os portões não são estúpidos. Em segundo lugar, você está correto, os HDLs precisam de muito código para realizar tarefas relativamente simples. Você pode se confortar com o fato de que o Verilog é pelo menos menos detalhado que o VHDL. Acostume-se com o fato de que fazer algo que era muito fácil no software levará muito mais tempo em um HDL como Verilog ou VHDL. Mas basta pedir a um cara de software para tentar gerar uma imagem para um monitor VGA que exibe o Jogo da Vida de Conway e ver sua cabeça girar com espanto! By the way, esse vídeo é criado com um FPGA. Você será capaz de fazer isso em breve!

Verilog