Variáveis - Exemplo de VHDL

As variáveis em VHDL agem de forma semelhante às variáveis em C. Seu valor é válido no local exato do código onde a variável é modificada. Portanto, se um sinal usa o valor da variável antes a atribuição, ela terá o valor da variável antiga. Se um sinal usa o valor da variável depois a atribuição terá o novo valor da variável.

Regras de variáveis:

- Variáveis só podem ser usadas dentro de processos

- Qualquer variável criada em um processo não pode ser usada em outro processo

- As variáveis precisam ser definidas após a palavra-chave process mas antes da palavra-chave começar

- As variáveis são atribuídas usando o := símbolo de atribuição

- As variáveis atribuídas imediatamente assumem o valor da atribuição

A coisa mais importante a entender é que as variáveis assumem imediatamente o valor de sua atribuição. Aqui está um exemplo que mostra uma maneira útil de usar variáveis:armazenando dados para uso temporário . Ele usa uma instrução case e o operador de concatenação e comercial (&).

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

No exemplo anterior, concatenamos os dois sinais para que pudessem ser usados na instrução case. A variável v_Choices ficou imediatamente disponível para uso assim que foi atribuída. Vejamos outro exemplo. O exemplo abaixo é mais abrangente e demonstra como as variáveis imediatamente assumem o valor de sua atribuição. Os sinais r_Var_Copy1 e r_Var_Copy2 parecem ser os mesmos, mas r_Var_Copy2 nunca consegue chegar a 5 antes de ser reiniciado.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

Para simular nosso projeto, precisamos criar um testbench. Além disso, as variáveis podem ser um pouco complicadas de serem exibidas na simulação. Se você estiver usando o Modelsim, leia mais sobre como ver suas variáveis na janela de forma de onda do Modelsim.

Banco de teste:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

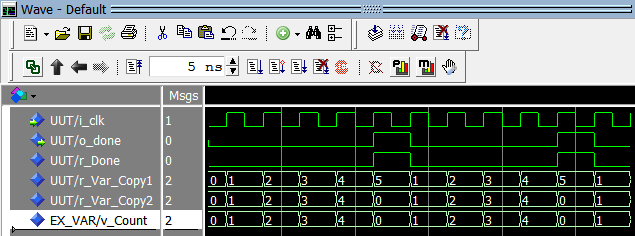

Exemplo de variáveis Forma de onda de bancada de teste

Exemplo de variáveis Forma de onda de bancada de teste O exemplo acima demonstra como as variáveis agem de forma diferente dos sinais. Os sinais r_Var_Copy1 e r_Var_Copy2 parecem ser os mesmos, mas r_Var_Copy2 nunca consegue chegar a 5 antes de ser reiniciado.

VHDL

- Declaração de Procedimento - Exemplo de VHDL

- Registros - Exemplo de VHDL

- Opções de análise

- Variáveis C# e tipos de dados (primitivos)

- Variáveis, literais e constantes de C++

- Variáveis C, Constantes e Literais

- Classe de armazenamento C

- Strings em C:como declarar variável, inicializar, imprimir, exemplo

- Java - Tipos de Variáveis

- C - Variáveis