A cadência acelera a verificação de SoC de bilhões de portas

A Cadence Design Systems lançou sua próxima geração de sistemas de emulação e prototipagem que, segundo ela, oferecem a depuração de hardware pré-silício mais rápida e de mais alto desempenho e validação de software para verificação de designs de sistema em chip (SoC) de bilhões de portas.

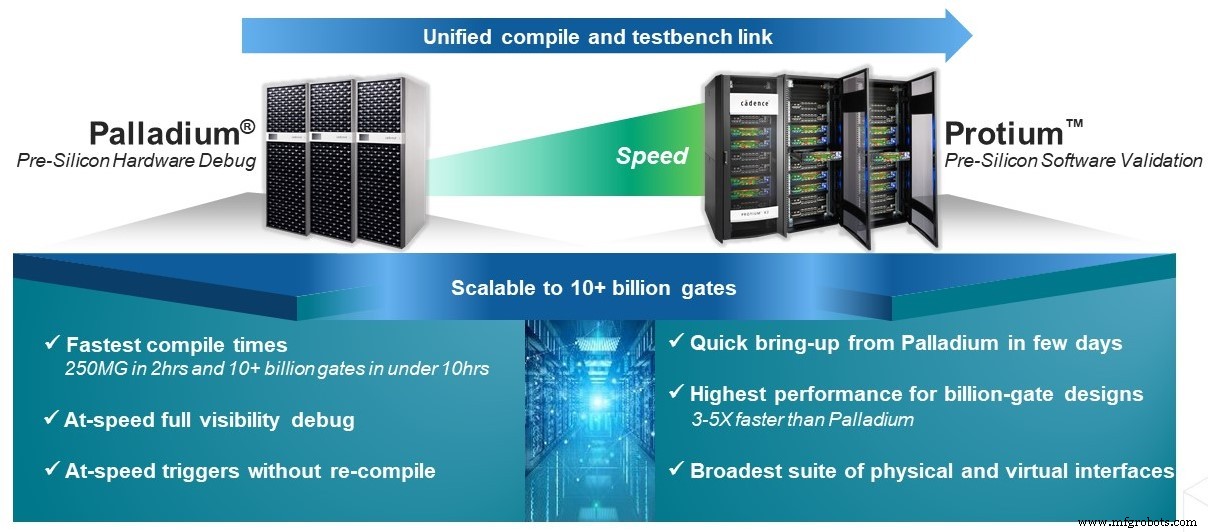

Com uma interface de compilador unificada, bem como interfaces de depuração comuns e conteúdo de teste, os novos sistemas de emulação empresarial Palladium Z2 e prototipagem empresarial Protium X2 fornecem aos clientes 2X capacidade e 1,5X melhorias de desempenho em relação a seus predecessores, permitindo que mais ciclos de validação sejam executados em chips maiores em menos tempo. Cadence disse que ambos os sistemas também oferecem uma tecnologia inovadora de compilação modular, capaz de compilar 10 bilhões de portas em menos de 10 horas no sistema Palladium Z2 e em menos de 24 horas no sistema Protium X2.

Uma chave para a combinação Palladium Z2 / Protium X2, que faz parte do amplo conjunto de verificação Cadence, incluindo aplicativos de verificação inteligente, é a interface do compilador unificado, o que significa que um design que compila para Palladium irá compilar e rodar no Protium. Com o fluxo perfeitamente integrado, depuração unificada, interfaces virtuais e físicas comuns e conteúdo de teste em todos os sistemas, os dois sistemas oferecem migração de design e testes rápidos da emulação à prototipagem. A capacidade escalonável significa que eles são projetados para enfrentar os desafios enfrentados por aqueles que projetam para os aplicativos mais avançados, incluindo projetos de computação móvel, de consumo e hiperescala.

Paul Cunningham, da Cadence, disse:“A verificação pré-silício do design SoC avançado requer uma solução com capacidade de vários bilhões de portas que ofereça o mais alto desempenho e depuração rápida e previsível.” O vice-presidente sênior e gerente geral do grupo de sistema e verificação acrescentou:"Nossa nova dupla dinâmica atende a esses requisitos com dois sistemas totalmente integrados, emulação Palladium Z2 otimizada para depuração de hardware rápida e previsível e prototipagem Protium X2 otimizada para o mais alto desempenho multi-bilhões- validação de software de portão. Estamos entusiasmados com o forte interesse do cliente e esperamos fazer uma parceria com eles para alavancar esses novos sistemas a fim de obter o maior rendimento de verificação em seus projetos ”.

Os primeiros clientes comentaram sobre os benefícios da taxa de transferência de verificação front-end comum. Na Nvidia, o diretor sênior de engenharia de hardware, Narendra Konda, disse:“A complexidade de nossos gráficos de ponta e designs de hiperescala aumenta a cada geração, enquanto nossos cronogramas de lançamento no mercado se apertam. Usando o fluxo front-end comum nos sistemas Cadence Palladium Z2 e Protium X2, estamos otimizando a distribuição da carga de trabalho entre a verificação, a validação e o desenvolvimento do software pré-silício. Com o dobro da capacidade utilizável, rendimento 50 por cento maior e resposta mais rápida do compilador modular, podemos validar nossos designs de GPU e SoC mais sofisticados de forma abrangente e dentro do cronograma. ”

Enquanto isso, na Arm, o diretor sênior de serviços de design, Tran Nguyen, disse:“As melhores emulações da classe são a chave para nosso sucesso, e a Arm usa a emulação extensivamente junto com a simulação em servidores baseados em Arm para obter o maior rendimento de verificação. Com o novo sistema Cadence Palladium Z2, vimos uma melhoria de até 50% no desempenho e uma melhoria 2X na capacidade de nossos projetos mais recentes, fornecendo-nos os poderosos recursos de pré-silício necessários para verificar nosso IP e produtos de próxima geração ”.

Como seus predecessores, Palladium Z2 e Protium X2 são construídos com uma configuração de rack padrão e devem ser instalados dentro de um data center e acessados da mesa dos engenheiros. Ambos podem lidar com muitos projetos simultaneamente, dependendo de quanta capacidade os projetos individuais realmente requerem. A granularidade que pode ser compartilhada está no chip individual dentro do sistema, e ambos os sistemas são escalonados para que cada chip individual possa ser usado em paralelo para um design diferente:

- O Palladium Z2 pode ser escalado a partir de um chip com 8 milhões de portas e pode ter até 144 trabalhos simultâneos por rack. Ou pode ser dimensionado para 18,4 bilhões de portas por rack, se todo o rack for usado para um único projeto. Além disso, até 12 racks podem ser usados para um único design e escala até 18,4 bilhões de portas.

- Um rack completo de Protium X2 contém 60 FPGAs e temos clientes que executam 60 trabalhos em paralelo. Uma vez que um único FPGA no Protium X2 comporta cerca de 40 milhões de portas, estes não são projetos pequenos. Todo o rack pode ser usado para um único projeto de 2,4 bilhões de portas. Ou, como no Palladium Z2, um design grande pode ser dimensionado em vários racks.

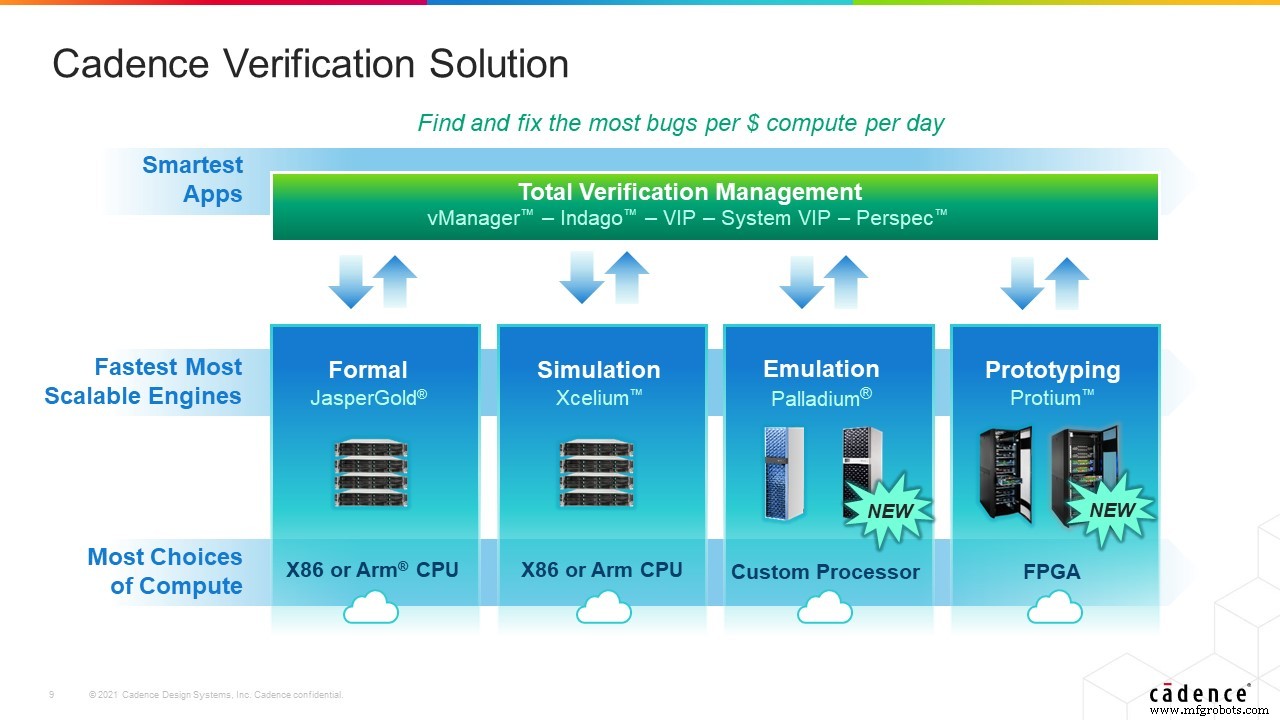

O fluxo completo de verificação Cadence, incluindo emulação Palladium Z2, prototipagem Protium X2, simulação lógica Xcelium, a plataforma de verificação formal JasperGold e o conjunto Cadence de aplicativos de verificação inteligente, oferece a maior taxa de verificação de bugs por dólar por dia, de acordo com a empresa.

Integrado

- Sistemas de numeração

- Universalidade do portal

- Sistemas de sinais atuais

- Por que um desenvolvedor bare-metal mudou para sistemas operacionais

- Cadence anuncia o programa Cloud Passport Partner

- SoC aumenta o desempenho dos wearables

- A placa do sensor inteligente acelera o desenvolvimento de IA de borda

- Modelagem de nível de portão

- Hitachi adquire o integrador de sistemas robóticos JR Automation por US$ 1,4 bilhão

- ABB reivindica 20% de participação no mercado de sistemas de controle distribuído de US$ 14 bilhões