Simplificando as cadeias de sinais de aquisição de dados AC e DC

Fenômenos de amostragem em conversores analógico-digital (ADCs) induzem os problemas de aliasing e retrocesso capacitivo e, para resolver esses problemas, os projetistas usam filtros e amplificadores de direção que apresentam seus próprios conjuntos de desafios. Isso torna a obtenção de desempenho CC e CA de precisão em áreas de aplicação de largura de banda média um desafio e os projetistas acabam trocando os objetivos do sistema para isso.

Este artigo descreve ADCs sigma-delta (∑-Δ) de tempo contínuo que inerentemente e dramaticamente resolvem os problemas de amostragem simplificando as cadeias de sinal. Eles eliminam a necessidade de filtros e buffers de suavização e resolvem erros de deslocamento da cadeia de sinal e problemas de desvio associados aos componentes adicionais. Esses benefícios reduzem o tamanho da solução, facilitam o design da solução e melhoram a correspondência de fase e a latência geral do sistema. Este artigo também faz uma comparação com conversores de tempo discreto e destaca os benefícios do sistema, bem como as restrições do uso de ADCs sigma-delta de tempo contínuo.

Fundamentos de amostragem

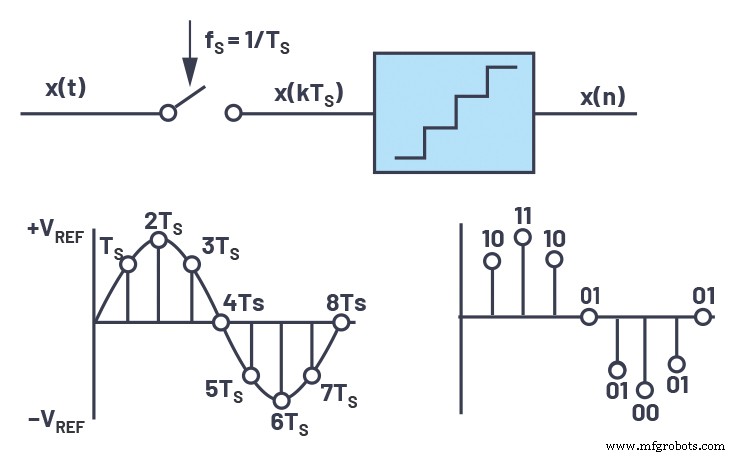

A digitalização de dados envolve os dois processos fundamentais de amostragem e quantização, conforme mostrado na Figura 1. A amostragem é a primeira etapa em que um sinal analógico variável de tempo contínuo x (t) é convertido em um sinal de tempo discreto x (n) usando amostragem frequência fS. O resultado é igualmente separado por um período de 1 / TS (fS =1 / TS).

clique para ampliar a imagem

Figura 1. Amostragem de dados. (Fonte:Dispositivos analógicos)

A segunda etapa é a quantização, que aproxima o valor dessas amostras de tempo discreto a um dos valores finitos possíveis e é representada em código digital, conforme mostrado na Figura 1. Essa quantização para um conjunto finito de valores leva a um erro na digitalização denominado ruído de quantização.

O processo de amostragem também resulta em aliasing, no qual vemos o retorno dos sinais de entrada e seus harmônicos em torno da amostra e mantém a frequência do clock. O critério de Nyquist requer que a frequência de amostragem seja pelo menos duas vezes a frequência mais alta contida no sinal. Se a frequência de amostragem for menor que o dobro da frequência máxima do sinal analógico, ocorrerá um fenômeno conhecido como aliasing.

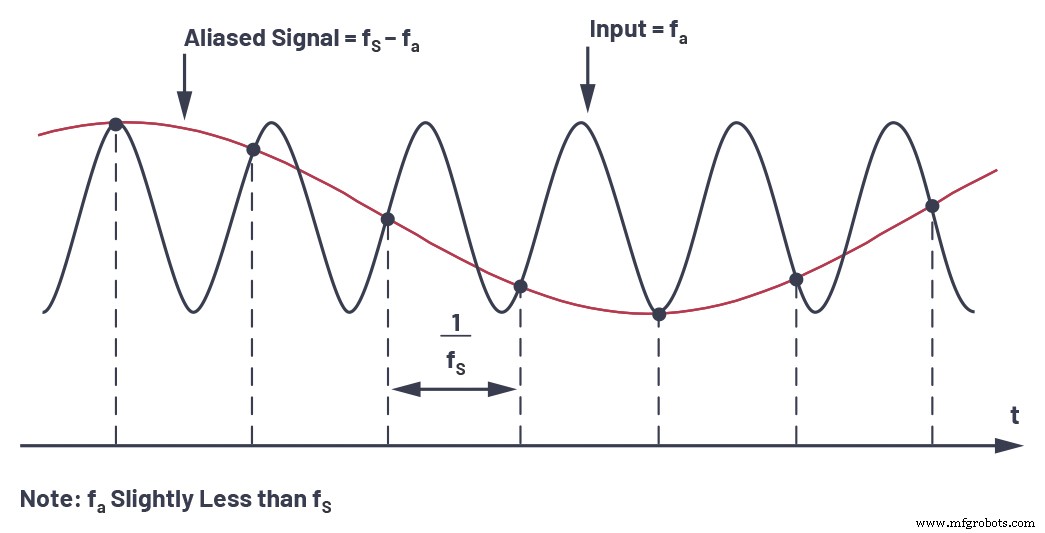

A fim de compreender as implicações do aliasing no domínio do tempo e da frequência, primeiro considere o caso de uma representação no domínio do tempo de uma onda senoidal de tom único amostrada como mostrado na Figura 2. Neste exemplo, a frequência de amostragem, fS, não é pelo menos 2fa, mas apenas um pouco mais do que a frequência de entrada analógica, fa, deixando de atender ao critério de Nyquist. Observe que o padrão das amostras reais produz uma onda senoidal com alternância em uma frequência inferior igual a fS - fa.

clique para ampliar a imagem

Figura 2. Aliasing:representação no domínio do tempo. (Fonte:Dispositivos analógicos)

clique para ampliar a imagem

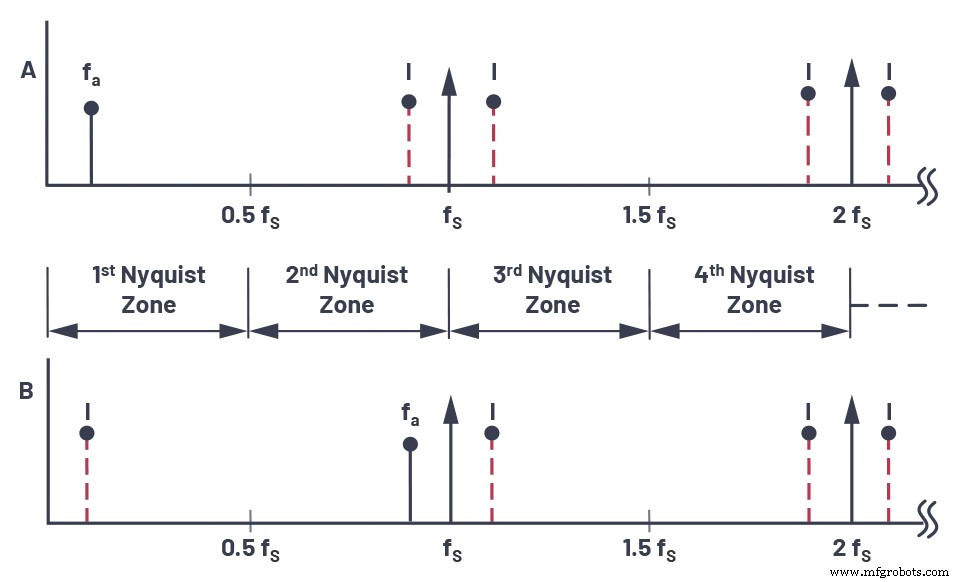

Figura 3. Aliasing:representação no domínio da frequência. (Fonte:Dispositivos analógicos)

A representação do domínio da frequência correspondente deste cenário é mostrada na Figura 3.

A largura de banda de Nyquist é definida como o espectro de frequência de dc a fS / 2. O espectro de frequência é dividido em um número infinito de zonas de Nyquist, cada uma com uma largura igual a 0,5fS. Na prática, o amostrador ideal é substituído por um ADC seguido por um processador FFT. O processador FFT fornece apenas uma saída DC para fS / 2; ou seja, os sinais ou apelidos que aparecem na primeira zona de Nyquist.

Considere o caso de uma onda senoidal de frequência única fa amostrada em uma frequência fS por um amostrador de impulso ideal (veja a Figura 1). Suponha também que fS> 2fa. A saída de domínio de frequência do amostrador mostra aliases, ou imagens, do sinal original em torno de cada múltiplo de fS; ou seja, em frequências iguais a | ± KfS ± fa |, K =1, 2, 3, 4 e assim por diante.

Agora considere o caso de um sinal que está fora da primeira zona de Nyquist na Figura 3. A frequência do sinal é apenas ligeiramente menor do que a frequência de amostragem, correspondendo à condição mostrada na representação do domínio do tempo na Figura 2. Observe que, embora o o sinal está fora da primeira zona de Nyquist, sua imagem (ou apelido), fS - fa, está dentro. Voltando à Figura 3, é claro que se um sinal indesejado aparecer em qualquer uma das frequências de imagem de fa, ele também ocorrerá em fa, produzindo assim um componente de frequência espúrio na primeira zona de Nyquist.

Combatendo desafios para desempenho de precisão

Para aplicações de alto desempenho, os projetistas de sistema precisam combater o ruído de quantização, aliasing e problemas de amostragem de entrada do capacitor comutado resultantes do processo de amostragem. Ambos os tipos de ADCs de precisão - isto é, registros de aproximação sucessivos (SARs) e ADCs sigma-delta, disponíveis na indústria - são projetados usando técnicas de amostragem baseadas em capacitor chaveado.

Ruído de quantização

Em um ADC Nyquist ideal, o tamanho LSB do ADC determinará o ruído de quantização que é adicionado à entrada, enquanto faz a conversão analógica para digital. Este ruído de quantização é espalhado pela largura de banda de fS / 2. Para combater o ruído de quantização, a primeira técnica é a sobreamostragem, que faz a amostragem do sinal de entrada a uma taxa muito mais alta do que a frequência de Nyquist para aumentar a relação sinal-ruído (SNR) e a resolução (ENOB). Na sobreamostragem, a frequência de amostragem é escolhida como N vezes a frequência de Nyquist (2 × fIN) e, como resultado, o mesmo ruído de quantização deve agora se espalhar por N vezes a frequência de Nyquist. Isso também relaxa os requisitos do filtro anti-serrilhamento. A razão de sobreamostragem (OSR) é definida como fS / 2fIN, onde fIN é o sinal BW de interesse. Como orientação geral, a sobreamostragem do ADC por um fator de quatro fornece um bit adicional de resolução ou um aumento de 6 dB na faixa dinâmica. O aumento da taxa de sobreamostragem resulta em ruído geral reduzido e a melhoria da faixa dinâmica (DR) devido à sobreamostragem é ΔDR =10log10 OSR em dB.

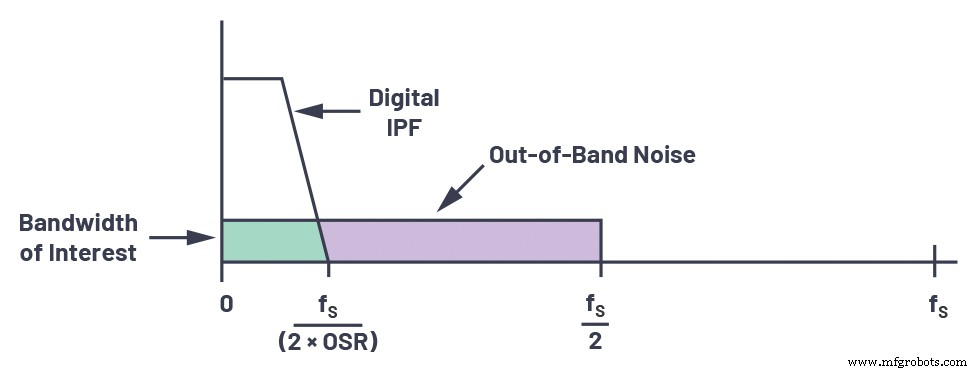

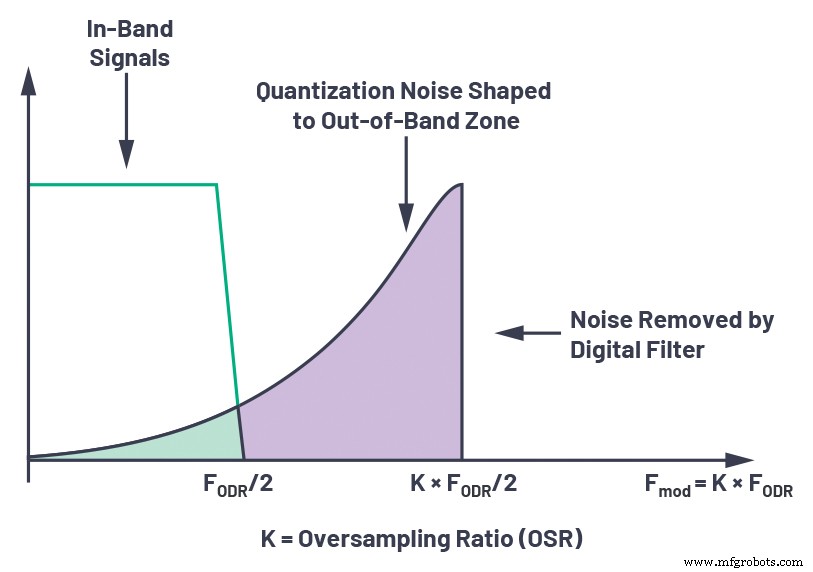

A sobreamostragem é inerentemente usada e implementada junto com um filtro digital integrado e funcionalidade de decimação. O modulador de sobreamostragem básico no ADC sigma-delta molda o ruído de quantização de forma que a maior parte dele ocorra fora da largura de banda de interesse, resultando em uma faixa dinâmica geral aumentada em baixas frequências, como mostrado na Figura 4. O filtro passa-baixo digital (LPF ) então remove o ruído de quantização fora da largura de banda de interesse e o dizimador reduz a taxa de dados de saída de volta à taxa de Nyquist.

clique para ampliar a imagem

Figura 4. Um exemplo de sobreamostragem. (Fonte:Dispositivos analógicos)

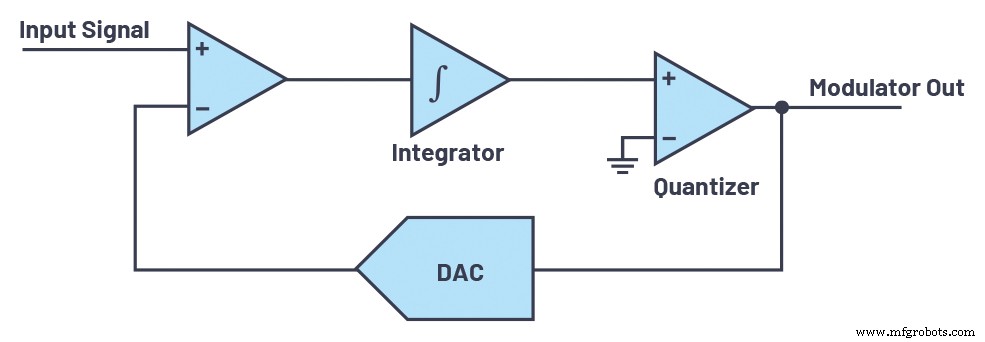

A modelagem de ruído é a outra técnica para reduzir o ruído de quantização. Em ADCs sigma-delta, um quantizador de baixa resolução (um bit a cinco bits) é usado dentro de um loop após o filtro de loop. Um DAC é usado como feedback para subtrair o sinal quantizado da entrada, conforme mostrado na Figura 5.

clique para ampliar a imagem

Figura 5. Modelagem de ruído. (Fonte:Dispositivos analógicos)

O integrador continuará somando o erro de quantização resultando na formação do ruído de quantização para frequências mais altas, que então podem ser filtradas usando um filtro digital. A Figura 6 ilustra a densidade espectral de potência (PSD) da saída x [n] de um ADC sigma-delta típico. A inclinação de modelagem de ruído depende da ordem do filtro de loop H (z) (veja a Figura 11) e é (20 × n) dB / década, onde n é a ordem do filtro de loop. O ADC sigma-delta atinge uma alta resolução dentro da banda por uma combinação de modelagem de ruído e sobreamostragem. A largura de banda dentro da banda é igual a fODR / 2 (ODR significa taxa de dados de saída). Uma resolução mais alta pode ser obtida aumentando a ordem do filtro de loop ou aumentando a taxa de sobreamostragem.

clique para ampliar a imagem

Figura 6. Gráfico de superamostragem e modelagem de ruído. (Fonte:Dispositivos analógicos)

Aliasing

Para combater o aliasing em aplicativos de alto desempenho, filtros antialiasing de ordem superior são usados para evitar qualquer quantidade de foldback. Um filtro anti-serrilhamento é um filtro passa-baixa que limita a banda do sinal de entrada e garante que não haja nenhum componente de frequência no sinal além da largura de banda de interesse que pode dobrar. O desempenho do filtro dependerá de quão próximo o sinal fora de banda está de fS / 2 e da quantidade de atenuação necessária.

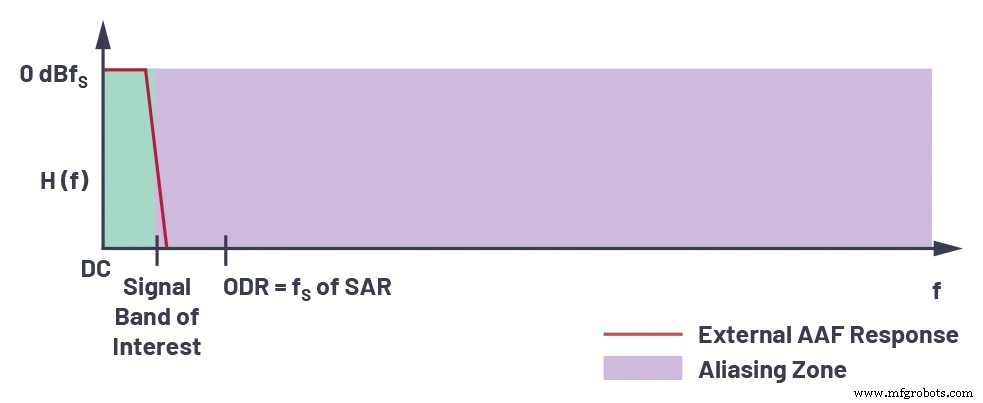

Para ADCs SAR, a lacuna entre o sinal de entrada BW e a frequência de amostragem não é grande, portanto, precisamos de um filtro de ordem superior que exige um projeto de filtro complexo de ordem superior com mais potência e mais distorção. Por exemplo, se um SAR com velocidade de amostragem de 200 kSPS tiver um BW de entrada de 100 kHz, o filtro antialiasing precisará rejeitar um sinal de entrada de> 100 kHz para garantir que não haja aliasing. Isso requer um filtro de ordem muito alta. A Figura 7 mostra a curva de demanda acentuada.

clique para ampliar a imagem

Figura 7. Requisito de alias. (Fonte:Dispositivos analógicos)

Se uma velocidade de amostragem de 400 kSPS for escolhida para relaxar a ordem do filtro, a rejeição será necessária para frequência de entrada> 300 kHz. Aumentar a velocidade de amostragem aumentará a potência e, para velocidade dupla, a potência também será duplicada. A sobreamostragem adicional ao custo de energia irá relaxar ainda mais a exigência do filtro antialiasing, já que a frequência de amostragem é muito mais alta do que o BW de entrada.

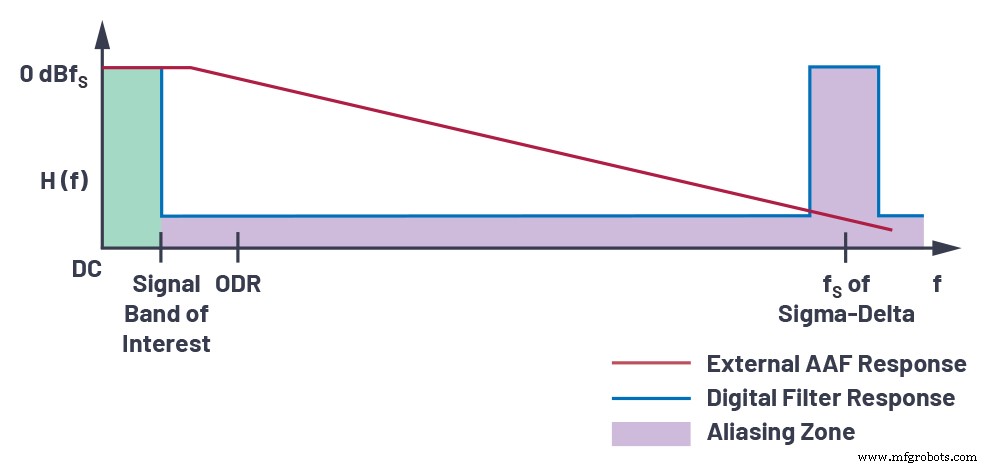

Em ADCs sigma-delta, a entrada é sobreamostrada em um OSR muito mais alto, de modo que o requisito do filtro antialiasing é relaxado, pois a frequência de amostragem é muito mais alta do que o BW de entrada, como mostrado na Figura 8.

clique para ampliar a imagem

Figura 8. Requisito do filtro anti-serrilhamento em sigma-delta. (Fonte:Dispositivos analógicos)

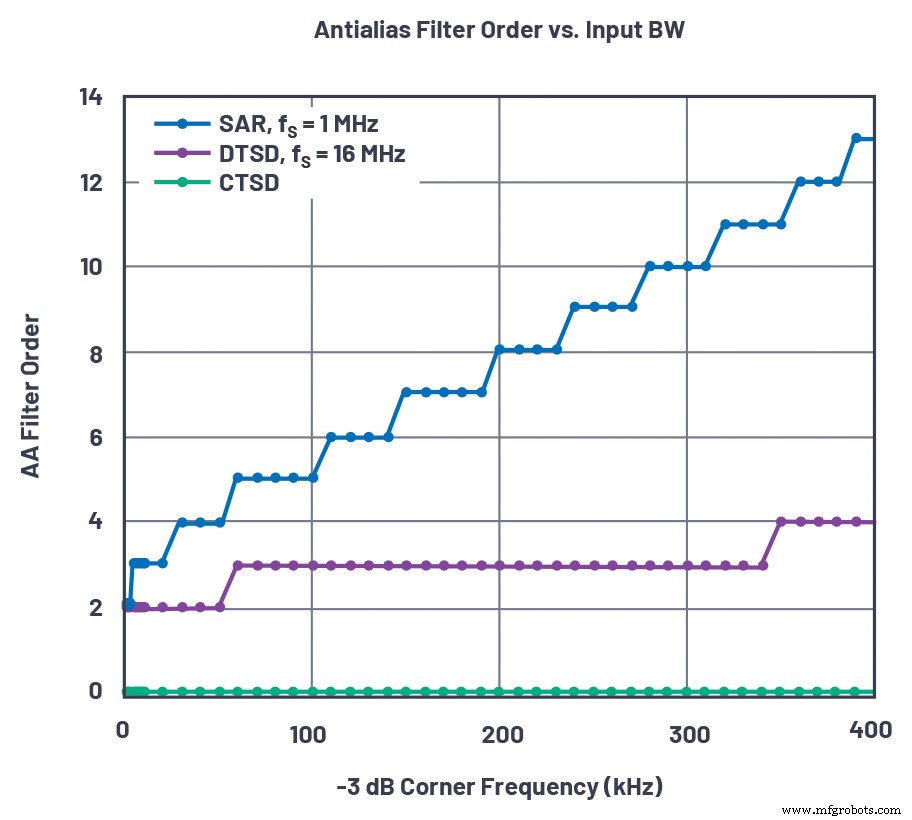

A Figura 9 dá uma ideia da complexidade AAF para as arquiteturas SAR e discrete-time sigma-delta (DTSD). Se tomarmos uma largura de banda de entrada de –3 dB de 100 kHz para atingir 102 dB de atenuação na frequência de amostragem fS, um filtro antialiasing de segunda ordem será necessário para um DTSD ADC, enquanto obter a mesma atenuação em fS exigirá um filtro de quinta ordem usando um SAR ADC.

Para um ADC sigma-delta (CTSD) de tempo contínuo, a atenuação é inerente, portanto, não precisamos de nenhum filtro anti-serrilhamento.

clique para ampliar a imagem

Figura 9. Requisito do filtro AAF para várias arquiteturas. (Fonte:Dispositivos analógicos)

Esses filtros podem ser um ponto problemático para designers de sistema, e eles precisam otimizá-los para a queda que eles fornecem na banda de interesse e fornecer o máximo de rejeição possível. Eles também adicionam muitos outros erros ao sistema, como deslocamento, ganho, erro de fase e ruído, reduzindo assim seu desempenho.

Além disso, ADCs de alto desempenho são diferenciais por natureza, portanto, precisamos do dobro de componentes passivos. Para obter uma melhor correspondência de fase em aplicativos multicanais, todos os componentes da cadeia de sinal devem corresponder bem. Como resultado, são necessários componentes com tolerância mais estreita.

Entrada de capacitor comutado

A amostragem da entrada do capacitor comutado depende do tempo de acomodação da entrada amostrada em um capacitor, criando uma demanda para carga / descarga da corrente transiente quando a chave de amostragem é ligada / desligada. Isso é chamado de retrocesso na entrada e exige um amplificador de acionamento de entrada que possa suportar essas correntes transitórias. Além disso, a entrada deve ser estabelecida no final do tempo de amostragem e a precisão da amostra de entrada determina o desempenho do ADC, implicando que o amplificador de acionamento precisa se estabilizar rapidamente após o evento de retrocesso. Isso leva à necessidade de um driver de alta largura de banda que possa suportar um ajuste rápido e absorver o retrocesso da operação do capacitor comutado. Em entradas de capacitor chaveado, sempre que a amostragem está ligada, o driver imediatamente tem que fornecer a carga para o capacitor de retenção. Esse aumento repentino na corrente só pode ser fornecido a tempo se o driver tiver recursos de largura de banda suficientes. Devido aos parasitas do switch, haverá um retrocesso no driver no momento da amostragem. Se o retrocesso não se estabilizar antes da próxima amostragem, isso resultará em um erro sendo amostrado, corrompendo assim a entrada ADC.

clique para ampliar a imagem

Figura 10. Recuo de amostragem. (Fonte:Dispositivos analógicos)

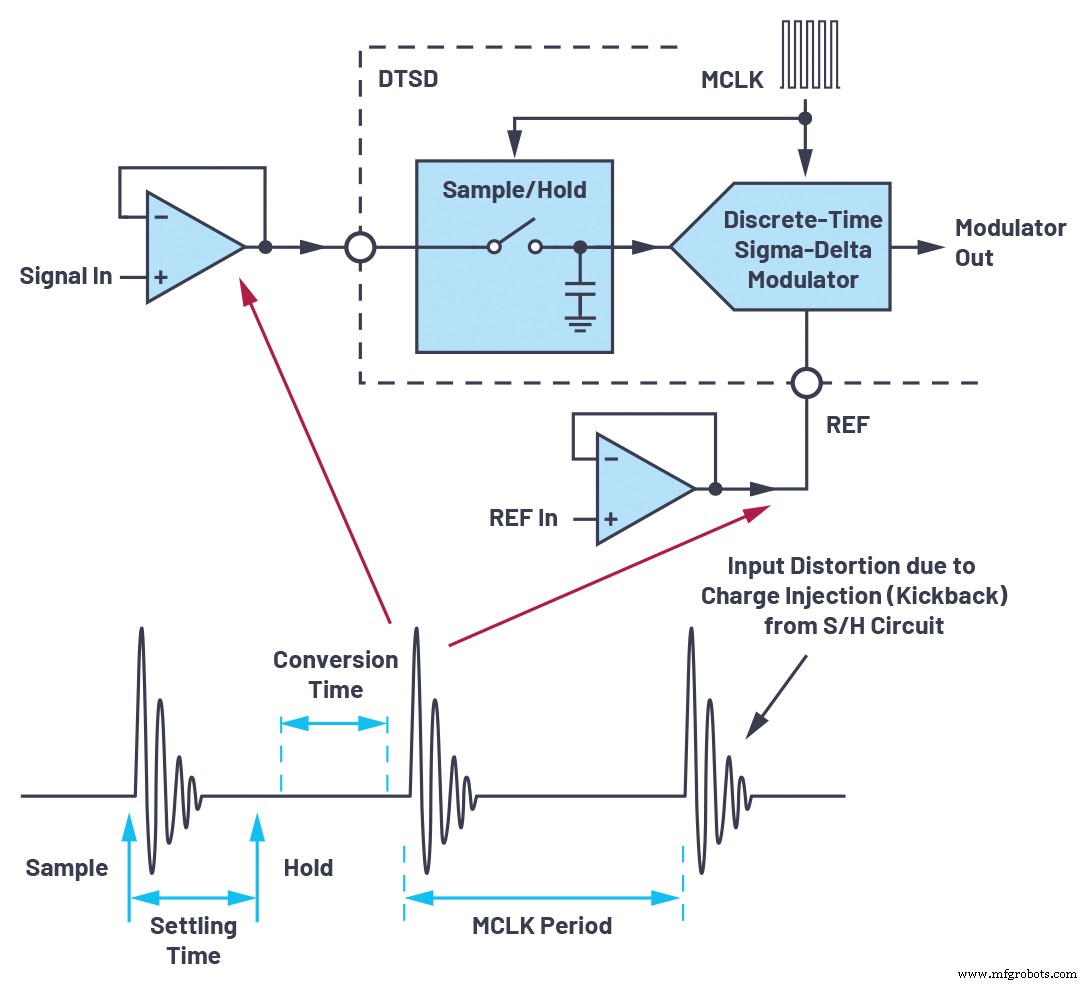

A Figura 10 mostra o retrocesso no DTSD ADC. Se, por exemplo, a frequência de amostragem é 24 MHz, o sinal de dados precisa se estabelecer dentro de 41 ns. Visto que a referência também é uma entrada de capacitor comutada, um buffer de alta largura de banda também é necessário no pino de entrada de referência. Esses buffers de sinal de entrada e referência aumentam o ruído e diminuem o desempenho geral da cadeia de sinal. Além disso, os componentes de distorção do driver do sinal de entrada (em torno da frequência S&H) aumentam ainda mais os requisitos de anti-serrilhamento. Além disso, com entradas de capacitor comutadas, as mudanças na velocidade de amostragem resultarão na variação da corrente de entrada. Isso pode resultar em um novo ajuste do sistema para reduzir o erro de ganho gerado no driver ou no estágio anterior ao dirigir o ADC.

ADC Sigma-Delta de tempo contínuo

Um CTSD ADC é uma arquitetura alternativa sigma-delta ADC que tira proveito de princípios como sobreamostragem e modelagem de ruído, mas que tem um meio alternativo de implementar a operação de amostragem que oferece benefícios de sistema significativos.

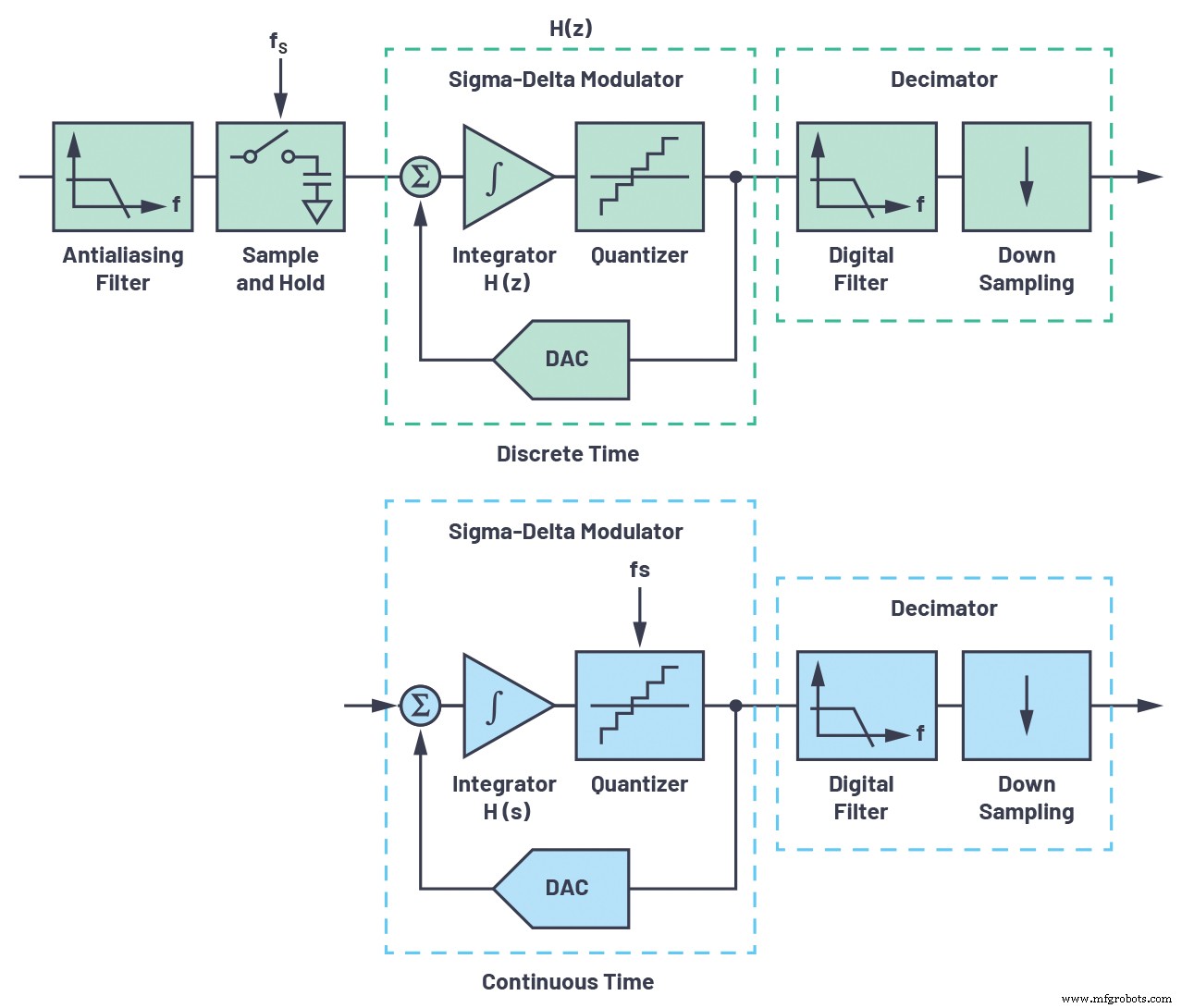

A Figura 11 mostra uma comparação de uma arquitetura DTSD e uma arquitetura CTSD. Como vemos na arquitetura DTSD, a entrada é amostrada antes do loop. O filtro de malha H (z) é discreto no tempo e implementado usando integradores de capacitores chaveados. O feedback DAC também é comutado com base em capacitor. Como há amostragem na entrada, o que resultará em um problema de aliasing de f S , um filtro anti-serrilhamento adicional é necessário na entrada antes que ela seja amostrada.

clique para ampliar a imagem

Figura 11. Esquemas de blocos modulares em tempo discreto e em tempo contínuo. (Fonte:Dispositivos analógicos)

O CTSD não possui um amostrador na entrada. Em vez disso, é amostrado no quantizador dentro do loop. O filtro de loop agora é de tempo contínuo usando integradores de tempo contínuo, assim como o DAC de feedback. Semelhante à quantização que é moldada, o aliasing devido à amostragem também é moldado. Isso resulta em um ADC quase sem amostragem, criando uma classe própria.

A frequência de amostragem do CTSD é fixa, ao contrário do DTSD, onde a frequência de amostragem do modulador pode ser facilmente escalada. Além disso, CTSD ADCs são conhecidos por serem menos tolerantes a jitter do que equivalentes de capacitores comutados. Cristal de prateleira ou osciladores CMOS fornecem clocks de baixo jitter para ADCs localmente, o que ajuda a evitar a transmissão de baixo jitter clock sobre o isolamento e reduz a EMC.

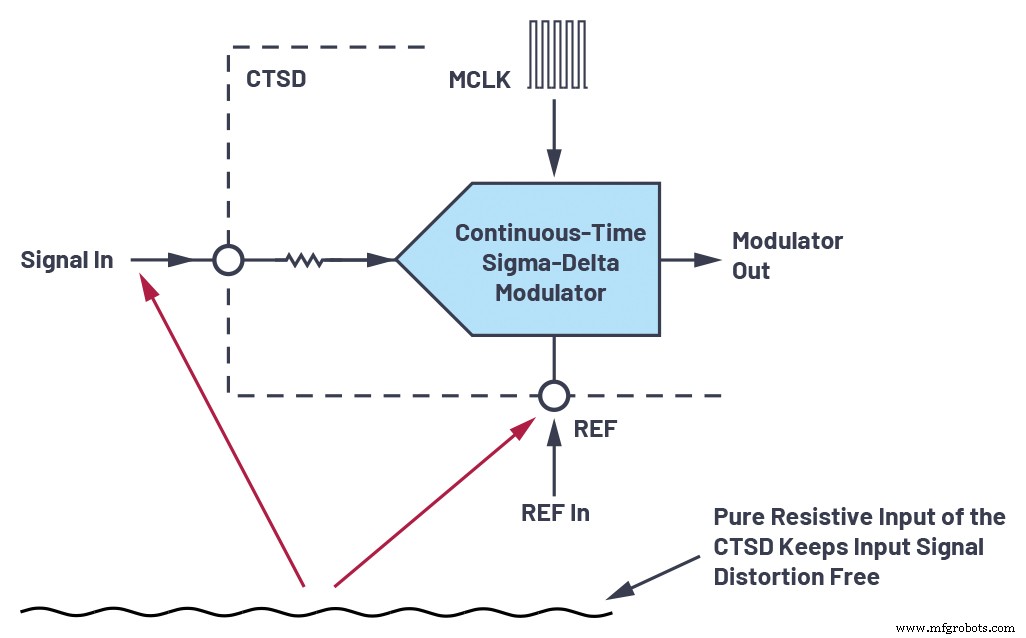

Os dois principais benefícios do CTSD são a rejeição de alias inerente e as entradas resistivas para sinais e referência.

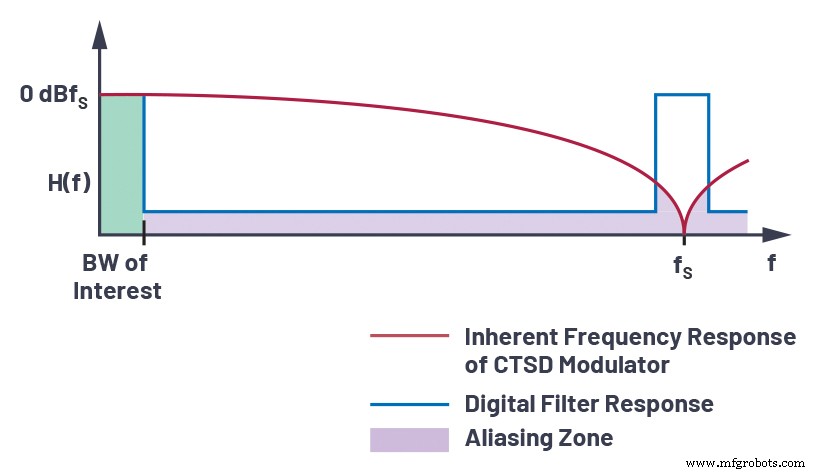

Antialiasing inerente

Moving the quantizer inside the loop results in inherent alias rejection. As shown in Figure 12, the input signal passes through the loop filter before being sampled and the foldback (alias) error, which is introduced at the quantizer, also sees this filter. The signal and the alias error will see the same noise transfer function as the sigma-delta loop, and both will have similar noise shaping as the quantization noise in sigma-delta architectures. Thus, the frequency response of the CTSD loop naturally rejects input signals around integer multiples of the sampling frequency, acting as an antialiasing filter.

click for larger image

Figure 12. Frequency response of a CTSD modulator. (Source:Analog Devices)

Resistive Input

Having resistive inputs on signal and reference inputs makes it easier to drive than the sample-and-hold configurations. With constant resistive inputs, there is no kickback and the driver can be completely removed. The input is distortion free, as shown in Figure 13. And since the input resistance is constant, the retuning of the system for gain errors is also eliminated.

click for larger image

Figure 13. Input settling for CTSD. (Source:Analog Devices)

Analog inputs can be bipolar even though the ADC has unipolar supply. This can remove the need for level shifting from a bipolar front end to the ADC. The dc performance of the ADC may not be the same as the input resistor now has input common-mode dependent current as well as the input current.

The reference load is also resistive, which reduces switching kickback, hence a separate reference buffer is not required. The resistor for a low-pass filter can be made on-chip so that it can track along with on-chip resistive load (as they could be of same material), for reduced gain error temperature drift.

CTSD architecture is not new, but the megatrends in industrial and instrumentation markets demand dc and ac precision performance at higher bandwidths. Moreover, customers prefer a single platform design that would cater to most of their solutions in order to reduce their time to market.

CTSD architecture has been the choice in a broad set of applications ranging from high performance audio to cellular handset RF front end due to a number of advantages over other types of ADCs. The benefits include greater amenability to integration and low power consumption, but also, and possibly more importantly, because using a CTSD solves a number of significant system-level problems. Due to a number of technological shortcomings, the use of CTSD has previously been limited to relative audio frequency/bandwidth and lower dynamic range. Therefore, high performance Nyquist rate converters such as successive approximation ADCs and oversampled DTSD converters have been the mainstream solution for precision, high performance/medium bandwidth applications.

However, recent technology breakthroughs have enabled overcoming many limitations. For example, the AD7134 from Analog Devices supports high precision dc to 400 kHz bandwidth ADC based on CTSD that achieves substantially higher performance specifications, while providing dc accuracy and, in turn, enabling the solution for a number of important system-level problems in high performance instrumentation applications. The AD7134 also integrates an asynchronous sample rate converter (ASRC) providing data at variable data rates derived from the fixed sampling speed of CTSD. The output data rate can be independent of modulator sampling frequency and can enable successful use of CTSD ADCs for different granular throughputs. The flexibility to change the output data rate at a granular level also enables users to use coherent sampling.

Inherent alias rejection removes the need for an antialiasing filter, which results in fewer components and a smaller solution size. More importantly, performance issues that come along with an antialiasing filter such as droop, errors such as offset, gain, and phase error, and noise in the system are no longer present. An antialiasing filter also adds significantly to the overall latency in the signal chain depending upon the rejection needed. Removal of the filter removes this delay completely, enabling precision conversion in noisy digital control loop applications.

With no antialiasing filter at the system level, phase matching in multichannel systems can be vastly improved. This is especially useful in applications demanding low channel-to-channel mismatch such as vibration monitoring, power measurements, data acquisition modules, and sonar. Because of their inherent filtering action, CTSD ADCs are also immune to any kind of interference at the system level, as well from within the IC itself. In DTSD ADCs and SAR ADCs, care has to be taken such that there is less interference when the ADC is sampling. Also, there would be immunity from interference on power supply lines due to the inherent filtering action. With constant resistive analog inputs and reference inputs, the driver requirement can be completely removed as well. Again, this addresses performance concerns such as errors like offset, gain, phase error, and noise to the system are no longer there.

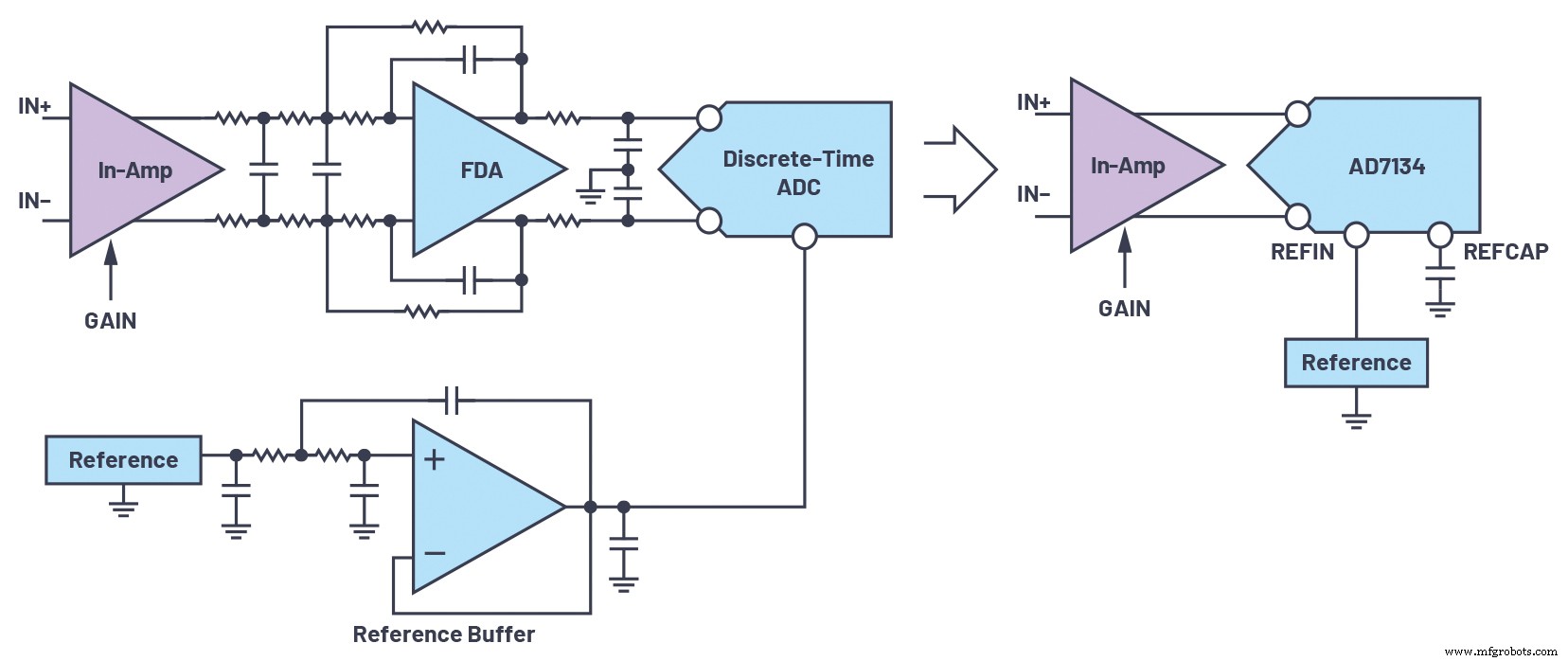

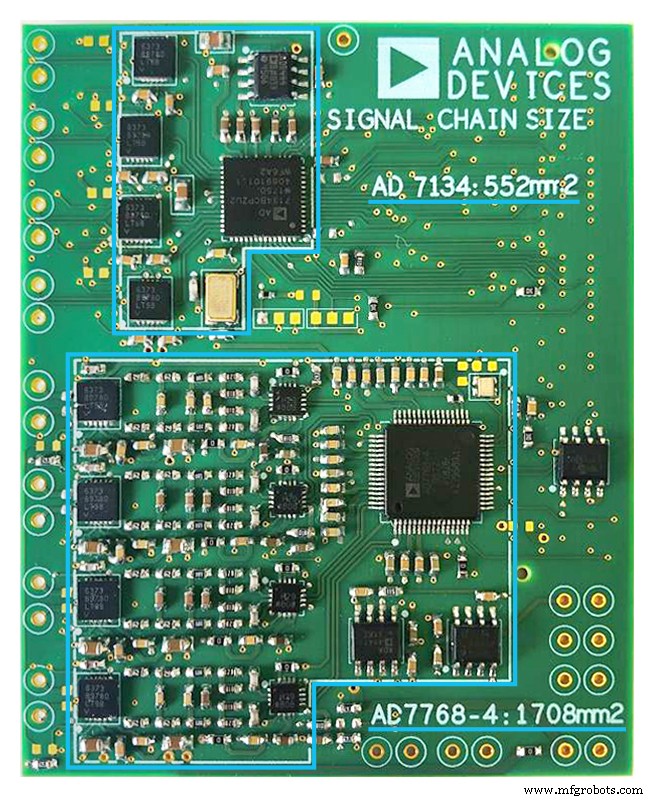

The struggle to achieve the precision performance is very minimal as the number of designed elements is significantly reduced. This result in faster design time, faster time to market for customers, easier BOM management, and reliability. Removal of an antialiasing filter, a driver, and a reference buffer will significantly reduce the system board area. An instrumentation amplifier can be used to directly drive the ADC. For example, with the AD7134, as it is a differential input only ADC, a differential in-amp such as the LTC6373 can be used as a driver. The comparison in Figure 14 shows the signal chain for a discrete-time-based signal chain and a continuous-time-based signal chain. Our experiment shows 70% of area savings when compared to an equivalent discrete-time-based signal chain, making it an excellent choice for high density multichannel applications.

In conclusion, this approach offers significant system size reduction, simplifies the signal chain design, makes the system more robust, and reduces the overall time to market with easy design-in without trading any performance parameters demanded by precision instrumentation applications.

click for larger image

Figure 14. A discrete-time-based (left) and a continuous-time-based (right) signal chain comparison. (Source:Analog Devices)

click for larger image

Figure 15. Size comparison of discrete-time and continuous-time signal chain. (Source:Analog Devices)

References

Kester, Walt. “MT-002:What the Nyquist Criterion Means to Your Sampled Data System Design.” Analog Devices, Inc., 2009.

Pavan, Shanti. “Alias Rejection of Continuous-Time Δ∑ Modulators with Switched Capacitor Feedback DACs.” IEEE Transactions on Circuits and Systems I:Regular Papers , Vol. 58, No. 2, February 2011.

Schreier, Richard and Gabor C. Temes. Understanding Delta-Sigma Data Converters. John Wiley and Sons, 2005.

Acknowledgements

The author would like to thank Abhilasha Kawle, Avinash Gutta, and Roberto Maurino for their support on this article.

Integrado

- Termos e conceitos de memória digital

- Variáveis C# e tipos de dados (primitivos)

- Conversão de tipo Python e conversão de tipo

- Semáforos:serviços utilitários e estruturas de dados

- Apacer:Cartões CV110-SD e CV110-MSD lançados em todo o mundo

- Swissbit:soluções de segurança baseadas em hardware para proteger dados e dispositivos

- Hiperconvergência e armazenamento secundário:Parte 2

- Construindo IA responsável e confiável

- Blockchain e cadeias de suprimentos:Liberando o potencial

- O significado dos Data Fabrics - e como eles beneficiam as cadeias de suprimentos