Processador crossover de baixo custo suporta inferência de endpoint

BRISTOL, UK - XMOS adaptou seu núcleo de processador Xcore para aprendizado de máquina, criando um processador cruzado para aplicativos AIoT. O Xcore.ai estará disponível a partir de $ 1.

Xcore.ai, a terceira geração de produtos desenvolvidos com base no design principal proprietário da empresa, é projetado para inferência de IA em tempo real e tomada de decisão em dispositivos de endpoint e também pode lidar com funções de processamento de sinal, controle e comunicação.

A novidade neste chip de terceira geração é um recurso de pipeline de vetor para aplicativos de aprendizado de máquina. É o único processador crossover de seu tipo a oferecer suporte a redes neurais binarizadas (1 bit), que estão crescendo em importância para IA de ultra-baixa potência em aplicativos de endpoint, pois oferecem uma melhoria de ordem de magnitude no desempenho e densidade de memória comercializada para uma redução modesta na precisão (o Xcore.ai também suporta números de 32, 16 e 8 bits).

O Xcore.ai junta-se a uma nova classe de sistema com capacidade de IA em chips para aplicações de endpoint, o processador crossover (Imagem:XMOS)

Xcore.ai se junta a uma classe emergente de processador de endpoint com capacidade de IA, o processador cruzado. Cunhado pela NXP, este termo descreve uma nova categoria importante de dispositivos com o desempenho de um processador de aplicativo combinado com a facilidade de uso, baixo consumo de energia e operação em tempo real de um microcontrolador.

“Se você conversar com os clientes sobre‘ microcontroladores ’, eles pensam nos dispositivos Cortex-M0, M3 ou M4 que custam 75 centavos ou menos, com desempenho relativamente baixo, cem MIPS ou mais. Então, 'SoCs' pode ser algo com núcleos quad-A53, que funciona a um gigahertz. Há uma grande lacuna para as coisas no meio, como processadores para voz, que é um problema de matemática particularmente difícil, exigindo milhares de MIPS. Portanto, há essa grande lacuna com uma área de aplicação realmente grande e importante situada bem no meio dela, e ela merece um nome ”, disse Mark Lippett, CEO da XMOS, em uma entrevista exclusiva ao EETimes.

Interfaces de voz

O produto de segunda geração anunciado anteriormente pela empresa, o XVF3510, foi lançado em julho de 2019 como um ASIC para interfaces de voz, mas por baixo do capô o silício também é baseado no design Xcore proprietário da empresa, enviado com firmware. Projetos de referência para soluções de voz de campo distante baseadas no XVF3510 são qualificados para o Alexa Voice Service da Amazon.

Dada a história do XMOS no setor de voz, não é surpresa que o chip Xcore.ai será inicialmente direcionado a aplicativos de interface de voz que requerem IA para detecção de palavras-chave ou funções de dicionário.

“Vamos ser absolutamente claros, a voz é a carga de trabalho de IA mais importante no endpoint e provavelmente permanecerá assim por muito tempo. Mas, para tornar as interfaces de voz melhores, você descobrirá que os dispositivos se tornarão mais multimodais ”, disse Lippett, descrevendo uma tendência de usar diferentes tipos de sensores para tornar os aplicativos mais sensíveis ao contexto, seja para detectar a presença de uma pessoa ou onde eles estão falando.

Mark Lippett (Imagem:XMOS)

“Há muitas oportunidades de melhorar as experiências do usuário não apenas ouvindo áudio, mas fazendo mais do que apenas isso”, disse ele.

Muitas aplicações de IA em dispositivos IoT dependem de uma combinação de privacidade, segurança e proteção que exige que o processamento seja feito no terminal. Lippett descreveu os recursos de segurança em aparelhos que usam voz e radar para desligar o forno se apenas crianças estiverem presentes na cozinha, por exemplo.

Xcore.ai irá, portanto, ir ao mercado com bibliotecas fornecidas para a criação de interfaces de voz, mas Lippett disse que tem capacidade sobressalente para os clientes construírem seus próprios sistemas. Uma interface MIPI está incluída para entrada de câmera.

Arquitetura Xcore

O chip Xcore.ai oferece até 3200 MIPS, 51,2 GMACCs e 1600 MFLOPS. Possui 1 Mbyte de SRAM incorporada mais uma interface DDR de baixa potência para expansão.

Versus um dispositivo Cortex-M7 que fornece aproximadamente o mesmo nível de integração que Xcore.ai, rodando em uma frequência operacional semelhante, os próprios números do XMOS colocam sua parte em 32x o desempenho de processamento AI e 15x o desempenho DSP.

“No mundo do endpoint, tem que haver preço-desempenho, não adianta falar de um sem o outro”, disse Lippett. “Temos sido muito agressivos no preço, podemos chegar a US $ 1 por esta peça [em volume]. Em termos gerais, custamos cerca de metade do custo [do dispositivo Cortex-M7 comparável] e estamos perdendo tudo em termos de desempenho ”.

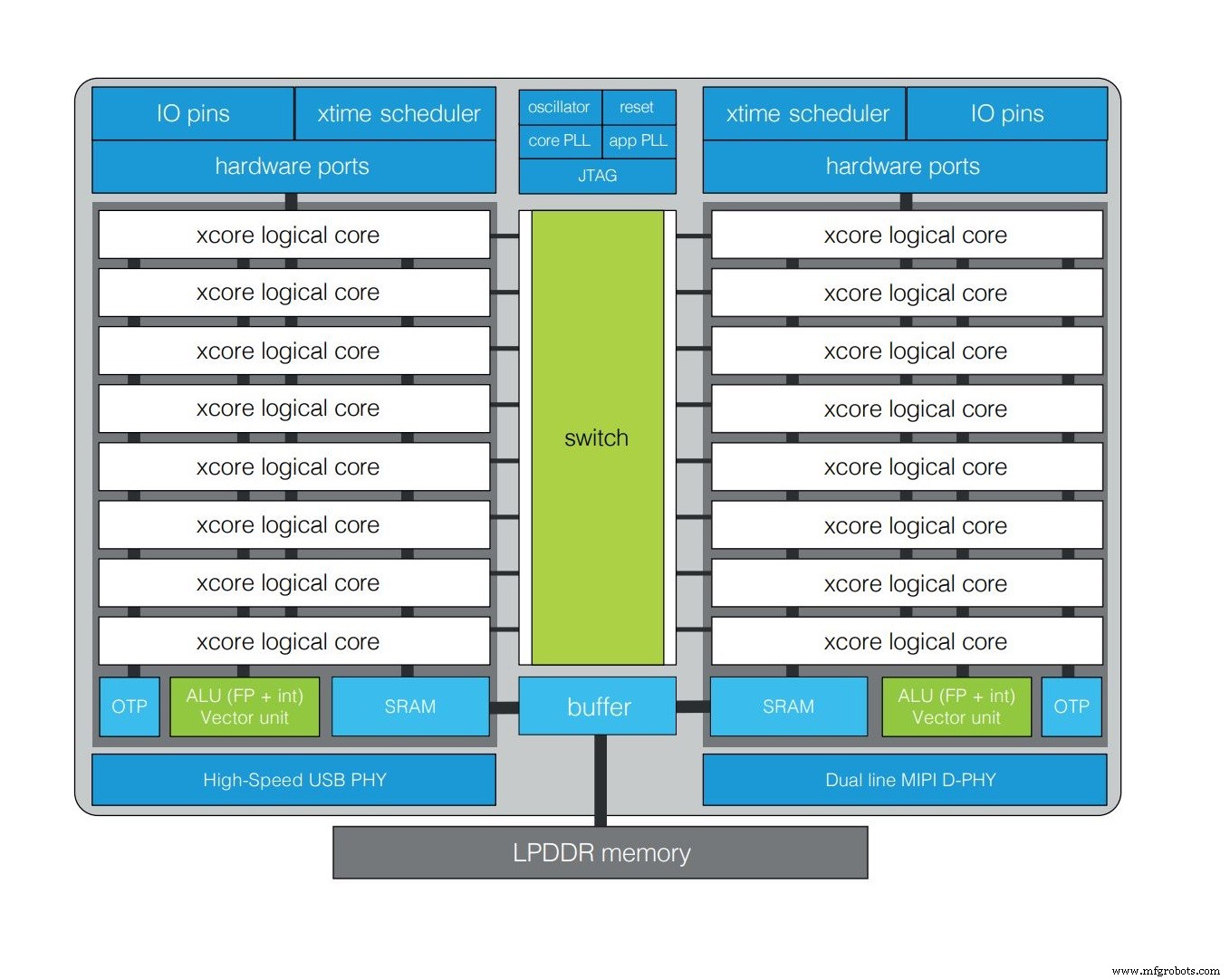

O Xcore é baseado em núcleos lógicos dispostos em blocos com memória,

ALUs e unidades de vetor (Imagem:XMOS)

Xcore.ai é baseado na arquitetura Xcore proprietária do XMOS. O próprio Xcore é construído em blocos de construção chamados núcleos lógicos, que podem ser usados para E / S, DSP, funções de controle ou aceleração de IA. Existem oito núcleos lógicos em cada bloco, com dois blocos em cada chip Xcore.ai, e os projetistas podem escolher quantos núcleos alocar para cada função. Cada bloco também contém memória, ALUs e uma unidade vetorial à qual os núcleos lógicos compartilham acesso.

“De maneira crítica, eles [compartilham o acesso] de uma forma muito previsível”, disse Lippett. “Isso é o que há de especial no Xcore. Inicialmente, queríamos fornecer flexibilidade de E / S para engenheiros de software, e o hardware não é muito tolerante se você perder prazos. Portanto, o Xcore é multi-core, não porque queremos reduzir as cargas de trabalho e fazer as coisas muito rapidamente - podemos fazer isso - mas na verdade é multi-core porque queremos dar a partes específicas do aplicativo seus próprios recursos, para que quando é necessário, está pronto. É projetado de baixo para cima para fornecer esse tipo de precisão de tempo. ”

O mapeamento de diferentes funções (I / O, DSP, controle, AI) para os núcleos lógicos no firmware permite a criação de um 'SoC virtual', inteiramente escrito em software. No exemplo abaixo, um núcleo está realizando tarefas que normalmente seriam feitas em hardware, como I

2

S, I

2

Os drivers C e LED, e alguns núcleos estão processando a rede neural, enquanto outros estão fazendo tarefas que normalmente seriam feitas no software. Definir tudo isso no software é mais rápido, para atender às demandas transitórias dos dispositivos IoT. O desenvolvimento também é mais barato, disse Lippett, permitindo que as empresas criem soluções que sejam econômicas mesmo em segmentos de mercado menores.

Um exemplo de aplicativo mapeado em um dispositivo Xcore.ai (Imagem:XMOS)

“A forma como vemos a evolução do mercado é que o mercado está exigindo recursos mais diversos e as empresas precisarão responder mais rapidamente”, disse Lippett. “É muito difícil fazer uma aposta de dois anos na IoT sem construir uma plataforma muito genérica que pode [eventualmente] não ser boa o suficiente para qualquer segmento. [Com o Xcore.ai], é muito mais fácil levar dispositivos ao mercado com muito mais rapidez, com menos capex, e efetivamente fazer apostas menores em mercados menores e tornar esses mercados econômicos. ”

Como o XMOS competirá contra os grandes fabricantes de microcontroladores que estão se mudando para esse espaço de processador cruzado?

“Não construindo SoCs baseados em ARM! Porque eles fazem isso muito bem ”, disse Lippett. “A única maneira de competir contra esses caras é tendo uma vantagem arquitetônica. Trata-se das capacidades intrínsecas do Xcore em termos de desempenho, mas também da flexibilidade. ”

Integrado

- Renesas destaca inteligência de endpoint no mundo incorporado 2019

- MCUs visam pontos de extremidade IoT seguros e designs de borda

- Módulos de processador sem fio pré-certificados possuem conectividade Bluetooth mesh

- Usar vários chips de inferência exige um planejamento cuidadoso

- PMIC simplifica designs de processador multi-rail

- Tiny haptic IC suporta wearables de baixa potência

- Processador multicore integra unidade de processamento neural

- Radar-on-chip de 60 GHz suporta os requisitos da indústria automotiva

- IC de gerenciamento de energia compatível com a família de processadores de aplicativos

- Processadores especializados aceleram cargas de trabalho de IA de endpoint