Arquitetura híbrida acelera IA, cargas de trabalho de visão

Quadric, uma startup do Vale do Silício, construiu um acelerador projetado para acelerar as cargas de trabalho de algoritmo de visão computacional e IA para dispositivos de ponta, como robôs, automação de fábrica e imagens médicas. A arquitetura de hardware da empresa é um novo fluxo de dados híbrido e design de Von Neumann que pode lidar com cargas de trabalho, incluindo redes neurais, aprendizado de máquina, visão computacional, DSP e subprogramas básicos de álgebra linear.

“Desde o início, estávamos cientes de que a IA não é o único aplicativo necessário para a computação no dispositivo em dispositivos de ponta”, disse o CEO da Quadric, Veerbhan Kheterpal ao EE Times . “Os desenvolvedores desses produtos precisam que o sistema completo seja capaz de executar algoritmos clássicos de computação de alto desempenho, junto com IA. Esses são realmente os requisitos completos do sistema. ”

Kheterpal enfatizou que a arquitetura não é uma coleção de aceleradores para cargas de trabalho individuais. Em vez disso, é uma arquitetura unificada com um conjunto de instruções paralelas de dados projetado para acelerar cargas de trabalho variadas, incluindo inferência de IA.

"Onde a IA está se movendo ultimamente, existem algumas tendências interessantes em torno da substituição de camadas inteiras por uma transformada rápida de Fourier (FFT)", disse Daniel Firu, diretor de produto da Quadric. Quadric está se posicionando para acelerar esses tipos de cargas de trabalho, citando um artigo recente do Google em que os pesquisadores aceleraram uma rede de transformadores substituindo algumas camadas por um FFT. O Google substituiu a subcamada de autoatenção de um codificador de transformador por um FFT para gerar uma rede que atingiu 92 por cento de precisão no benchmark BERT; o treinamento foi até sete vezes mais rápido nas GPUs ou duas vezes mais rápido nas TPUs do Google.

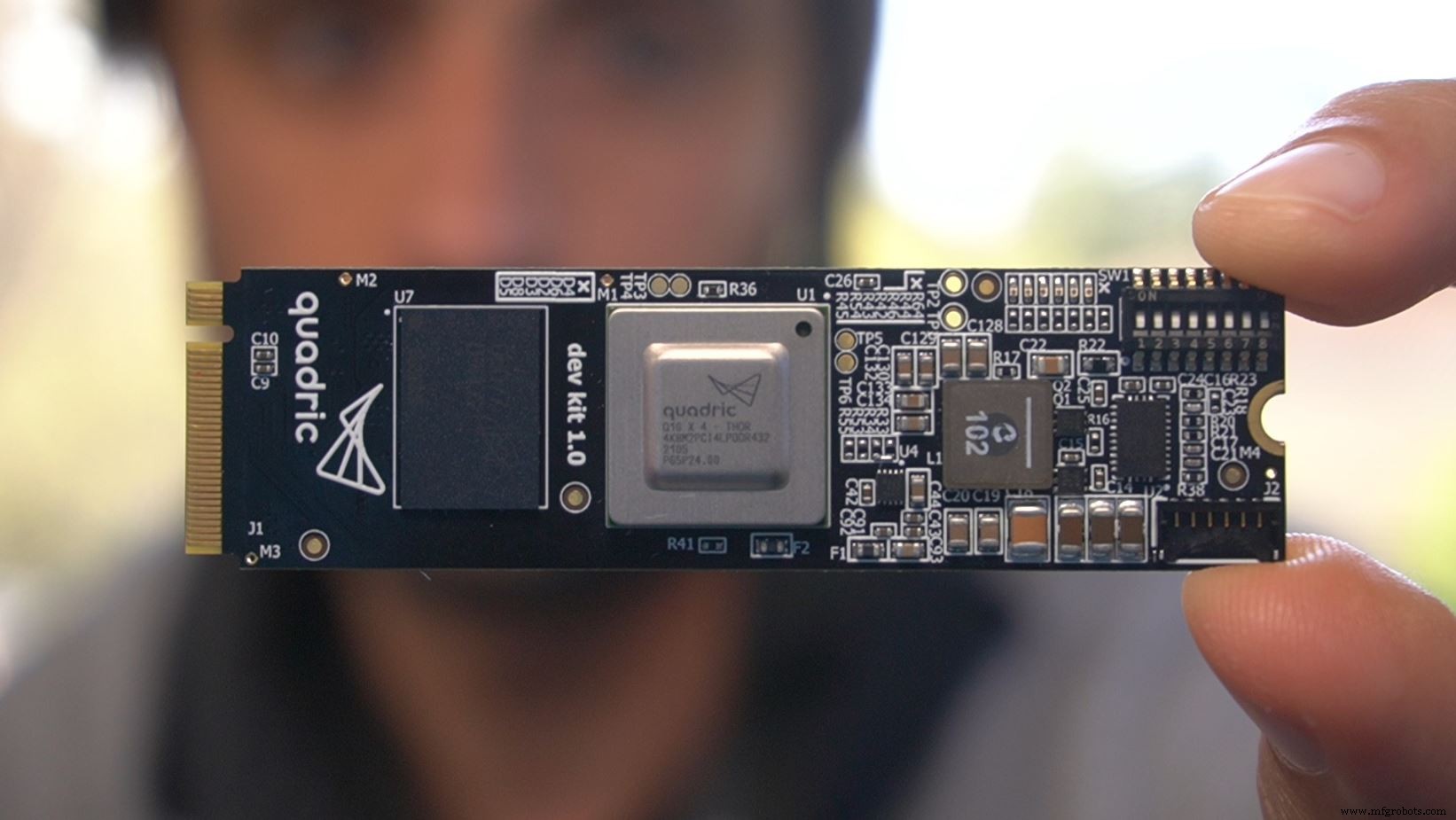

Kit de desenvolvedor Quadric, uma placa M.2 com o processador Q16 e 4 GB de memória externa (Fonte:Quadric)

Robôs Vineyard

Os três cofundadores da Quadric, Veerbhan Kheterpal, Daniel Firu e Nigel Drego, fundaram anteriormente a 21, uma empresa de mineração de bitcoin que foi vendida para a Coinbase. Quadric, Burlingame, Califórnia, não começou projetando chips. Em vez disso, ele originalmente construiu robôs agrícolas que podiam subir e descer os vinhedos do Vale do Napa olhando as vinhas e enviando alertas quando detectava vazamentos de irrigação ou pragas.

Veerbhan Kheterpal (Fonte:Quadric)

“Quando o estávamos construindo, percebemos que não seria um produto viável construído a partir da cadeia de suprimentos de drones por US $ 5 a US $ 10.000”, disse Kheterpal. “Teria que ser construído a partir da cadeia de suprimentos de trator, custando US $ 50.000, e carregar PCs grandes com GPUs, com toneladas de câmeras. Foi quando começamos a examinar os bastidores de todo aquele software de robótica e descobrimos o que estava fundamentalmente causando essa necessidade de energia para crescer com plataformas como Nvidia e Intel. ”

A empresa começou a construir um chip acelerador - “o chip que gostaríamos de ter”, de acordo com Firu.

Uma rodada de financiamento inicial foi lançada em 2017, seguida por uma rodada da Série A que gerou US $ 13 milhões de clientes em potencial, incluindo o investidor líder da Quadric, o setor automotivo japonês Tier-One Denso. O financiamento total da Quadric é de US $ 18 milhões.

Turing concluído

Quadric's emprega uma arquitetura orientada a instruções que pega elementos de arquiteturas de fluxo de dados e os combina com elementos de uma máquina Von Neumann. O objetivo é substituir sistemas heterogêneos em dispositivos de ponta por algo menos complexo. Como máquinas Turing completas, os núcleos Quadric Vortex oferecem uma combinação de aceleração com flexibilidade, afirma a empresa. A arquitetura é escalável em termos de matrizes de núcleos e portátil para nós de processo avançados (7 ou 5 nm). Isso é adequado para aplicativos de dispositivos de ponta com orçamentos de energia entre aproximadamente centenas de miliwatts a 20W.

O primeiro chip da empresa, o Q16, é uma matriz de núcleos Vortex de 16 x 16. Cada núcleo tem a capacidade de realizar multiplicação de matrizes e cálculos de IA, mas cada um também tem uma ALU multifuncional, para operações como AND, OR, redução, deslocamento e outras. O software permite que os desenvolvedores expressem diversos tipos de algoritmo, incluindo funções de ativação LSTM e muito mais. As instruções If-Then-Else estão disponíveis em todo o array, permitindo que os desenvolvedores aproveitem a dispersão de baixa granularidade.

Cada núcleo do array tem acesso de ciclo único a seus núcleos vizinhos, além de acesso de ciclo único à memória interna de 4 Kb. A memória on-chip também está incluída junto com o array, dando aos núcleos acesso determinístico de baixa latência.

Os núcleos operam em paralelo no que Quadric chama de maneira de “instrução única, decodificação múltipla”; cada núcleo recebe a mesma instrução em cada ciclo. Mas, com base em dados dinâmicos em tempo de execução, cada núcleo pode interpretar essa instrução de maneira diferente. Isso permite que os núcleos, ou grupos de núcleos, executem funções ligeiramente diferentes.

Também está incluído um barramento de transmissão dedicado que otimiza a largura de banda no array e pode ser usado para transmitir constantes, como pesos de rede neural, em todos os núcleos de uma vez (Firu disse que muitos algoritmos de visão de computador também têm algumas informações invariáveis de loop que podem ser mapeado no ônibus).

As informações dinâmicas entram no array por meio de unidades de armazenamento de carga estáticas e controladas por software, que permitem tempos de execução de kernel determinísticos. O dispositivo permite o carregamento e armazenamento simultâneos de quaisquer duas bordas de um dispositivo, além de uma propriedade especial de uma borda que pode ser usada para enviar pesos de rede neural - carregar de duas bordas e armazenar de uma terceira borda simultaneamente pode reduzir os tempos de execução de computação.

Daniel Firu (Fonte:Quadric)

“Você pode carregar em um lado e armazenar de um lado perpendicular”, disse Firu. “Isso permite que coisas muito interessantes aconteçam no nível do software. Você também pode começar a fazer coisas como mapeamentos de dados e rotações de imagens e coisas assim usando este paradigma. ”

Enquanto isso, memórias estáticas controladas por software (não cache) no chip oferecem espaço para grandes estruturas de dados. O Quadric permite acesso à API para que os desenvolvedores possam definir estruturas de dados arbitrárias em seu interior. No chip Q16, as memórias são de 8 GB, o suficiente para caber “dois ou três buffers de quadro no HD, ou uma rede neural inteira de pesos”, disse Firu.

Pilha de software

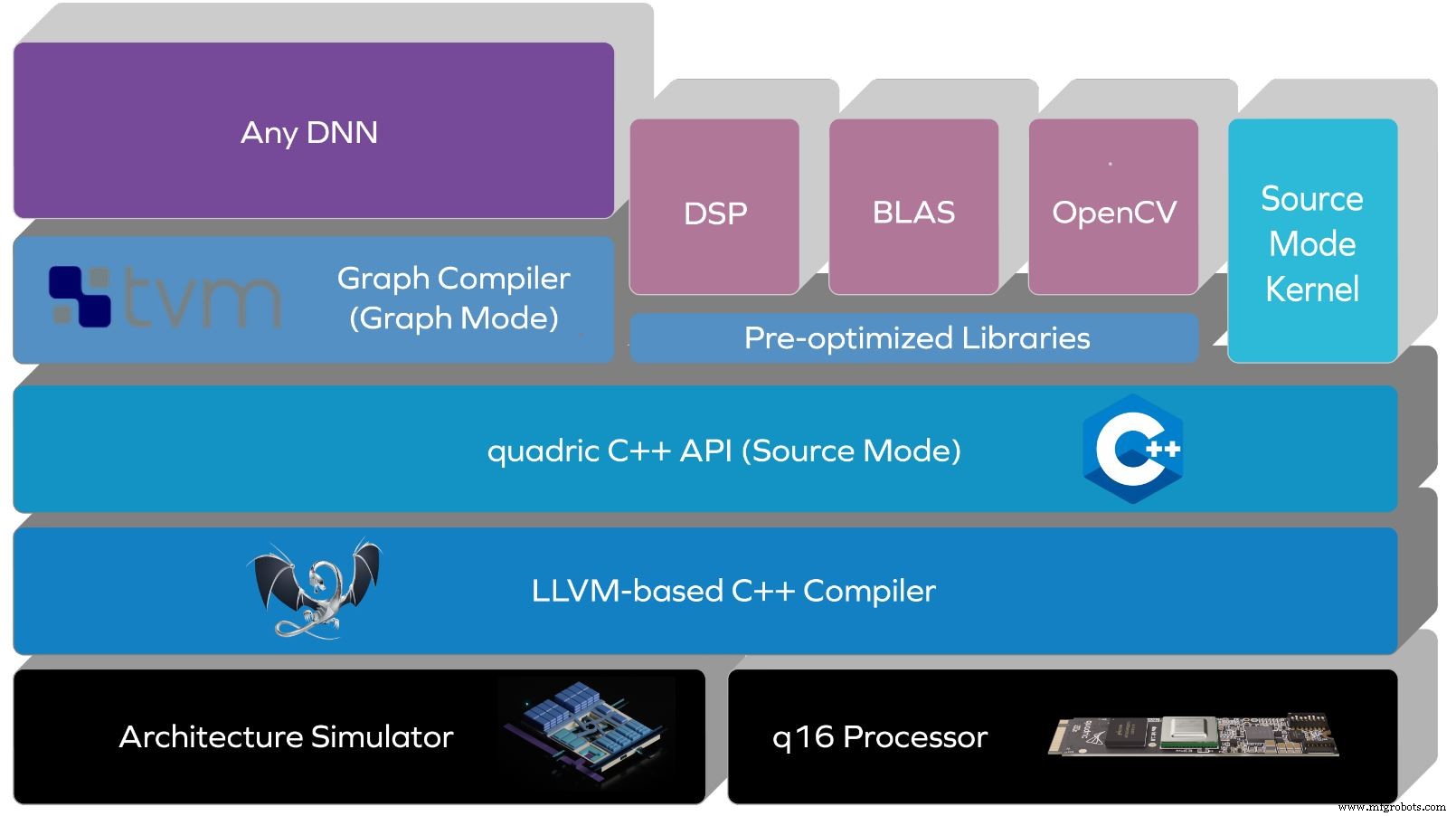

A Quadric construiu sua pilha de software antes do silício. Os clientes já o usam com o simulador de arquitetura da empresa, ou com FPGAs, há um ano, disse Kheterpal. A pilha do Quadric abstrai a arquitetura e o conjunto de instruções por meio de um compilador baseado em LLVM, com uma API C ++ no topo.

O Modo Fonte oferece suporte a diferentes algoritmos paralelos de dados com controle C ++ em nível de fonte dos recursos arquitetônicos do processador. À medida que as redes neurais se tornam mais complexas, o modo de origem também permite que os desenvolvedores expressem operações personalizadas.

Pilha de software do Quadric (Fonte:Quadric)

Uma atualização futura da pilha oferecerá um modo de gráfico sem código, que será compatível com as versões TensorFlow ou ONNX de redes neurais. Isso incluirá um compilador de rede neural profunda (DNN) baseado em TVM que gera código automaticamente.

“Estamos combinando o poder do não-código com a flexibilidade de ter seu próprio código personalizado e combiná-los de maneiras interessantes para atingir sua aplicação”, disse Kheterpal. “A maioria das plataformas oferecerá apenas uma arquitetura específica de IA com algum tipo de compilador DNN - mas e a personalização? Que tal um DNN que não é compatível? E os operadores que não são suportados? Não temos essas restrições porque este é um núcleo completo de Turing, os núcleos podem fazer qualquer operação. A flexibilidade do código dá aos desenvolvedores a capacidade de escrever qualquer algoritmo que desejem. ”

Roteiro de fichas

O chip Q16 da Quadric, que possui 256 núcleos Vortex em uma matriz de 16 x 16 em silício de 16 nm, oferece 4 INT8 DNN TOPS. Ele pode executar o ResNet-50 a 200 inferências por segundo (para parâmetros INT8 com tamanho de imagem 224 x 224), consumindo em média 2W.

O roteiro da Quadric inclui uma segunda geração da arquitetura, além de uma fita de um chip Q32 (uma matriz de 1.000 núcleos), "provavelmente em 7 nm", disse Firu. Embora o Q16 seja estritamente um acelerador (ele ficaria ao lado de um processador host do sistema), o Q32 em desenvolvimento também pode incluir núcleos Arm ou RISC-V para atuar como host.

Um kit de desenvolvedor de formato M.2, com um processador Q16 ao lado de 4 GB de memória externa diretamente mapeada para o espaço de memória universal do Q16, já está disponível.

>> Este artigo foi publicado originalmente em nosso site irmão, EE Vezes.

Conteúdos Relacionados:

- Aceleradores de hardware atendem a aplicativos de IA

- Quando um DSP supera um acelerador de hardware

- Um guia para acelerar aplicativos com instruções personalizadas RISC-V perfeitas

- O desempenho do chip de inferência baseia-se no design de subsistema de memória otimizado

- Novos módulos de aceleração de IA melhoram o desempenho de ponta

- Edge AI desafia a tecnologia de memória

Para obter mais informações sobre o Embedded, assine o boletim informativo semanal por e-mail da Embedded.

Integrado

- Ambientes de nuvem híbrida:um guia para os melhores aplicativos, cargas de trabalho e estratégias

- A arquitetura do chip AI visa o processamento do gráfico

- MCU sem fio apresenta arquitetura dual-core

- Processadores especializados aceleram cargas de trabalho de IA de endpoint

- O design de referência suporta cargas de trabalho de IA com uso intensivo de memória

- A placa do sensor inteligente acelera o desenvolvimento de IA de borda

- Câmera inteligente oferece visão de máquina de ponta turnkey AI

- IBM apresenta uma arquitetura Hybrid Blockchain para a Internet das coisas

- Omrons TM Cobot acelera a integração e a programação

- Visão hiperespectral. O que é?