Assinado vs. Não assinado em VHDL

Todos os designers digitais devem entender como a matemática funciona dentro de um FPGA ou ASIC. O primeiro passo para isso é entender como os tipos de sinais assinados e não assinados funcionam. Existem tipos assinados e não assinados no numeric_std pacote, que faz parte da biblioteca ieee. Deve-se notar que há outro arquivo de pacote que é usado frequentemente para realizar operações matemáticas:std_logic_arith . No entanto, std_logic_arith não é um arquivo de pacote oficial suportado pelo ieee e não é recomendado para uso em projetos digitais.

Um sinal definido como tipo assinado significa que as ferramentas interpretam este sinal como positivo ou negativo. Um sinal definido como tipo unsigned significa que o sinal será apenas positivo. Internamente, o FPGA usará o Two's Complement representação. Por exemplo, um sinal de 3 bits pode ser interpretado de acordo com a tabela abaixo:

Você está confuso ainda? Você deveria estar, isso não é intuitivo! Vejamos um exemplo que esperamos esclarecer as coisas. O arquivo abaixo testa como o assinado não assinado funciona. O que precisa ser entendido é que se os sinais são ou não definidos como assinados ou não assinados não afetam como a matemática binária real é executada.

Por exemplo:para dois vetores com sinal 10001 + 00010, a resposta ainda é 10011, MAS é a interpretação do resultado que é diferente.

Para o caso não assinado, a resposta (10011) representa 19.

Para o caso assinado, a resposta (10011) representa -13.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end signed_unsigned;

architecture behave of signed_unsigned is

signal rs_SUM_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUM_RESULT : unsigned(4 downto 0) := (others => '0');

signal rs_SUB_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUB_RESULT : unsigned(4 downto 0) := (others => '0');

begin

-- Purpose: Add two numbers. Does both the signed and unsigned

-- addition for demonstration. This process is synthesizable.

p_SUM : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUM_RESULT <= (others => '0');

ru_SUM_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUM_RESULT <= unsigned(i_a) + unsigned(i_b);

rs_SUM_RESULT <= signed(i_a) + signed(i_b);

end if;

end process p_SUM;

-- Purpose: Subtract two numbers. Does both the signed and unsigned

-- subtraction for demonstration. This process is synthesizable.

p_SUB : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUB_RESULT <= (others => '0');

ru_SUB_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUB_RESULT <= unsigned(i_a) - unsigned(i_b);

rs_SUB_RESULT <= signed(i_a) - signed(i_b);

end if;

end process p_SUB;

end behave;

Banco de teste:

library ieee;

use ieee.std_logic_1164.all;

entity example_signed_unsigned_tb is

end example_signed_unsigned_tb;

architecture behave of example_signed_unsigned_tb is

--Registers

signal r_CLK : std_logic := '0';

signal r_RST_L : std_logic := '0';

signal r_A : natural := 0;

signal r_B : natural := 0;

signal r_A_SLV : std_logic_vector(4 downto 0) := (others => '0');

signal r_B_SLV : std_logic_vector(4 downto 0) := (others => '0');

constant c_CLK_PERIOD : time := 10 ns;

component example_signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end component example_signed_unsigned;

begin

i_DUT: example_signed_unsigned

port map (

i_rst_l => r_RST_L,

i_clk => r_CLK,

i_a => r_A_SLV,

i_b => r_B_SLV

);

clk_gen : process is

begin

r_CLK <= '0' after c_CLK_PERIOD/2, '1' after c_CLK_PERIOD;

wait for c_CLK_PERIOD;

end process clk_gen;

process

begin

r_RST_L <= '0';

wait for 20 ns;

r_RST_L <= '1';

wait for 20 ns;

r_A_SLV <= "01001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00010";

wait for 20 ns;

r_A_SLV <= "11111";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "00000";

r_B_SLV <= "00001";

wait for 20 ns;

wait;

end process;

end behave;

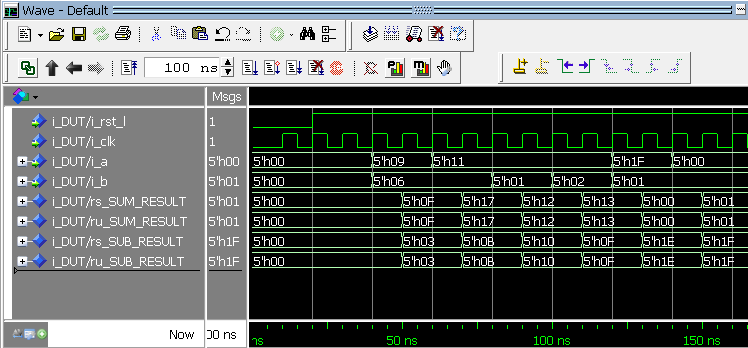

Valores de saída de onda de simulação de modelo mostrados em HEX

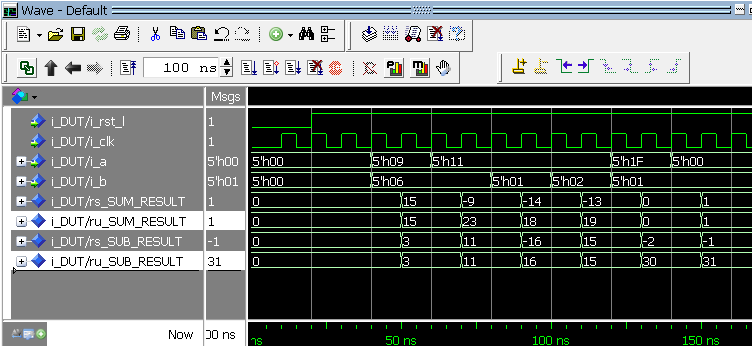

Valores de saída de onda de simulação de modelo mostrados em HEX  Valores de saída de onda de simulação de modelo mostrados em DECIMAL

Valores de saída de onda de simulação de modelo mostrados em DECIMAL Compare as duas capturas de tela do modelsim acima. No primeiro você pode ver que os resultados das funções matemáticas são exatamente as mesmas quando representadas em hexadecimal. É a interpretação dos resultados que é diferente. Isso pode ser visto olhando para a captura de tela inferior. Quando o Modelsim exibe os resultados em decimal, ele interpreta alguns deles como números negativos. Ao usar tipos assinados e não assinados, você deve ter muito cuidado! Espero que você entenda um pouco melhor este tópico. Eu sinto que essa é uma área com a qual muitos designers digitais lutam, então se houver algo que você não entenda completamente, por favor me envie um e-mail através do link de contato na barra lateral e tentarei deixar mais claro.

VHDL