Determinismo da fase de inicialização:Usando sincronização multichip

A integração de vários blocos de processamento de sinal digital (DSP), conversores digital-analógico (DACs) de banda larga e conversores analógico-digital (ADCs) de banda larga dentro de um único chip monolítico está agora permitindo o descarregamento de recursos FPGA famintos de energia para permitem uma pegada menor, menor potência, plataformas de contagem de canais aumentadas que podem amostrar em taxas mais altas do que as obtidas anteriormente. Junto com essa nova capacidade, vêm os novos algoritmos de sincronização multichip (MCS) dentro desses circuitos integrados (ICs), que permitem aos usuários atingir uma fase (determinística) conhecida para todos os canais ao alimentar o sistema ou de outra forma fazer modificações de software no sistema. Esta fase determinística, portanto, simplifica os algoritmos de calibração de nível de sistema mais amplos necessários para alcançar a sincronização de todos os canais na saída ou entrada para as redes front-end conectadas a esses ICs. Este artigo apresenta resultados experimentais que demonstram essa capacidade MCS ao usar uma plataforma de receptor / transmissor de 16 canais que consiste em vários CIs digitalizadores, fontes de relógio e interfaces digitais.

Diagrama de bloqueio do sistema de alto nível

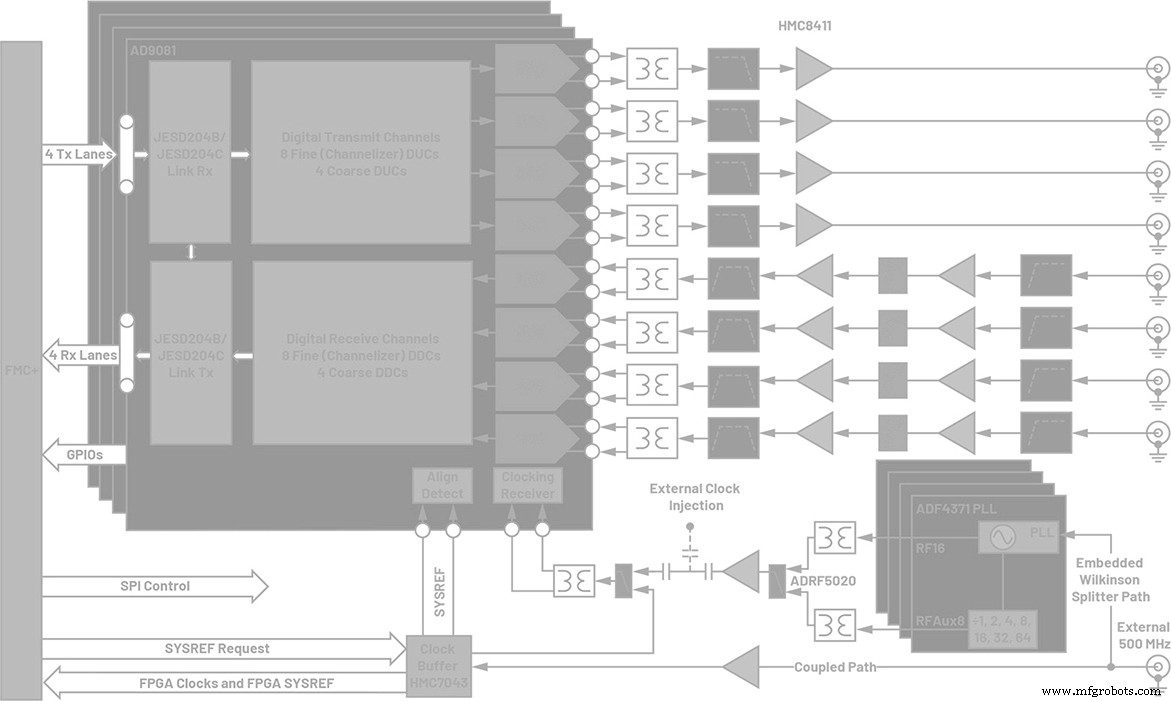

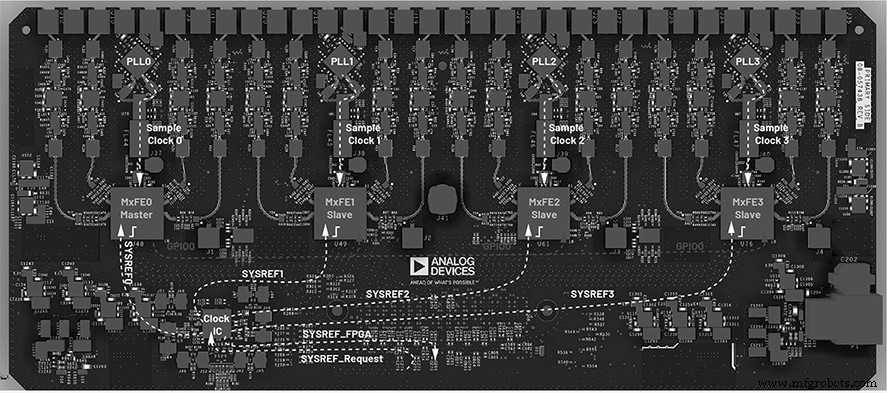

Um diagrama de blocos do sistema usado para este teste é mostrado na Figura 1 e consiste em quatro ICs DAC / ADC / DSP integrados, cada um composto por quatro DACs 12 GSPS, quatro ADCs 4 GSPS e 12 conversor digital ascendente (DUC) e 12 digitais blocos downconverter (DDC).

clique para ver a imagem em tamanho real

Figura 1. Um diagrama de blocos de alto nível do sistema usado para demonstrar MCS e algoritmos de calibração multicanal. (Fonte:Dispositivos analógicos)

Os DUCs / DDCs permitem a tradução de frequência e / ou interpolação / decimação dentro do domínio digital. Usando um único relógio de referência de 500 MHz injetado na placa, um buffer de relógio de referência bloqueada é então utilizado para gerar os sinais de referência do sistema necessários para MCS, bem como os relógios necessários para a interface digital para o processador de banda base (BBP). O sistema também contém quatro sintetizadores de loop de bloqueio de fase (PLL) separados que geram as fontes de 12 GHz necessárias para sincronizar cada CI de digitalização a partir da referência comum. Um front end de RF é conectado a cada saída / entrada do digitalizador, o que cria um sinal filtrado e amplificado de / para os conectores de RF lançados na borda. Uma solução completa de distribuição de energia é implementada. Todas as tensões necessárias para o sistema são geradas a partir de uma única fonte de 12 V. Todos os sinais de transmissão se propagam na parte inferior da placa, ao passo que todos os sinais de recepção se propagam na parte superior da placa para obter o melhor isolamento canal a canal.

Estrutura da árvore do relógio do Subarray

Como mencionado anteriormente, a árvore de relógio de subarray consiste em uma única fonte de referência de 500 MHz que é dividida e enviada para as entradas de referência de quatro CIs de sintetizador PLL separados, como mostrado acima na Figura 1. Este sinal de 500 MHz também é 10 dB acoplado, amplificado , e enviado para outro IC do buffer de relógio que é responsável por gerar as referências do sistema (SYSREFs) e os relógios BBP necessários para a interface digital. O objetivo desta árvore do relógio é triplo, pois:

- Permite atrasos SYSREF de canal individual para corrigir qualquer incompatibilidade de comprimento de rastreamento entre ICs.

- Permite o ajuste individual de fase de PLL / sintetizador e, portanto, garante a sincronização entre as respectivas fontes de relógio do digitalizador IC, para compensar quaisquer gradientes térmicos induzidos dentro do sistema.

- Permite que o usuário atinja os requisitos de configuração e retenção necessários para os ICs de digitalização.

Os CIs da árvore do relógio são escolhidos para demonstrar que várias anomalias no layout da placa podem ser corrigidas no software e / ou hardware com a ajuda de blocos de atraso digital e analógico presentes nesses chips. Em última análise, o resultado é uma árvore de clock que pode fornecer um pulso SYSREF para todos os ICs necessários dentro do mesmo ciclo de clock de amostra de cada um desses ICs.

Interface digital com processador de banda base

Cada um dos quatro CIs de digitalização estabelece uma interface de link digital JESD204B ou JESD204C com o BBP. 1,2 Essa interface é responsável por transmitir os códigos ADC e DAC pelos rastreamentos físicos (SERDES) de e para o BBP. O número de rastreamentos SERDES diferenciais usados nesta interface é denominado número de pistas (L) para este link. A resolução do bit do conversor enviada através do link é considerada como N '. O número de caminhos de dados canalizados, também conversores virtuais cunhados, é rotulado como M. Os resultados mostrados neste artigo usam um link JESD204C com M =16, N '=16, L =4 para os links do lado DAC e M =8 , N '=16, L =2 para os links do lado ADC.

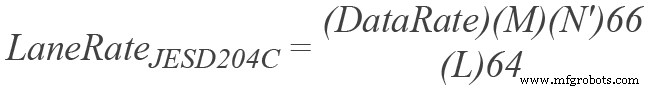

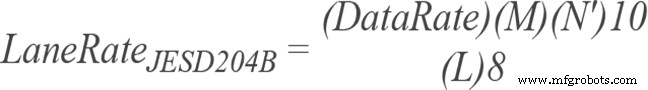

A taxa na qual os dados são transmitidos e recebidos entre o digitalizador IC e o BBP é denominada taxa de faixa. Os blocos DSP em silício (ou seja, os DDCs / DUCs) permitem que o usuário faça a amostragem dos digitalizadores em uma taxa diferente da taxa de dados enviada pelas vias físicas. Como tal, a taxa de faixa é dependente da taxa de dados digitalmente dizimada / interpolada para cada caminho de dados. Para este trabalho, uma taxa de dados I / Q de 250 MSPS foi utilizada. Para uma interface JESD204C, a taxa de faixa é definida como:

enquanto para uma interface JESD204B, a taxa de faixa é definida como:

Os resultados mostrados neste artigo usam uma taxa de faixa de 16,5 Gbps para os links JESD204C do lado ADC e DAC.

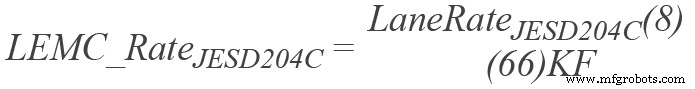

Cada link JESD204B / JESD204C pode ser estabelecido em diferentes subclasses. Essas subclasses são separadas com base na necessidade de sincronização multichip ou latência determinística. Para este trabalho, os dados mostrados usam um modo JESD204C Subclasse 1 e, portanto, utilizam sinais SYSREF para alinhar porções dos dados digitais transmitidos por meio de vários links presentes no sistema. Especificamente, neste modo JESD204C Subclasse 1, os sinais SYSREF são usados para alinhar o contador multibloco estendido local (LEMC), que transmite a uma taxa:

onde F é o número de octetos por quadro JESD por via e K é o número de quadros por multiframe único. Para este trabalho, F =8 e K =32 e, portanto, uma taxa LEMC de 7,8125 MSPS é usada. O conhecimento dessa taxa LEMC é importante, pois qualquer rotina MCS bem-sucedida precisará demonstrar que as frequências de RF que não são um múltiplo inteiro da taxa LEMC são capazes de atingir a fase de inicialização determinística.

Método de sincronização multichip

Dentro deste sistema, os ICs ADC / DAC integrados de banda larga fornecem circuitos MCS para permitir a fase determinística de energização em todos os canais de transmissão e recepção de RF, mesmo ao usar os blocos DUC / DDC DSP dentro do IC. Este recurso MCS permite que os usuários preencham uma tabela de pesquisa (LUT) durante uma calibração de fábrica para minimizar o tempo de inatividade operacional. Qualquer demonstração de MCS bem-sucedida deve ser capaz de fornecer fase determinística em todos os canais do sistema para cada tentativa de frequência de RF, gradiente térmico e ciclo de energia do sistema.

Os ICs ADC / DAC integrados contêm 12 blocos DUC e 12 blocos DDC, conforme mostrado acima na Figura 1. Cada um desses blocos contém um sub-bloco de interpolação (DUC) ou decimação (DDC) para alterar a taxa de dados do sinal de entrada digital DAC ou Sinal de saída digitalizado ADC, respectivamente. Também contido em cada DUC / DDC está um complexo oscilador numericamente controlado (NCO), que permite a tradução de frequência dentro do domínio digital. Cada um desses NCOs é capaz de ajuste de fase complexo em tempo real, de modo que o sinal digital entre o DAC / ADC e o BBP pode ser modificado para compensar várias incompatibilidades de comprimento de rastreamento SERDES.

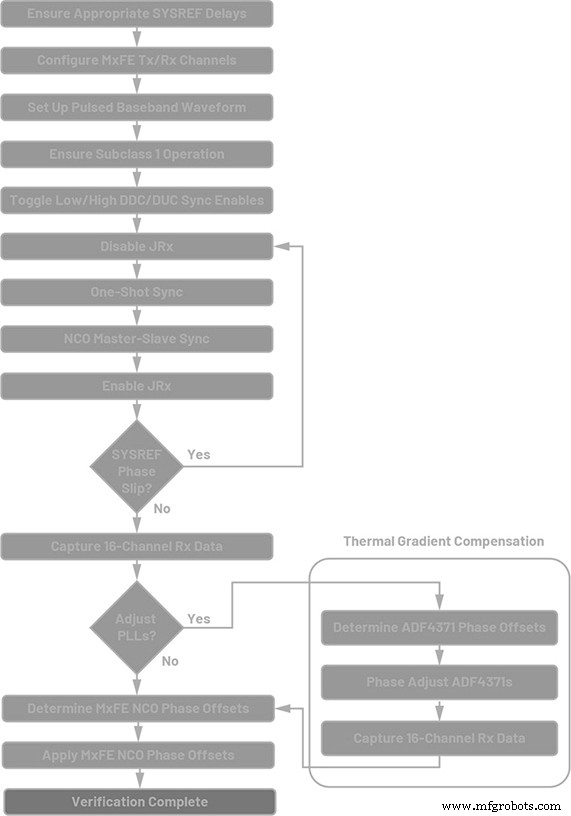

O recurso MCS para esses ICs ADC / DAC é responsável por atingir o determinismo de fase em todos os aspectos do caminho de dados do IC do digitalizador. O fluxo de trabalho para atingir o MCS é mostrado na Figura 2.

clique para imagem em tamanho real

Figura 2. O fluxo de trabalho MCS envolve recursos separados que alinham diferentes partes do caminho de dados. (Fonte:Dispositivos analógicos)

O algoritmo MCS pode ser dividido em duas funções separadas:

- Sincronização instantânea:este recurso é responsável por alinhar os dados de banda base enviados pelas vias físicas de todos os CIs digitalizadores dentro do sistema de subarray.

- Sincronização mestre-escravo NCO:este recurso é responsável por alinhar todos os NCOs em todos os CIs digitalizadores diferentes dentro do sistema de subarray.

O recurso de sincronização única requer primeiro que o usuário defina os parâmetros de link JESD (como M, N ', L, etc.) e, em seguida, configure a lógica de sincronização para qualquer média SYSREF desejada (se estiver usando pulsos SYSREF contínuos). Além disso, os atrasos LEMC desejados podem ser usados para forçar o LEMC a ser gerado em um certo atraso após a borda do SYSREF. Depois que isso for concluído, o usuário habilita o bit de sincronização one-shot em cada IC do digitalizador e, em seguida, solicita que os pulsos SYSREF sejam enviados para cada IC dentro do mesmo ciclo de clock, conforme mostrado na Figura 3.

clique para ver a imagem em tamanho real

Figura 3. O algoritmo MCS usa sinais SYSREF para implementar a sincronização one-shot e sinais GPIO para implementar a sincronização mestre-escravo NCO para atingir a fase determinística. (Fonte:Dispositivos analógicos)

Para este sistema, atrasos finos analógicos foram introduzidos no IC do buffer de clock para permitir SYSREFs síncronos para todos os ICs do digitalizador. Uma verificação subsequente pode ser executada para verificar o processo de sincronização one-shot realizado com sucesso, consultando os registros dentro de cada IC que fornecem informações sobre a relação de fase entre o sinal SYSREF e o limite LEMC de cada link de IC.

Uma vez que uma fase estável é medida (isto é, uma vez que o registrador de fase SYSREF-LEMC lê 0), o usuário então sabe que os LEMCs de todos os CIs digitalizadores estão alinhados e o usuário pode então prosseguir para o processo de sincronização mestre-escravo NCO. Para esta atividade, as subtarefas descritas para a sincronização única estão contidas em uma interface de programação de aplicativo (API) fornecida pelo fabricante do chip.

O recurso de sincronização mestre-escravo NCO primeiro atribui um dos ICs digitalizadores dentro do subarray para atuar como um chip mestre, conforme mostrado acima na Figura 3. Todos os outros digitalizadores são então considerados ICs escravos. O IC mestre é configurado de forma que o pino GPIO0 deste dispositivo seja configurado como uma saída e roteado para as redes GPIO0 dos três ICs digitalizadores escravos. As redes GPIO0 escravas são configuradas como entradas. O usuário pode então escolher disparar no pulso SYSREF, na borda de subida do LEMC ou na borda de descida do LEMC. Para os dados mostrados neste artigo, a borda de subida do LEMC é usada como fonte de disparo de sincronização mestre-escravo NCO e as redes GPIO são roteadas por meio do BBP em vez de localmente no subarray. Em seguida, os bits de sincronização DDC são alternados para baixo e depois para alto para armar o algoritmo de sincronização NCO do lado ADC. Da mesma forma, o bit de alinhamento do microprocessador é alternado para baixo e depois para alto para armar o algoritmo de sincronização NCO do lado DAC.

Quando este acionamento é solicitado, na próxima borda de subida do LEMC, o IC do digitalizador mestre ativa um sinal de saída mestre através de sua rede GPIO0. Este sinal se propaga para as entradas GPIO0 de cada um dos dispositivos escravos. Na próxima borda do LEMC, todos os CIs do digitalizador experimentam um algoritmo de reinicialização NCO. Depois disso, quaisquer pulsos LEMC são ignorados em relação ao algoritmo de sincronização mestre-escravo NCO. Tal como acontece com a sincronização one-shot, essas subtarefas de sincronização mestre-escravo NCO estão contidas nas funções de API para facilidade de uso do usuário.

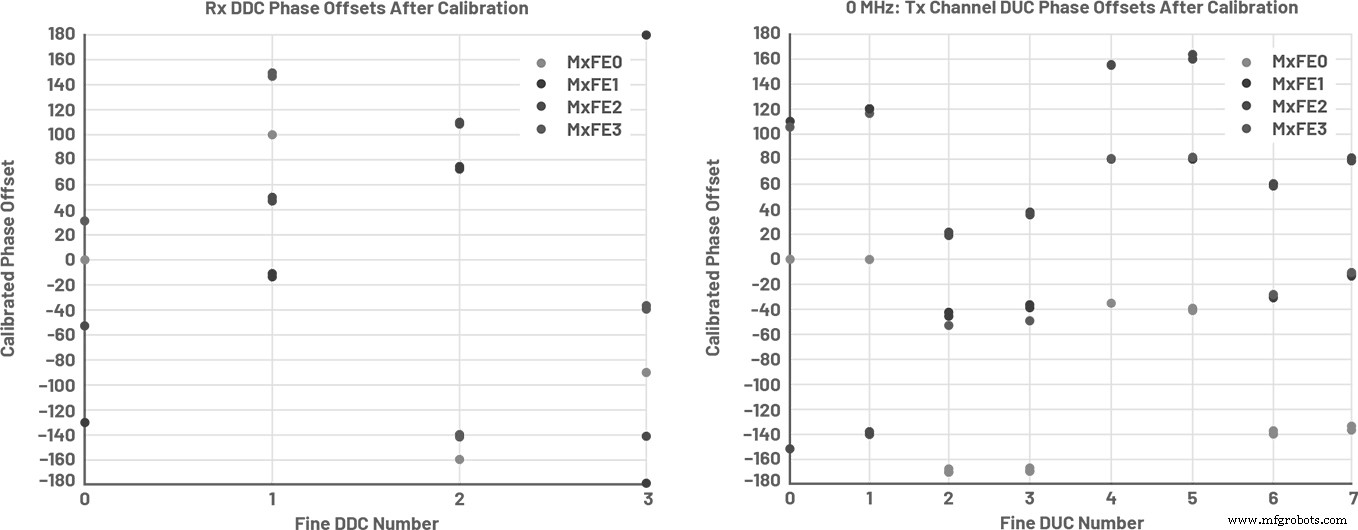

Usar os recursos de sincronização one-shot e NCO mestre-escravo alinha ambas as entradas para cada DDC / DUC de modo que o deslocamento da fase de saída de cada canal de recepção e transmissão seja repetido após vários ciclos de energia, conforme mostrado na Figura 4. Os dados na Figura 4 mostra os deslocamentos de fase calibrados em 100 ciclos de energia (indicados por vários pontos sólidos) para cada canalizador de recepção e transmissão enquanto o sistema está operando sob um gradiente térmico estático durante cada reinicialização.

clique para ver a imagem em tamanho real

Figura 4. Os DDCs finos de recepção (esquerda) e os DUCs finos de transmissão (direita) estão devidamente alinhados ao executar o algoritmo MCS. (Fonte:Dispositivos analógicos)

Como pode ser visto a partir dos vários pontos presentes nesta figura, os pontos de cada cor para um determinado DDC / DUC são todos fortemente agrupados na mesma posição após os ciclos de energia, retratando assim a fase determinística para aquele canal específico. Para os dados neste teste, todos os oito DUCs do canalizador foram usados no lado da transmissão, enquanto apenas quatro dos oito DDCs do canalizador foram usados. No entanto, foi confirmado que, de fato, todos os oito DDCs do canalizador fornecem fase determinística ao usar o algoritmo MCS também.

A emissão desse algoritmo na inicialização estabelece uma fase determinística para cada canal se os relógios de amostra do sintetizador PLL e os CI SYSREFs de relógio mantiverem a mesma relação de fase na inicialização. No entanto, qualquer sistema passará por gradientes térmicos, o que pode resultar em desvio do clock do PLL e que pode resultar em uma fase de inicialização diferente se não for compensado. Para compensar o desvio do gradiente térmico dentro do sistema, esta plataforma utiliza ajustes de fase do sintetizador PLL.

Na próxima parte desta série de artigos, exploraremos os ajustes de fase do sintetizador PLL, escalabilidade para múltiplos subarrays e algoritmos de calibração em nível de sistema.

Referências

1 Del Jones. “Primer JESD204C:O que há de novo e para você - Parte 1.” Diálogo analógico , Vol. 53, No. 2, junho de 2019.

2 Del Jones. “JESD204C Primer:O que há de novo e disponível para você - Parte 2.” Diálogo analógico , Vol. 53, No. 3, julho de 2019.

Integrado

- Mudança de fase

- Fase AC

- Rotação de fase

- C# usando

- MACOM estreia novo amplificador de ruído de fase ultrabaixa

- A Keysight lança um novo sistema de teste de ruído de fase

- Usar vários chips de inferência exige um planejamento cuidadoso

- Como gerar uma forma de onda de alta precisão usando um DAC e um PCB personalizado

- Gerador de Relógio Verilog

- Usando uma fresadora como torno