Design integrado com FPGAs:Implementação

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas:

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas:1:Recursos de hardware

2:Linguagens de implementação

3:Processo de desenvolvimento

4:Construindo um projeto

5:Implementação (este artigo)

Adaptado de Architecting High-Performance Embedded Systems, de Jim Ledin.

Testando o comportamento lógico

É importante testar o comportamento da lógica usando simulação antes de tentar executá-la no FPGA. Isso ocorre porque é muito mais fácil detectar e corrigir problemas no ambiente de simulação do que com a lógica em execução dentro do FPGA. As ferramentas de simulação do Vivado fazem um ótimo trabalho na representação do comportamento do circuito:

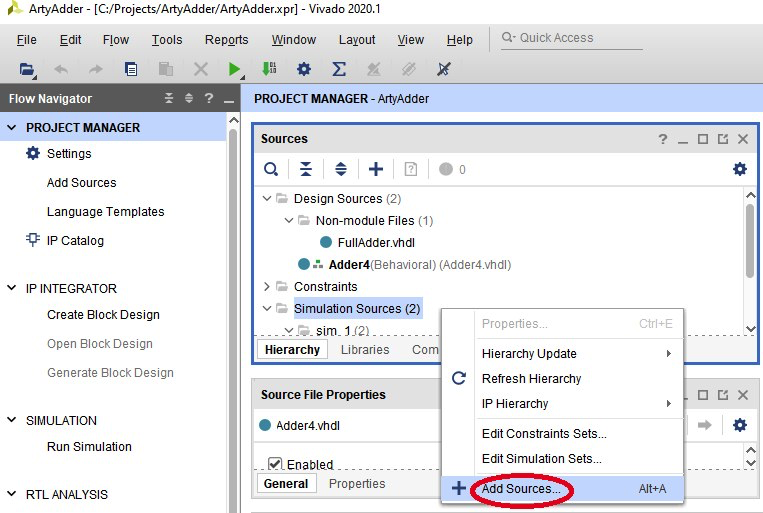

- Em Fontes subjanela, clique com o botão direito em Fontes de simulação e selecione Adicionar fontes… :

Figura 4.18 - Adicionar fontes… seleção de menu para fontes de simulação

- Em Adicionar fontes caixa de diálogo, certifique-se de Adicionar ou criar fontes de simulação for selecionado e clique em Avançar .

- Em Adicionar ou criar fontes de simulação caixa de diálogo, clique em Criar arquivo .

- Insira o nome do arquivo vhdl e clique em OK .

- Clique em Concluir para dispensar o Adicionar ou Criar Fontes de Simulação caixa de diálogo e clique em OK no Definir Módulo caixa de diálogo e clique em Sim quando perguntado se você tem certeza de que deseja usá-los

- Clique duas vezes em Adder4 TestBench (Behavioral) (Adder4TestBench.vhdl) em Fontes de simulação . Exclua o conteúdo preenchido automaticamente do vhdl janela do editor e insira o seguinte código no Adder4TestBench.vhdl editor:

IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; entidade ADDER4_TESTBENCH isend entidade ADDER4_TESTBENCH; arquitetura BEHAVIORAL de ADDER4_TESTBENCH é o componente ADDER4 é a porta (A4:em std_logic_vector (3 downto 0); B4:em std_logic_ outvector (3 downd 0); C_OUT4:out std_logic); componente final; sinal a:std_logic_vector (3 até 0); sinal b:std_logic_vector (3 até 0); sinal s:std_logic_vector (3 até 0); sinal c_out:std_logic; sinal esperado_sum5:não assinado (4 até 0); sinal esperado_sum4:não assinado (3 até 0); sinalesperado_c:std_logic; erro de sinal:std_logic; iniciar TESTED_DEVICE:mapa da porta ADDER4 (A4 => a, B4 => b, SUM4 => s, C_OUT4 => c_out); TESTE:início do processo - Teste todas as combinações de dois adendos de 4 bits (256 testes no total) para a_val em 0 a 15 loop para b_val em 0 a 15 loop - Defina as entradas para o componente ADDER4 a <=std_logic_vector (to_unsigned ( a_val, a'length)); b <=std_logic_vector (to_unsigned (b_val, b'length)); aguarde 1 ns; - Calcula a soma de 5 bits dos dois valores de 4 bits expect_sum5 <=unsigned ('0' &a) + unsigned ('0' &b); aguarde 1 ns; - Divida a soma em uma saída de 4 bits e um bit de transporte, soma_esperada4 <=soma_esperada5 (3 até 0); esperado_c <=esperado_sum5 (4); aguarde 1 ns; - O sinal de 'erro' só irá para 1 se ocorrer um erro se ((sem sinal (s) =sem sinal (valor_esperado4)) e (c_out =esperado_c)) então erro <='0'; senão erro <='1'; fim se; - Cada passagem pelo loop interno leva 10 ns e espera 7 ns; loop final; loop final; esperar; TESTE do processo final; arquitetura final COMPORTAMENTE; Este código exercita a funcionalidade do somador de 4 bits, apresentando todas as combinações de números de 4 bits para cada um dos A4 e B4 entradas para o Adder4 componente. Ele compara o SUM4 e C_OUT4 saídas do Adder4 componente para valores calculados independentemente para as mesmas entradas. Após cada operação de adição, o erro o sinal é definido como 0 se o Adder4 as saídas corresponderam aos valores esperados ou está definido como 1 se houver uma incompatibilidade.

O código em Adder4TestBench.vhdl assemelha-se ao código de software tradicional na forma como usa loops for aninhados para aplicar todas as combinações de entrada de teste ao Adder4 componente em teste. O código que executa testes no modo de simulação não é sintetizável, o que significa que não representa puramente um circuito lógico de hardware e é capaz de operações tradicionais semelhantes a software, como a execução iterativa de para rotações.

No entanto, como em circuitos físicos, os sinais com valores atribuídos no código da bancada de teste usando o operador <=não podem ser usados no mesmo instante em expressões subsequentes. Isso ocorre porque o ambiente de simulação representa os efeitos do mundo real do atraso de propagação, o que é significativo mesmo em dispositivos FPGA minúsculos. Os três aguardam 1 ns ; as instruções no código da bancada de teste pausam as operações do circuito para permitir o retardo de propagação. Esses atrasos de 1 ns fornecem tempo para os valores do sinal calculados antes da esperar declaração para propagar para que possam ser usados na declaração a seguir. A última espera por 7 ns ; instrução no loop interno é uma pausa que nos permite ver claramente os resultados de cada iteração dos loops de simulação na exibição do traço do sinal.

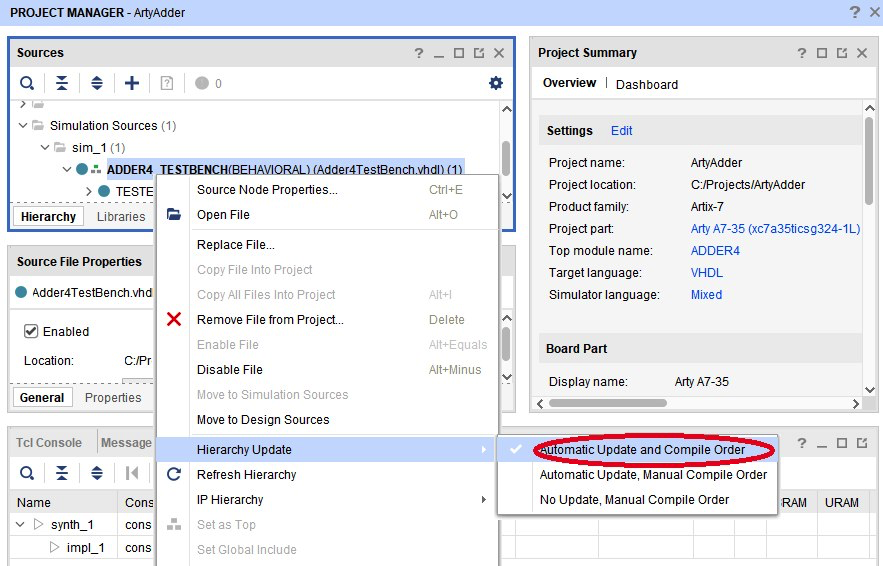

- Clique com o botão direito em Adder4 TestBench (Behavioral) (Adder4TestBench.vhdl) em Fontes de simulação e selecione Atualização automática e pedido de compilação . Isso define ADDER4_TESTBENCH como o objeto de nível superior para a execução da simulação:

Figura 4.19 - Seleção de menu para definir atualização automática e ordem de compilação

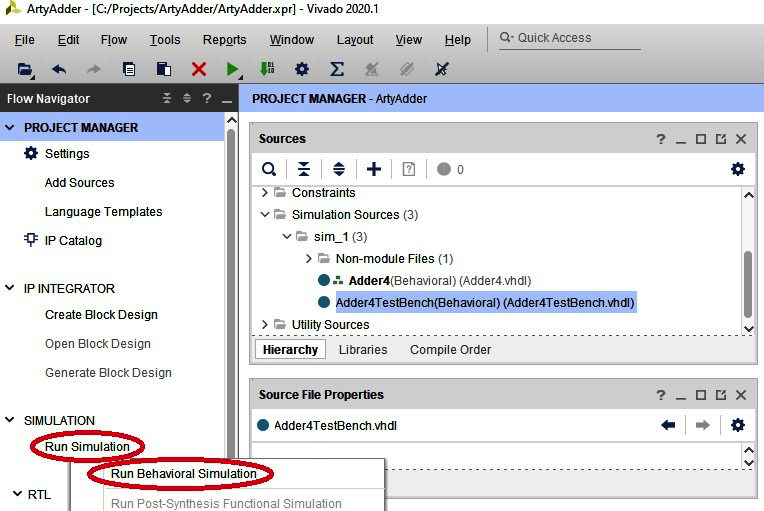

- Clique em Executar simulação e, em seguida, Executar Simulação Comportamental no Flow Navigator janela para entrar no modo de simulação. Se você ainda não salvou os arquivos do editor, será solicitado que o faça. Clique em Salvar . A simulação será executada:

Figura 4.20 - Seleção do menu Executar Simulação Comportamental

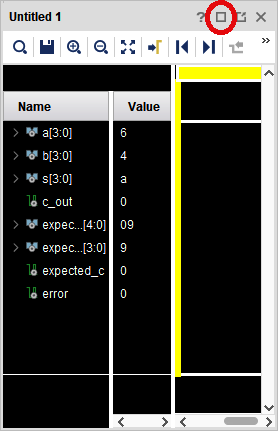

- Quando a SIMULAÇÃO a janela abrir, clique no botão maximizar na janela de saída da simulação com o título Sem título 1 :

Figura 4.21 - Janela de resultados da simulação

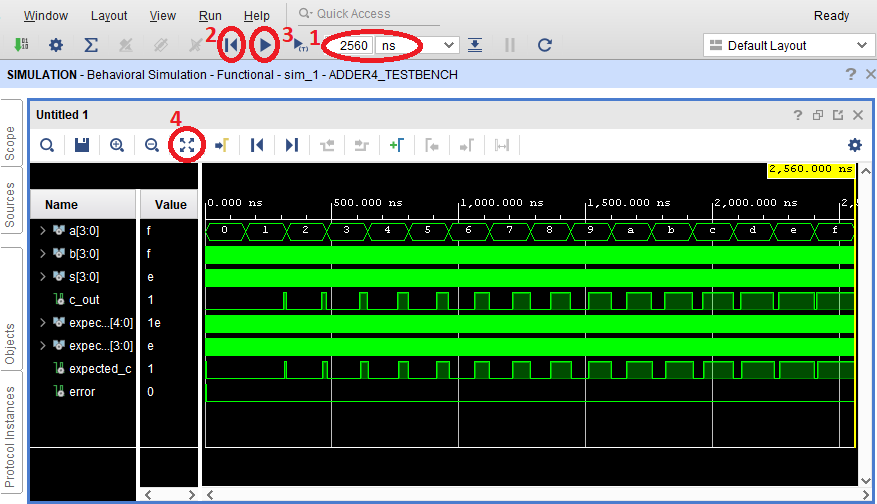

O tempo total simulado de cada passagem pelo loop interno é de 10 ns. Porque há 256 passagens pelo loop em Adder4TestBench.vhdl , o tempo para executar a simulação é 2560 ns.

- Defina o tempo de execução da simulação para 2560 ns na barra de ferramentas superior ( etapa 1 na figura a seguir), pressione o botão de reiniciar apontando para a esquerda ( etapa 2 ) e, em seguida, pressione o botão voltado para a direita para executar a simulação por 2560 ns ( etapa 3 ) e, por fim, pressione o botão Ajuste de zoom botão ( passo 4 ) para dimensionar o intervalo de dados de saída da simulação para caber na janela:

Figura 4.22 - Resultados da simulação do início ao fim da execução

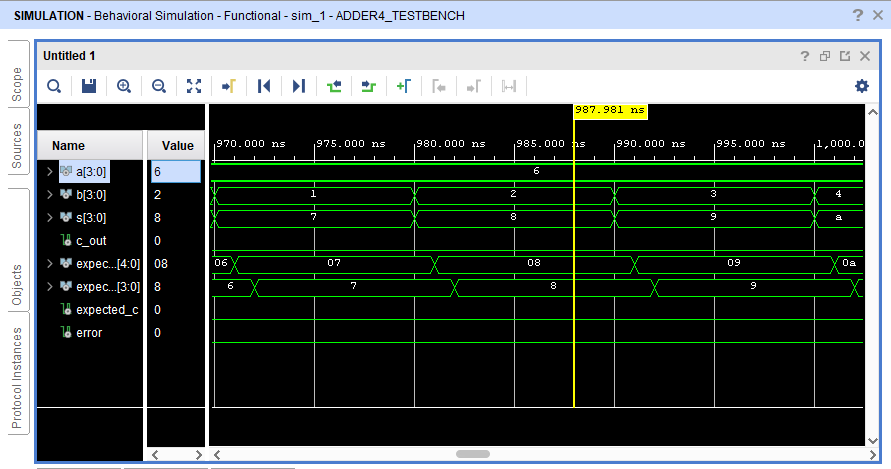

Você pode usar os ícones de ampliação para ampliar qualquer ponto do traço e observar os resultados de cada operação de adição realizada durante o teste. Por exemplo, a figura a seguir mostra que os valores decimais 6 e 2 foram adicionados para produzir o resultado 8 com um transporte de 0. Esses valores correspondem aos valores esperados, o que causou o erro deve ser definido como 0. O erro sinal é 0 para todos os 256 casos de teste, indicando que nosso circuito lógico passou em todos os testes:

Figura 4.23 - Visão ampliada dos resultados da simulação

- Feche o modo de simulação clicando no X no azul SIMULAÇÃO barra acima do rastreamento de dados Clique em OK quando perguntado se deseja fechar a simulação.

Tendo passado no teste comportamental, definiremos os sinais de E / S usados no projeto.

Definindo sinais de E / S

Nosso próximo passo é conectar as entradas e saídas do nosso circuito aos dispositivos de hardware na placa Arty. As entradas serão as chaves e botões da placa e as saídas serão LEDs.

As etapas a seguir criarão um arquivo de restrições que descreve os pinos de E / S que usaremos no dispositivo FPGA e as funções conectadas a esses pinos na placa Arty. Os arquivos de restrição têm a extensão xdc:

- Em Fontes subjanela, clique com o botão direito em Restrições e selecione Adicionar fontes… .

- Em Adicionar fontes caixa de diálogo, certifique-se de Adicionar ou criar restrições for selecionado e clique em Avançar .

- Em Adicionar ou criar restrições caixa de diálogo, clique em Criar arquivo .

- Digite o nome do arquivo Arty-A7-100.xdc (ou Arty-A7-35.xdc se apropriado para o seu dispositivo) e clique em OK .

- Clique em Concluir para dispensar o Adicionar ou Criar Restrições

- Expanda as restrições árvore de origem e clique duas vezes em Arty-A7-35.xdc .

- A Digilent fornece arquivos de restrição pré-preenchidos para as placas Arty A7 Visite https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-35-Master .xdc e copie todo o conteúdo da janela do navegador para a janela do editor Arty-A7-35.xdc no Vivado. Se apropriado para o seu dispositivo, use o arquivo em https://raw.githubusercontent.com/Digilent/digilent-xdc/master/Arty-A7-100-Master.xdc em vez disso.

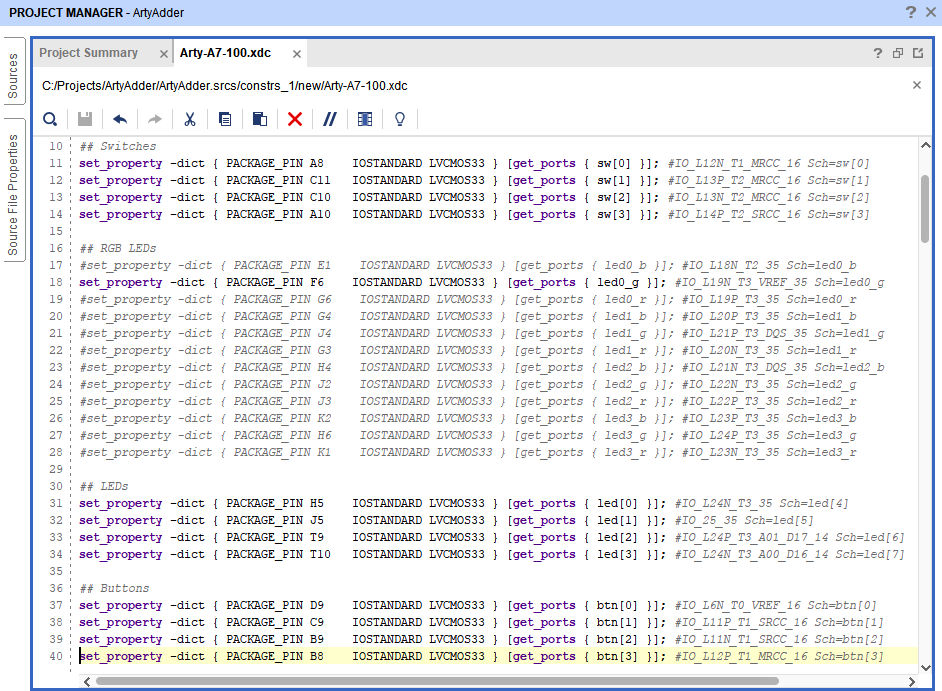

- Todos os pinos de I / O são comentados no arquivo de restrições por Descomente as linhas apropriadas no arquivo removendo o caractere # do início de cada linha. Usaremos os distintivos listados nas seções a seguir no Arty- A7-100.xdc arquivo: Switches , RGB LEDs (mas apenas led0_g , o primeiro LED verde), LEDs e Botões . A figura a seguir mostra essas linhas após terem sido descomentadas:

Figura 4.24 - Janela do editor de restrições

Na próxima seção, criaremos um arquivo VHDL de nível superior que faz a interface do código do somador com os dispositivos de E / S.

Criação de um arquivo VHDL de nível superior

Em seguida, criaremos um arquivo VHDL de nível superior que conecta nosso componente adicionador de 4 bits aos sinais de E / S da placa correspondentes:

- Em Fontes subjanela, clique com o botão direito em Design Sources e selecione Adicionar fontes… .

- Em Adicionar fontes caixa de diálogo, certifique-se de Adicionar ou criar fontes de design for selecionado e clique em Avançar .

- Em Adicionar ou criar fontes de design caixa de diálogo, clique em Criar arquivo .

- Insira o nome do arquivo vhdl e clique em OK .

- Clique em Concluir para dispensar o Adicionar ou criar fontes de design caixa de diálogo e clique em OK no Definir Módulo caixa de diálogo e clique em Sim quando perguntado se você tem certeza de que deseja usá-los

- Clique duas vezes em vhdl em Fontes de Design . Exclua o conteúdo preenchido automaticamente de ArtyAdder.vhdl janela do editor e insira o seguinte código no ArtyAdder.vhdl editor:

- Carrega a biblioteca de bibliotecas padrão IEEE; use IEEE.STD_LOGIC_1164.ALL; a entidade ARTY_ADDER é a porta (sw:em STD_LOGIC_VECTOR (3 downto 0); btn:in STD_LOGIC_VECTOR (3 downto 0); led:out STD_LOGIC_VECTOR (3 downto 0); led0_g:out STD_LOGIC); ARTY_ADDER; arquitetura BEHAVIORAL de ARTY_ADDER é - Referência a definição anterior do componente adicionador de 4 bits ADDER4 é porta (A4:em std_logic_vector (3 downto 0); B4:in std_logic_vector (3 downto 0); SUM4:out std_logic_vector (3 até 0); C_OUT4:out std_logic); componente final; início ADDER:mapa da porta ADDER4 (A4 => sw, B4 => btn, SUM4 => led, C_OUT4 => led0_g); arquitetura final COMPORTAMENTO;

Este código mapeia os nomes dos sinais para os dispositivos de E / S nomeados em Arty-A7-100.xdc como sw (4 interruptores), btn (4 botões), led (4 LEDs de cor única) e led0_g (o canal verde do primeiro LED multicolorido) para o ADDER4 entradas e saídas.

Embora VHDL não faça distinção entre maiúsculas e minúsculas, o processamento de xdc arquivos de restrição no Vivado diferenciam maiúsculas de minúsculas. O caso usado em nomes de dispositivos de E / S definidos no xdc arquivo deve ser idêntico quando referenciado em um arquivo VHDL. Especificamente, os nomes dos sinais de E / S em VHDL devem estar em minúsculas neste arquivo porque estão em minúsculas no arquivo de restrições.

Agora estamos prontos para sintetizar, implementar e programar nosso design para a placa Arty.

Synthesizing and implementing the FPGA bitstream

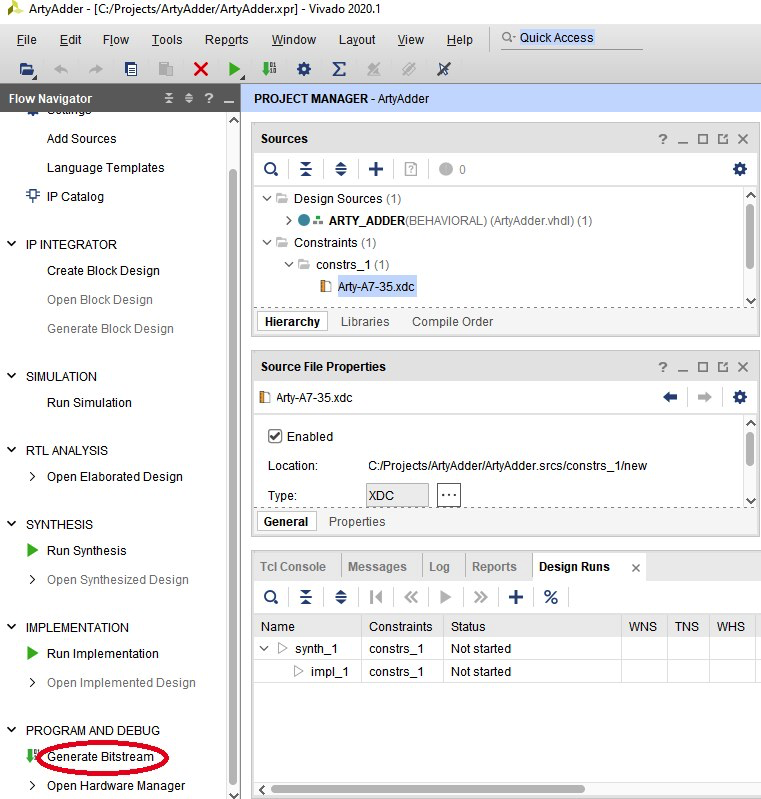

Alternatively, you can select Generate Bitstream and Vivado will perform all of the required steps, including synthesis, implementation, and bitstream generation without further user intervention. If a fatal error occurs, the process will stop and error messages will be displayed. Perform the following steps to generate the bitstream:

- Click Generate Bitstream to start the build You may be asked if you want to save text editors. Click Save . You may be informed that there are no implementation results available and asked if it is OK to launch synthesis and implementation. Click Yes :

Figure 4.25 – Generate Bitstream menu selection

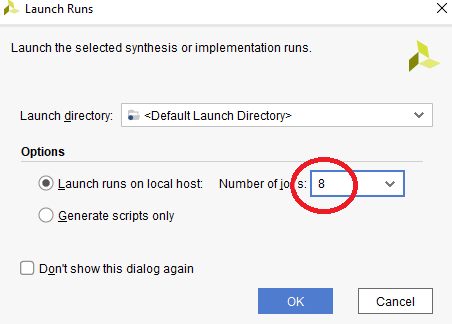

- The Launch Runs dialog will then You can select a value for Number of jobs up to the number of processor cores in your computer. Using more cores makes the process go faster, but it can bog down your machine if you want to continue using it during a lengthy build process. Click OK to start the build:

Figure 4.26 – Launch Runs dialog

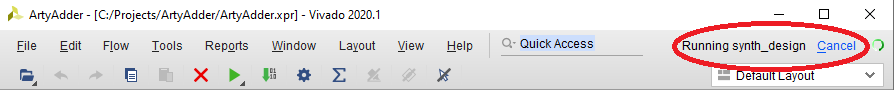

- During the build process, Vivado will display the status in the upper-right corner of the main window. If necessary, you can cancel the build process by clicking Cancel next to the status display:

Figure 4.27 – Compilation status display

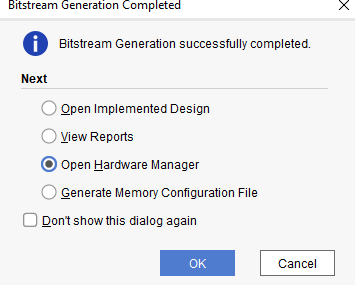

- When the build process completes, assuming there were no fatal errors, a Bitstream Generation Completed dialog will Although other options are offered, we will proceed directly to downloading the bitstream to the Arty board. Select Open Hardware Manager and click OK :

Figure 4.28 – Bitstream Generation Completed dialog

Next, we will download the bitstream into the FPGA.

Downloading the bitstream to the board

Perform the following steps to download the bitstream to an Arty A7 board:

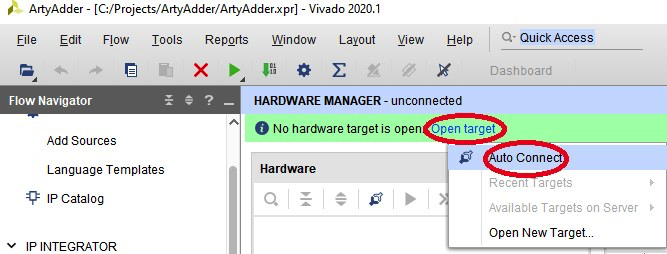

- The HARDWARE MANAGER dialog will appear and indicate No hardware target is open .

- Connect your Arty A7-35 or A7-100 board to the computer with a USB Wait a few seconds for the board to be recognized, then click Open target , then Auto Connect :

Figure 4.29 – Open target and Auto Connect selections

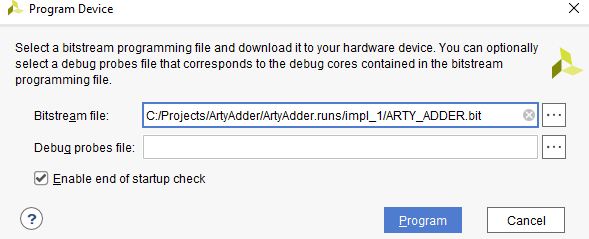

- After a few seconds, Vivado should indicate that the board is connected. Click Program device to download the FPGA bitstream to the Arty You will be prompted to select a bitstream file. If you’ve used the same directory structure as this example, the file will be located at C:/Projects/ArtyAdder/ ArtyAdder.runs/impl_1/ARTY_ADDER.bit :

Figure 4.30 – Program Device dialog

- Click Program to download the program to the FPGA device and start it

- You can now test the operation of the program with the Arty I/O Place all of the four switches in the off position (move the switches toward the adjacent board edge) and do not press any of the four pushbuttons. All of the four green LEDs should be off.

- If you turn on any individual switch or press any one pushbutton, the corresponding green LED should turn on. Turning on any combination of switches while pressing any number of pushbuttons will add the corresponding 4-bit numbers and light the LEDs with the If there is a carry (for example, turn on SW3 and press BTN3 simultaneously), the green carry LED will illuminate.

The programming process performed here stored the program in FPGA RAM. If you cycle power on the FPGA board, you will need to repeat the programming process to reload the program. Alternatively, you can store the FPGA configuration file in onboard flash memory as described in the following section.

Programming the bitstream to onboard flash memory

To configure the FPGA each time power is applied to the Arty board, the FPGA configuration file must be stored to flash memory on the board. If the MODE jumper is installed, the FPGA will attempt to download a configuration file from onboard flash memory at power-on. This memory is located in a separate chip adjacent to the Artix-7 FPGA. Follow these steps to program the configuration file to flash memory:

- Install the MODE jumper on the Arty board if it is not already in

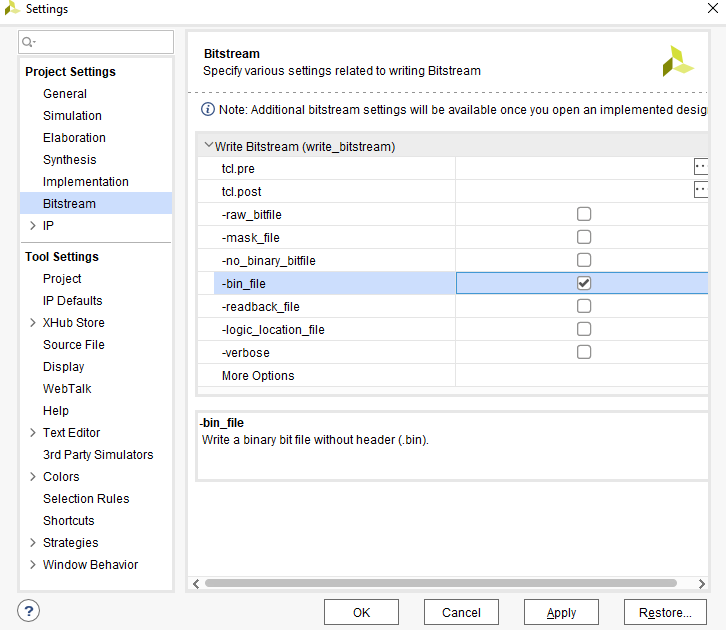

- Right-click Generate Bitstream and select Bitstream Settings… .

- In the Settings dialog, check the box next to -bin_file and click OK :

Figure 4.31 – Bitstream settings dialog

- In the main Vivado dialog, click Generate Bitstream and repeat the bitstream generation process. Click Cancel when the Bitstream Generation Completed dialog

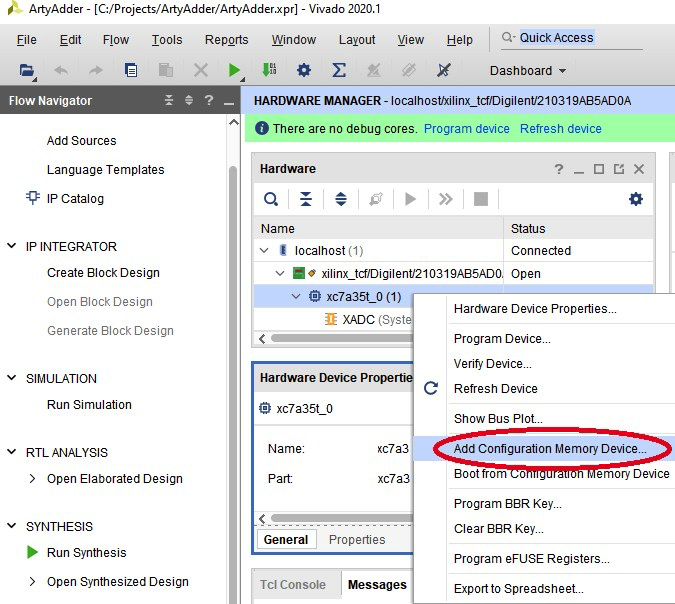

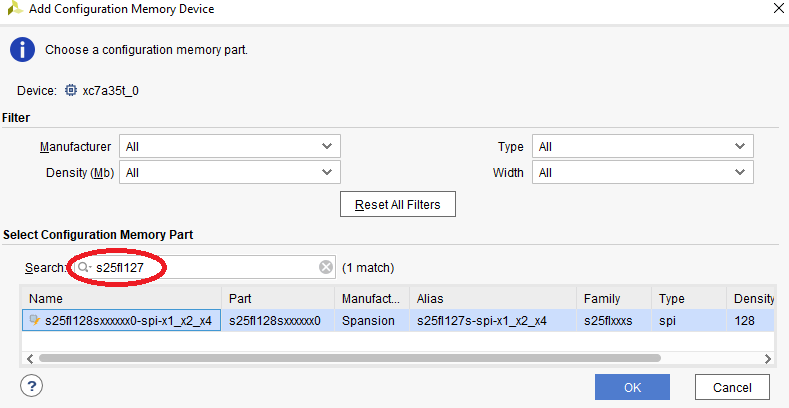

- In the Hardware dialog, right-click the FPGA part number (xc7a100t_0 ) and select Add Configuration Memory Device… :

Figure 4.32 – Add Configuration Memory Device… menu selection

- Type s25fl127 into the Search This should bring up one matching part number. Select the part and click OK :

Figure 4.33 – Add Configuration Memory Device dialog

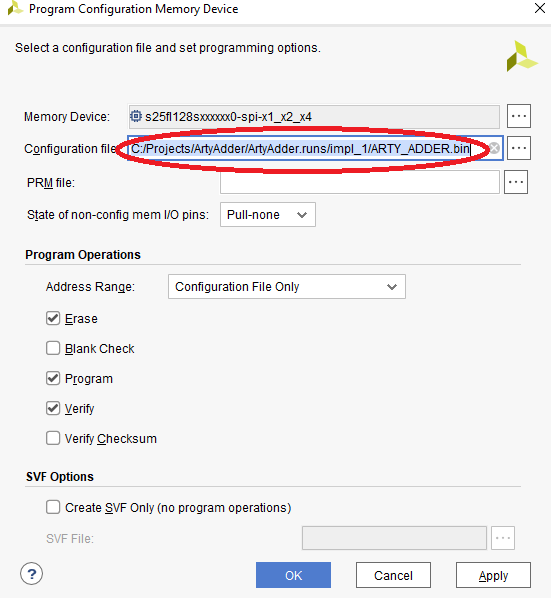

- You will be presented with a dialog asking Do you want to program the configuration memory device now? Click OK .

- This will bring up a Program Configuration Memory Device dialog requesting the configuration filename. Click the … button to the right of Configuration file and select C:/Projects/ArtyAdder/ArtyAdder.runs/impl_1/ARTY_ADDER.bin. Click OK :

Figure 4.34 – Program Configuration Memory Device dialog

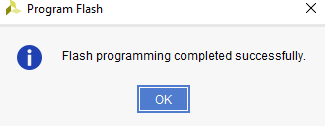

- The programming process will take several seconds to You should receive a message indicating success after the file has been programmed into the board flash memory:

Figure 4.35 – Program Flash complete dialog

After this, each time you cycle the board power, the 4-bit adder program will load and run. It will take a long time for the program to load with the settings that we used for configuration file loading. To avoid waiting for the FPGA to load the program, you can improve the speed of configuration file loading by performing the following steps:

- Select Open Synthesized Design in Flow Navigator .

- In the Vivado main menu, select Tools/Edit Device Properties… .

- In the General tab, set Enable Bitstream Compression to TRUE .

- In the Configuration tab, set Configuration Rate (MHz) to 33, then click OK .

- Generate the bitstream again, and program the flash memory as described You will need to remove the configuration memory device and add it back again to display the option for reprogramming.

- Close Hardware Manager .

- Unplug the Arty board USB cable and plug it in The program should begin running virtually instantaneously at power-on.

This section presented an example of simple combinational logic interacting with signals on the FPGA I/O pins. The intent here has been to familiarize you with the Vivado

tool suite and to demonstrate how the tools are used to perform a complete FPGA development cycle.

Summary

This chapter began with a discussion on the effective use of FPGAs in real-time embedded system architectures and continued with a description of standard FPGA devices and the low-level components they contain. The range of FPGA design languages, including HDLs, block diagram methods, and popular software programming languages such as C/C++, was introduced. An outline of the FPGA development process was presented. The chapter concluded with a complete example of an FPGA development cycle, starting with a statement of requirements and ending with a functional system implemented on a low-cost FPGA development board.

Having completed this chapter, you should know how FPGAs can be applied effectively in real-time embedded system architectures and understand the components inside an FPGA integrated circuit. You have learned about the programming languages used in the design of FPGA algorithms, the steps in the FPGA development cycle, and understand the sequence of steps in the FPGA development process.

The next chapter will expand on the FPGA development process to provide a complete approach to architecting real-time embedded systems containing FPGAs. It will also begin the development of a prototype high-performance embedded system, a digital oscilloscope, that will serve as an example for the following chapters.

Reprinted with permission from Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin is the CEO of Ledin Engineering, Inc. Jim is an expert in embedded software and hardware design, development, and testing. He is also accomplished in embedded system cybersecurity assessment and penetration testing. He has a B.S. degree in aerospace engineering from Iowa State University and an M.S. degree in electrical and computer engineering from Georgia Institute of Technology. Jim is a registered professional electrical engineer in California, a Certified Information System Security Professional (CISSP), a Certified Ethical Hacker (CEH), and a Certified Penetration Tester (CPT).

Jim Ledin is the CEO of Ledin Engineering, Inc. Jim is an expert in embedded software and hardware design, development, and testing. He is also accomplished in embedded system cybersecurity assessment and penetration testing. He has a B.S. degree in aerospace engineering from Iowa State University and an M.S. degree in electrical and computer engineering from Georgia Institute of Technology. Jim is a registered professional electrical engineer in California, a Certified Information System Security Professional (CISSP), a Certified Ethical Hacker (CEH), and a Certified Penetration Tester (CPT). Related Contents:

- Embedded design with FPGAs:Hardware resources

- Embedded design with FPGAs:Implementation languages

- Embedded design with FPGAs:Development process

- Open-source tools help simplify FPGA programming

- Implementing floating-point algorithms in FPGAs or ASICs

- Leveraging FPGAs for deep learning

- Software tools migrate GPU code to FPGAs for AI applications

For more Embedded, subscribe to Embedded’s weekly email newsletter.

Integrado

- O que é design de sistema incorporado:etapas no processo de design

- Concluindo as peças impressas em 3D com… giz de cera?

- Entrevista com especialista:Tecnólogo-chefe da ANSYS para obter sucesso na impressão em Metal 3D com simulação

- Transformando big data em dados inteligentes com IA incorporado

- Desafios de implementação da porta USB Type-C e soluções de design

- As principais tendências da indústria estão moldando o design incorporado

- Plataforma de código aberto visa IoT com Linux incorporado

- Clientron:terminal PDV multifuncional com impressora integrada

- O kit de design mede a pressão arterial com sensor óptico

- All in com aditivo