Compreendendo a ativação de DSP usando o MCU i.MX RT500 Crossover da NXP

Saiba mais sobre programas multithread, desenvolvimento de aplicativos usando o sistema operacional em tempo real XOS, compartilhamento de recursos com semáforos e como a família i.MX RT500 da NXP de microcontroladores ajudam os engenheiros a projetar dispositivos inteligentes habilitados para DSP.

Os dispositivos de consumo inteligentes de hoje requerem componentes capazes de processar grandes quantidades de dados para atender às demandas de vários aplicativos de segurança e processamento de sinal. Esses componentes (incluindo microcontroladores) devem ser capazes de processar esses dados de forma rápida e eficiente, exigindo processadores de sinais digitais altamente otimizados.

Este artigo apresenta alguns recursos do processador de áudio Cadence® Tensilica® Fusion F1, um coprocessador designado que auxilia a CPU principal do MCU i.MX RT500 na execução de cálculos de processamento de sinal.

Conceitos básicos de programas multi-threaded

À primeira vista, o hardware de processamento moderno cria a ilusão de que executa muitos threads simultaneamente. Na realidade, um único núcleo da CPU cuida de um único thread por vez. Quando o número de threads excede o número de núcleos de CPU disponíveis, um sistema operacional é necessário para agendar os threads.

O sistema operacional precisa acompanhar todos os threads iniciados e seu estado, e atribui slots de tempo de CPU a cada thread para que vários aplicativos possam ser executados de forma eficiente e aparentemente em paralelo.

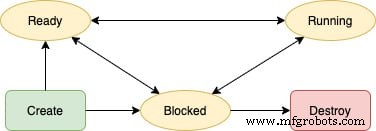

Figura 1. Os diferentes estados de um tópico

O programador do sistema operacional mantém uma fila para threads que estão prontos para serem executados, uma fila para bloquear threads e precisa armazenar informações sobre as threads que estão em execução para realizar a distribuição justa do tempo de CPU:

- Threads na fila pronta estão atualmente esperando que o sistema operacional os programe na CPU. Normalmente, o agendador do SO conhece diferentes níveis de prioridade, que ele considera ao escolher o próximo thread a ser executado na CPU.

- Threads de bloqueio aguardam que um evento externo aconteça, por exemplo, uma interrupção de pino ou uma operação de arquivo. Agendar esses threads significaria que a CPU desperdiçaria energia de processamento esperando que uma operação externa fosse concluída. Assim que a operação de bloqueio termina, o thread de espera associado retorna ao final da fila de espera.

- Os threads atualmente em execução podem realizar uma operação de bloqueio ou o sistema operacional pode agendar um thread diferente de acordo com sua estratégia de agendamento. Nesse caso, o agendador moverá o encadeamento atualmente em execução para a lista de encadeamentos bloqueados ou para o fim da fila pronta, respectivamente.

Os desenvolvedores de sistema operacional podem escolher implementar uma ou várias estratégias de agendamento diferentes, dependendo dos requisitos exatos. Além do agendamento, a sincronização e a comunicação entre diferentes threads são outros aspectos essenciais dos sistemas multi-threaded.

Condições e eventos no XOS

As condições no XOS RTOS (sistema operacional em tempo real) permitem que os desenvolvedores instruam um thread a bloquear até que uma condição especificada se torne verdadeira. O sistema avalia cada condição usando uma função de condição definida pelos desenvolvedores do aplicativo. O XOS executa uma avaliação sempre que outro thread sinaliza o objeto de condição ou quando um manipulador de interrupção dispara um.

Os eventos no XOS, por outro lado, representam um grupo de bits que os desenvolvedores podem utilizar para sincronizar diferentes threads ou threads e manipuladores de interrupção. O XOS permite que vários threads esperem por eventos e os sinalizem simultaneamente.

Interrupções no XOS

O XOS oferece um rico conjunto de recursos para lidar com interrupções e exceções que ocorrem durante o tempo de execução. Os mecanismos de interrupção dentro do XOS oferecem aos programadores a flexibilidade de instalar manipuladores personalizados, garantindo que o envio de interrupções funcione o mais rápido possível no sistema. O XOS também oferece suporte ao tratamento de interrupções aninhadas, o que significa que o SO pausa o tratador de interrupções atual se ocorrer uma interrupção de prioridade mais alta. Assim que o sistema termina de lidar com a interrupção de alta prioridade, ele retoma automaticamente o atendimento às interrupções de baixa prioridade.

Threads também podem ter serviços relacionados ao tempo, como atrasos cronometrados e retornos de chamada de cronômetro periódicos no XOS. O coprocessador DSP suporta até três temporizadores internos que os programadores podem configurar conforme necessário.

Compreendendo os semáforos

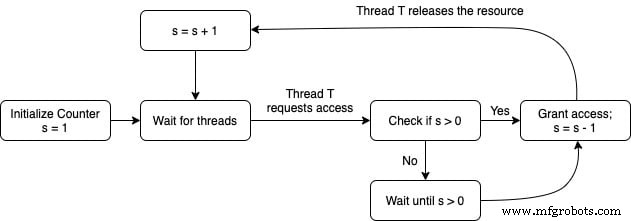

Na programação multithread, os semáforos fornecem um meio de controlar e coordenar o acesso a um recurso compartilhado. Os semáforos ajudam a evitar problemas de seção crítica em sistemas concorrentes sincronizando diferentes threads. Os semáforos são uma construção simples que mantém o controle de um contador interno com um valor inicial predeterminado que os programadores podem definir livremente no código-fonte. Existem diferentes implementações, mas o contador geralmente representa quantos threads ainda podem acessar um recurso compartilhado.

Sempre que um thread deseja acessar o recurso compartilhado, o sistema verifica se o contador associado é maior que zero. Se for, o sistema operacional concede acesso ao recurso e diminui o contador interno do semáforo. Se um thread não pode acessar o recurso no momento determinado, o thread muda para um estado de bloqueio e espera até receber acesso ao recurso. Sempre que um thread libera o recurso, o sistema operacional aumenta o contador do semáforo e um novo thread pode entrar na seção crítica.

Figura 2. Um fluxograma ilustrando como funcionam os semáforos

Uma visão geral do i.MX RT500 MCU e do DSP

i.MX RT500 é uma família de microcontroladores dual-core baseados em um poderoso núcleo Arm® Cortex®-M33 com velocidade de clock de até 275 MHz e suporte para até cinco megabytes de SRAM.

O i.MX RT500 MCU oferece recursos de proteção como Arm TrustZone e uma unidade de proteção de memória embutida (MPU) com suporte para até oito regiões. O coprocessador criptográfico CASPER permite a aceleração de hardware para impulsionar várias funções necessárias para algoritmos criptográficos assimétricos. Um conjunto de recursos de economia de energia permite que os designers correspondam o consumo de energia do i.MX RT500 aos requisitos de sua aplicação.

Vários aceleradores de hardware dedicados ajudam a CPU principal a realizar cálculos de DSP. Um DSP de áudio Cadence® Tensilica® Fusion F1 adicional, uma GPU 2D com aceleração de gráficos vetoriais e várias interfaces de exibição tornam o i.MX RT500 adequado para várias aplicações embarcadas seguras e de baixo consumo de energia. Os casos de uso típicos incluem aplicativos IoT, dispositivos IoT, dispositivos auditivos, assistentes pessoais ativados por voz e outros dispositivos de consumo semelhantes.

Uma olhada no DSP de áudio

O i.MX RT500 contém vários coprocessadores especiais que podem ajudar a aliviar a carga sobre os núcleos da CPU, executando cálculos matematicamente complexos, deixando os núcleos de processamento livres para realizar outras tarefas. Um desses processadores dedicados é o Fusion DSP, que inclui um processador de áudio Cadence® Tensilica® Fusion F1 e uma unidade de ponto flutuante de hardware.

Este mecanismo de processamento de áudio funciona em frequências de até 200 MHz e é projetado para habilitar dispositivos acionados por voz sempre ligados, como assistentes virtuais. Além disso, o DSP de áudio combina vários módulos para tarefas típicas de pré-processamento e pós-processamento usando vários codecs de áudio.

O DSP e os núcleos da CPU principal podem se comunicar entre si por vários meios. Os desenvolvedores podem usar toda a SRAM ao trabalhar com o Fusion DSP, a menos que a RAM esteja protegida e certas partes marcadas para acesso somente seguro.

Programação com o DSP em mente

Os DSPs da Tensilica oferecem suporte a vários sistemas operacionais em tempo real (RTOS), incluindo FreeRTOS ™, Zephyr ™, Linux® e XOS. A Cadence desenvolveu o kernel embarcado XOS como um projeto de referência com os processadores Tensilica em mente.

Os recursos leves do kernel XOS incluem um agendador de tarefas, comutação de contexto adaptável, mecanismos de sincronização, gerenciamento de interrupções e exceções e gerenciamento de recursos críticos. O código-fonte do kernel é escrito principalmente em C padrão e não é específico para processadores Xtensa e DSPs.

Atendendo aos requisitos de dispositivos para consumidores inteligentes

A família i.MX RT500 de MCUs crossover possui vários recursos projetados para inspirar os dispositivos de consumo inteligentes de amanhã. Os diferentes coprocessadores auxiliam os principais núcleos de processamento do MCU na realização de cálculos matematicamente complexos para aplicações de segurança e processamento de sinal. Um desses coprocessadores é o Cadence® Tensilica® Fusion F1 DSP de áudio altamente otimizado, permitindo dispositivos acionados por voz sempre ligados, como assistentes virtuais. Os programadores podem utilizar o XOS e o Xplorer IDE para projetar aplicativos para o processador Cadence dedicado.

A nota de aplicação AN13159 contém mais detalhes, uma lista de funções API suportadas e exemplos para condições e eventos no XOS, e o site da NXP oferece mais informações sobre os recursos e aplicativos do i.MX RT500. Ele também fornece diferentes materiais de treinamento, como notas de aplicação, vídeos e webinars sob demanda.

Artigos do setor são uma forma de conteúdo que permite aos parceiros do setor compartilhar notícias, mensagens e tecnologia úteis com os leitores do All About Circuits de uma forma que o conteúdo editorial não é adequado. Todos os artigos da indústria estão sujeitos a diretrizes editoriais rígidas com a intenção de oferecer aos leitores notícias úteis, conhecimentos técnicos ou histórias. Os pontos de vista e opiniões expressos nos Artigos da Indústria são do parceiro e não necessariamente da All About Circuits ou de seus redatores.

Integrado

- C# usando

- Dispositivo híbrido mescla arquiteturas DSP e MCU

- Quando um DSP bate um acelerador de hardware

- Decisões, decisões:Acelerador de hardware ou DSP?

- Medição de nível de fluido sem contato usando um chip refletômetro

- Usando tags RFID para monitoramento de segurança residencial

- Os chipsets de radar de imagem 4D aprimoram a identificação do objeto

- Bluetooth MCU aprimora a segurança da IoT

- MCU sem fio apresenta arquitetura dual-core

- Diretrizes para lidar com DSP usando