NAND Gate S-R Flip-Flop

PEÇAS E MATERIAIS

- 4011 quad NAND gate (catálogo Radio Shack # 276-2411)

- 4001 quad NOR gate (catálogo Radio Shack # 276-2401)

- Chave DIP de oito posições (catálogo Radio Shack nº 275-1301)

- LED de gráfico de barras de dez segmentos (catálogo Radio Shack nº 276-081)

- Uma bateria de 6 volts

- Três resistores de 10 kΩ

- Dois resistores de 470 Ω

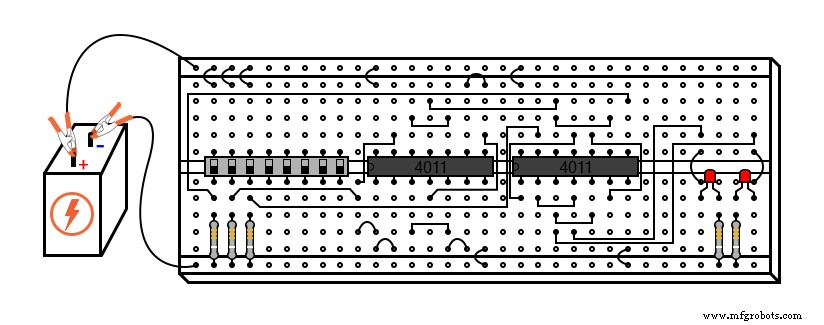

Cuidado! O 4011 IC é CMOS e, portanto, sensível à eletricidade estática! Embora a lista de peças exija uma unidade de LED de dez segmentos, a ilustração mostra dois LEDs individuais sendo usados. Isso se deve à falta de espaço na placa de ensaio para montar o conjunto do switch, dois circuitos integrados e o gráfico de barras.

Se você tiver espaço em sua placa de ensaio, sinta-se à vontade para usar o gráfico de barras conforme solicitado na lista de peças e conforme mostrado nos circuitos de travamento anteriores.

REFERÊNCIAS CRUZADAS

Aulas de circuitos elétricos , Volume 4, capítulo 3:"Portões lógicos"

Aulas de circuitos elétricos , Volume 4, capítulo 10:"Multivibradores"

OBJETIVOS DE APRENDIZAGEM

- A diferença entre uma trava fechada e um flip-flop

- Como construir um circuito de “detector de pulso”

- Aprenda os efeitos do “salto” do contato do interruptor em circuitos digitais

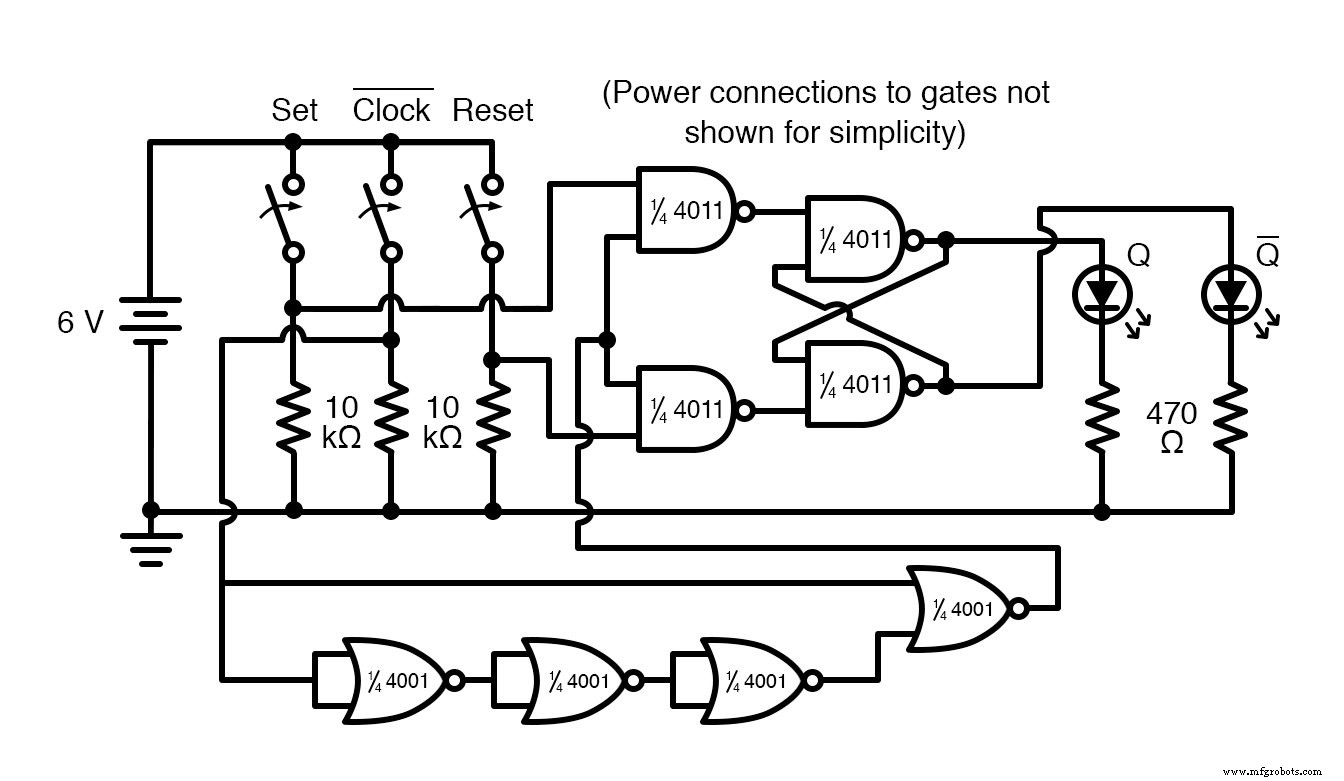

DIAGRAMA ESQUEMÁTICO

ILUSTRAÇÃO

INSTRUÇÕES

A única diferença entre um fechado (ou ativado ) latch e um flip-flop é que um flip-flop é habilitado apenas na borda de subida ou descida de um sinal de “clock”, em vez de toda a duração de um sinal de habilitação “alto”.

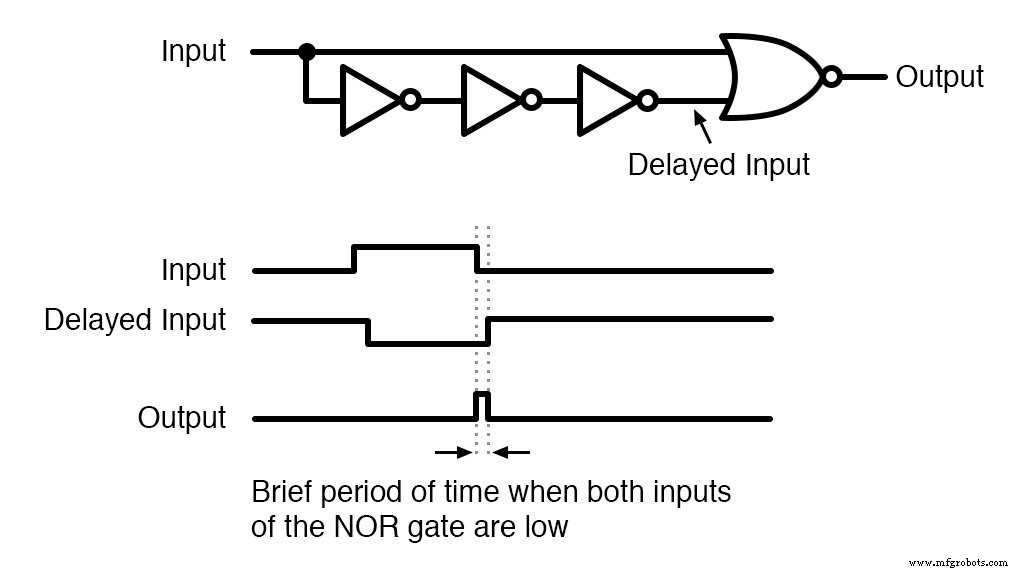

A conversão de uma trava habilitada em um flip-flop requer simplesmente que um circuito "detector de pulso" seja adicionado à entrada de habilitação para que a borda de um pulso de clock gere um breve pulso de habilitação "alto":

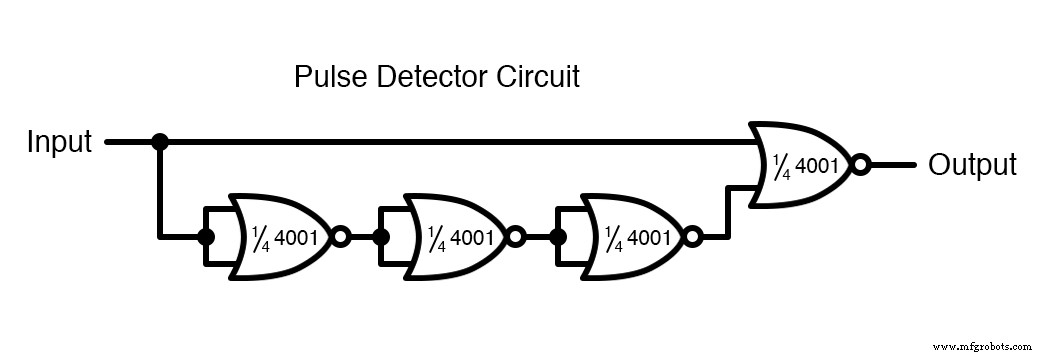

A única porta NOR e as três portas do inversor criam esse efeito, explorando o tempo de retardo de propagação de várias portas em cascata. Neste experimento, eu uso três portas NOR com entradas paralelas para criar três inversores, usando assim todas as quatro portas NOR de um circuito integrado 4001:

Normalmente, ao usar uma porta NOR como um inversor, uma entrada seria aterrada enquanto a outra atua como a entrada do inversor, para minimizar a capacitância de entrada e aumentar a velocidade. Aqui, no entanto, uma resposta lenta é desejada , então eu coloco em paralelo as entradas NOR para fazer inversores em vez de usar o método mais convencional.

Observe que este circuito detector de pulso em particular produz um pulso de saída “alto” em cada borda descendente do sinal do relógio (entrada). Isso significa que o circuito flip-flop deve responder aos estados de entrada Set e Reset somente quando o interruptor do meio é movido de "on" para "off", não de "off" para "on".

Quando você constrói este circuito, entretanto, você pode descobrir que as saídas respondem aos sinais de entrada Set e Reset durante ambos transições da entrada de relógio, não apenas quando é comutado de um estado “alto” para um estado “baixo”.

O motivo para isso é o contato rejeição :o efeito de um interruptor mecânico que abre e quebra rapidamente quando seus contatos são fechados pela primeira vez, devido à colisão elástica das placas de contato de metal. Em vez de o interruptor Clock produzir uma única transição de sinal limpo de baixo para alto quando fechado, provavelmente haverá vários "ciclos" baixo-alto-baixo à medida que os blocos de contato "saltam" durante a ativação.

A primeira transição de alto para baixo causada pelo salto acionará o circuito do detector de pulso, habilitando a trava S-R naquele momento, tornando-o responsivo às entradas Set e Reset. Idealmente, é claro, os interruptores são perfeitos e sem saltos. No mundo real, porém, o salto de contato é um problema muito comum para circuitos de porta digital operados por entradas de switch e deve ser bem compreendido se quiser ser superado.

PLANILHA RELACIONADA:

-

Planilha de circuitos flip-flop

Tecnologia industrial