Função de Gate Básica

Peças e Materiais

- 4011 quad NAND gate (catálogo Radio Shack # 276-2411)

- Chave DIP de oito posições (catálogo Radio Shack nº 275-1301)

- LED de gráfico de barras de dez segmentos (catálogo Radio Shack nº 276-081)

- Uma bateria de 6 volts

- Dois resistores de 10 kΩ

- Três resistores de 470 Ω

Cuidado! O 4011 IC é CMOS e, portanto, sensível à eletricidade estática!

Leitura Adicional

Aulas de circuitos elétricos , Volume 4, capítulo 3:"Portões lógicos"

Objetivos de aprendizagem

- Objetivo de um resistor “suspenso”

- Como determinar experimentalmente a tabela verdade de um portão

- Como conectar portas lógicas

- Como criar diferentes funções lógicas usando portas NAND

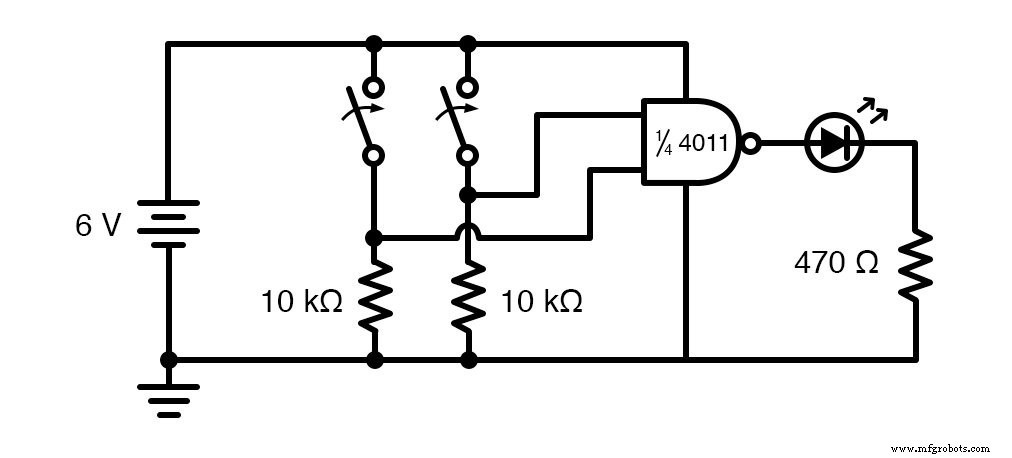

Diagrama esquemático da função de portão básico

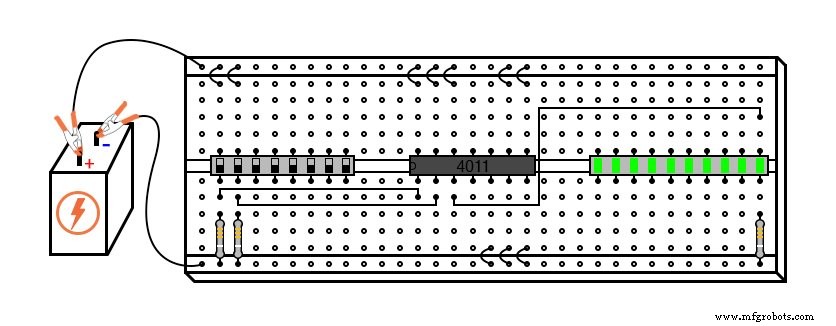

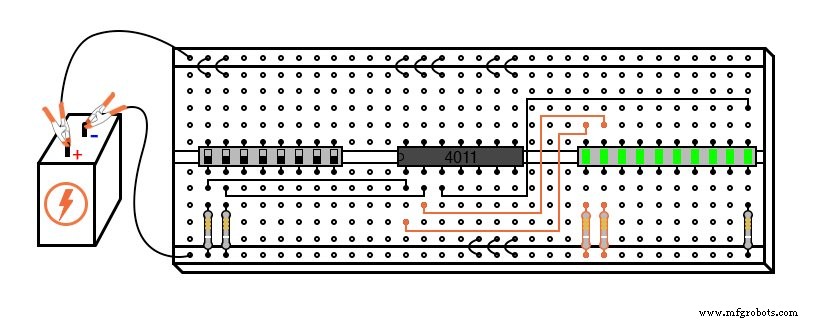

Ilustração da função de portão básico

Instruções para o experimento

Para começar, conecte uma única porta NAND a duas chaves de entrada e um LED, conforme mostrado. A princípio, o uso de uma chave de 8 posições e um gráfico de barras de LED de 10 segmentos pode parecer excessivo, pois apenas duas chaves e um LED são necessários para mostrar a operação de uma única porta NAND. No entanto, a presença desses interruptores e LEDs extras torna muito conveniente expandir o circuito e ajuda a tornar o layout do circuito limpo e compacto.

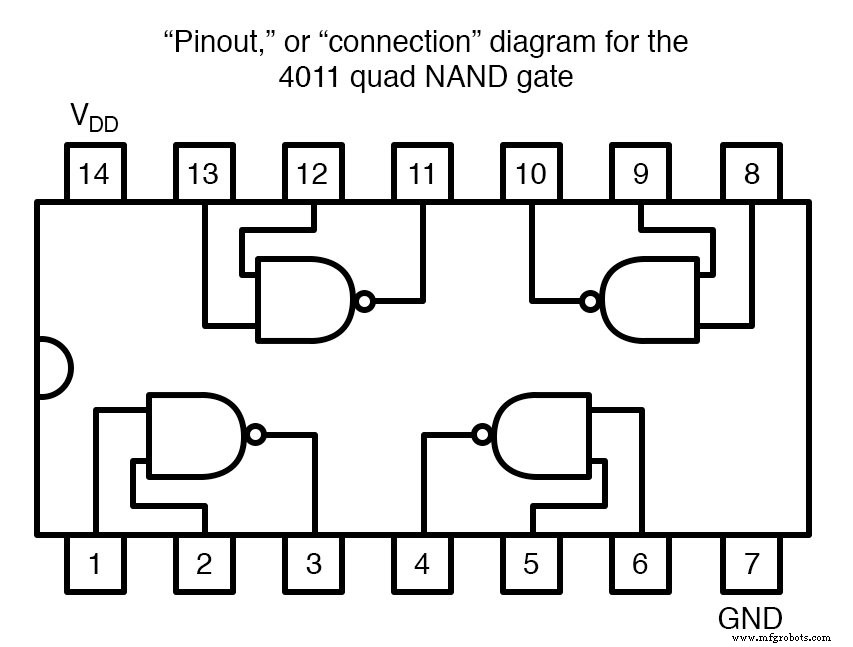

É altamente recomendável que você tenha uma folha de dados para o 4011 chip disponível quando você constrói seu circuito. Não siga apenas a ilustração mostrada acima! É importante que você desenvolva a habilidade de ler planilhas de dados, especialmente diagramas de “pinagem” ao conectar terminais IC a outros elementos de circuito. O diagrama de conexão da folha de dados é uma informação essencial para se ter. Aqui é mostrada minha própria versão do que qualquer 4011 folha de dados mostra:

Na ilustração do breadboard, mostrei o circuito construído usando a porta NAND inferior esquerda:os pinos nºs 1 e 2 são as entradas e o pino nº 3 é a saída. Os pinos nºs 14 e 7 conduzem energia DC para todos os quatro circuitos de porta dentro do chip IC, “V DD ”Representando o lado positivo da fonte de alimentação (+ V) e“ Gnd ”representando o lado negativo da fonte de alimentação (-V), ou aterramento. Às vezes, o terminal negativo da fonte de alimentação será identificado como “V SS ”Em vez de“ Gnd ”em uma folha de dados, mas significa a mesma coisa.

O circuito lógico digital não usa fontes de alimentação divididas como os amplificadores operacionais. Como os circuitos do amplificador operacional, porém, o aterramento ainda é o ponto de referência implícito para todas as medições de tensão. Se eu fosse falar de um sinal “alto” presente em um determinado pino do chip, significaria que havia voltagem total entre aquele pino e o lado negativo da fonte de alimentação (terra).

Observe como todas as entradas das portas não utilizadas dentro do 4011 o chip está conectado a V DD ou chão. Isso não é um erro, mas um ato de design intencional. Desde o 4011 é um circuito integrado CMOS, e as entradas do circuito CMOS são deixadas desconectadas ( flutuante ) pode assumir qualquer nível de tensão meramente pela interceptação de uma carga elétrica estática de um objeto próximo, deixando as entradas flutuantes, o que significa que essas portas não utilizadas podem receber quaisquer combinações aleatórias de sinais "alto" e "baixo".

Por que isso é indesejável, se não estamos usando esses portões? Quem se importa com os sinais que eles recebem, se não estamos fazendo nada com suas saídas? O problema é que se os sinais de tensão estática aparecem nas entradas da porta que não estão totalmente "altas" ou totalmente "baixas", os transistores internos das portas podem começar a ligar de forma a consumir corrente excessiva. Na pior das hipóteses, isso pode causar danos ao chip.

Na melhor das hipóteses, significa consumo excessivo de energia. Pouco importa se escolhermos conectar essas entradas de porta não utilizadas "altas" (V DD ) ou “baixo” (terra), desde que os conectemos a um desses dois locais. Na ilustração do breadboard, mostro todas as principais entradas conectadas a V DD , e todas as entradas inferiores (das portas não utilizadas) conectadas ao aterramento. Isso foi feito simplesmente porque os orifícios do trilho da fonte de alimentação estavam mais próximos e não exigiam cabos de jumper longos!

Observe que nenhuma das saídas de portas não utilizadas foram conectados a V DD ou aterrar, e por um bom motivo! Se eu fizesse isso, poderia forçar uma porta a assumir o estado de saída oposto ao que está tentando alcançar, o que é uma maneira complicada de dizer que eu teria criado um curto-circuito. Imagine uma porta que deve produzir um nível lógico “alto” (para uma porta NAND, isso seria verdadeiro se qualquer uma de suas entradas fosse “baixa”).

Se tal porta tivesse seu terminal de saída diretamente conectado ao aterramento, ela nunca poderia atingir um estado “alto” (sendo eletricamente comum ao aterramento por meio da conexão do fio do jumper). Em vez disso, seu transistor de saída superior (canal P) seria ligado em vão, fornecendo corrente máxima para uma carga inexistente. Isso provavelmente danificaria o portão! Os terminais de saída de porta, por sua própria natureza, geram seus próprios níveis lógicos e nunca “flutuam” da mesma forma que as entradas de porta CMOS fazem.

Os dois resistores de 10 kΩ são colocados no circuito para evitar condições flutuantes de entrada na porta usada. Com a chave fechada, a respectiva entrada será conectada diretamente ao V DD e, portanto, ser "alto". Com um interruptor aberto, o 10 kΩ “ menu suspenso "Resistor fornece uma conexão resistiva ao terra, garantindo um estado" baixo "seguro no terminal de entrada da porta. Dessa forma, a entrada não será suscetível a tensões estáticas parasitas.

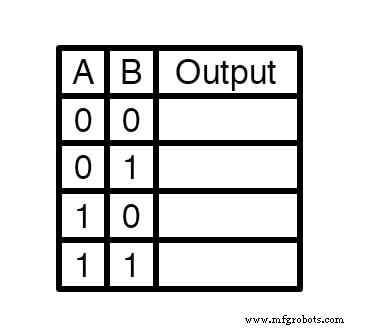

Com a porta NAND conectada às duas chaves e um LED conforme mostrado, você está pronto para desenvolver uma “tabela verdade” para a porta NAND. Mesmo se você já sabe como é uma tabela de verdade de porta NAND, este é um bom exercício de experimentação:descobrir os princípios comportamentais de um circuito por indução. Desenhe uma tabela de verdade em um pedaço de papel como este:

O “A” e “B” colunas representam as duas opções de entrada, respectivamente. Quando a chave está ligada, seu estado é “alto” ou 1. Quando a chave está desligada, seu estado é “baixo” ou 0, conforme garantido por seu resistor suspenso. A saída do portão, é claro, é representada pelo LED:esteja ele aceso (1) ou apagado (0). Depois de colocar as chaves em todas as combinações possíveis de estados e registrar o status do LED, compare a tabela verdade resultante com o que a tabela verdade de uma porta NAND deve ser.

Como você pode imaginar, este circuito da placa de ensaio não se limita a testar portas NAND. Qualquer tipo de porta pode ser testado com duas chaves, dois resistores suspensos e um LED para indicar o status da saída. Apenas certifique-se de verificar novamente o diagrama de "pinagem" do chip antes de substituí-lo pino por pino no lugar do 4011 . Nem todos os chips de gate “quad” têm as mesmas atribuições de pinos!

Melhoria adicional

Uma melhoria que você pode querer fazer neste circuito é atribuir um par de LEDs para indicar o status de entrada, além de um LED atribuído para indicar a saída. Isso torna a operação um pouco mais interessante de observar e tem o benefício adicional de indicar se um switch falha em fechar (ou abrir), mostrando o verdadeiro sinal de entrada para o portão, em vez de forçar você a inferir o status de entrada a partir da posição do interruptor:

PLANILHA RELACIONADA:

-

Planilha de portas lógicas básicas

Tecnologia industrial