TTL NAND e portas AND

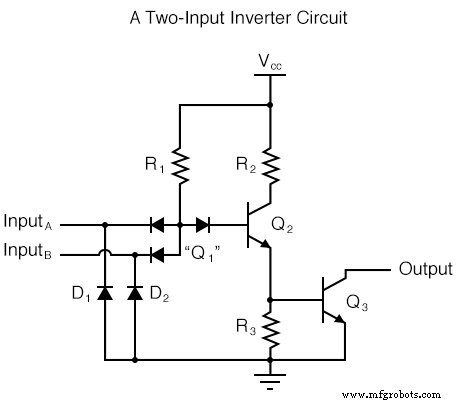

Suponha que alteramos nosso circuito inversor de coletor aberto básico, adicionando um segundo terminal de entrada exatamente como o primeiro:

Este esquema ilustra um circuito real, mas não é chamado de "inversor de duas entradas". Por meio da análise, descobriremos qual é a função lógica deste circuito e, correspondentemente, como ele deve ser designado.

Assim como no caso do inversor e do buffer, o conjunto de diodos de "direção" marcado "Q1" é na verdade formado como um transistor, embora não seja usado em qualquer capacidade de amplificação. Infelizmente, uma estrutura simples de transistor NPN é inadequada para simular os três As junções PN são necessárias nesta rede de diodos, portanto, um transistor (e símbolo) diferente é necessário.

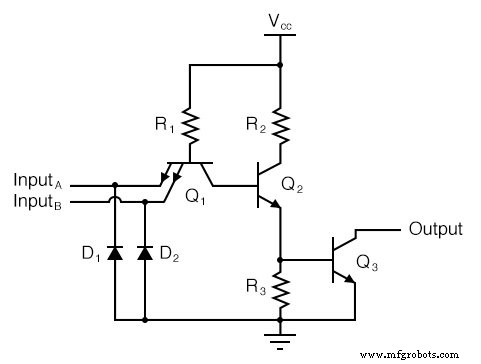

Este transistor tem um coletor, uma base e dois emissores, e no circuito, é assim:

No circuito de entrada única (inversor), o aterramento da entrada resultou em uma saída que assumiu o estado “alto” (1). No caso da configuração de saída de coletor aberto, este estado "alto" era simplesmente "flutuante".

Permitir que a entrada flutue (ou seja conectada ao Vcc) resultou no aterramento da saída, que está no estado “baixo” ou 0. Assim, um 1 de entrada resultou em um 0 de saída e vice-versa.

Ilustração de circuito para estados de entrada

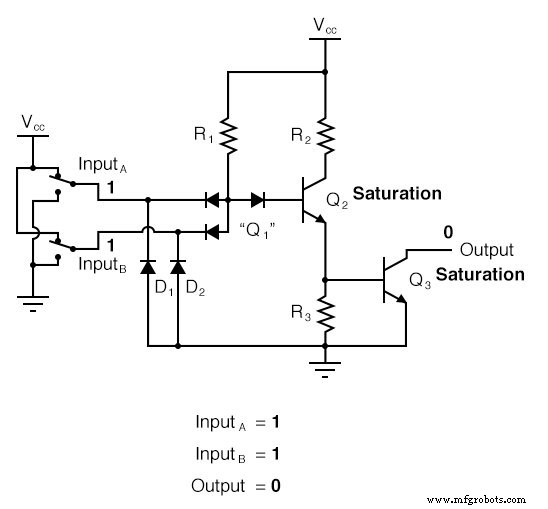

Como este circuito se parece muito com o circuito inversor simples, sendo a única diferença um segundo terminal de entrada conectado da mesma forma à base do transistor Q2, podemos dizer que cada uma das entradas terá o mesmo efeito na saída.

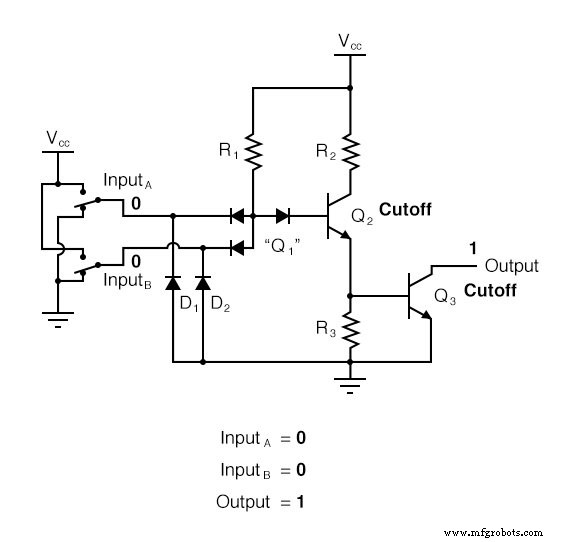

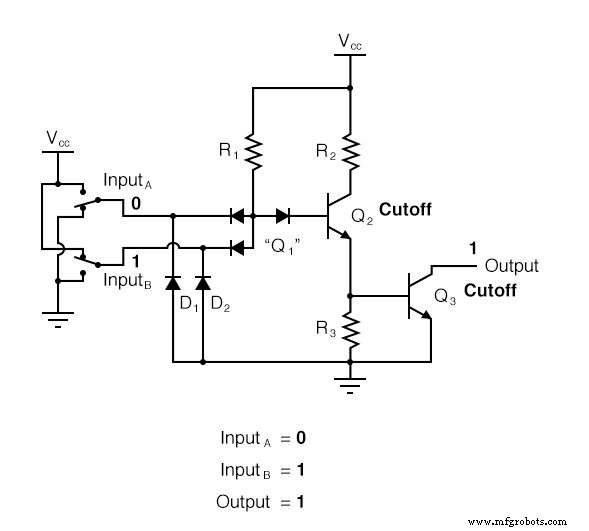

Ou seja, se qualquer uma das entradas estiver aterrada, o transistor Q2 será forçado a uma condição de corte, desligando assim Q3 e flutuando a saída (a saída fica “alta”). A seguinte série de ilustrações mostra isso para três estados de entrada (00, 01 e 10):

Em qualquer caso, onde houver uma entrada aterrada (“baixa”), a saída é garantida como flutuante (“alta”). Por outro lado, o único momento em que a saída ficará “baixa” é se o transistor Q3 ligar, o que significa que o transistor Q2 deve ser ligado (saturado), o que significa que nenhuma entrada pode estar desviando a corrente R1 da base de Q2.

A única condição que irá satisfazer este requisito é quando ambas as entradas estão "altas" (1):

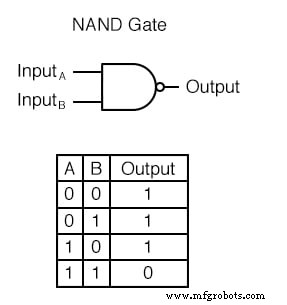

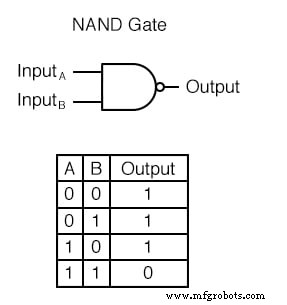

Porta NAND

Coletando e tabulando esses resultados em uma tabela verdade, vemos que o padrão corresponde ao da porta NAND:

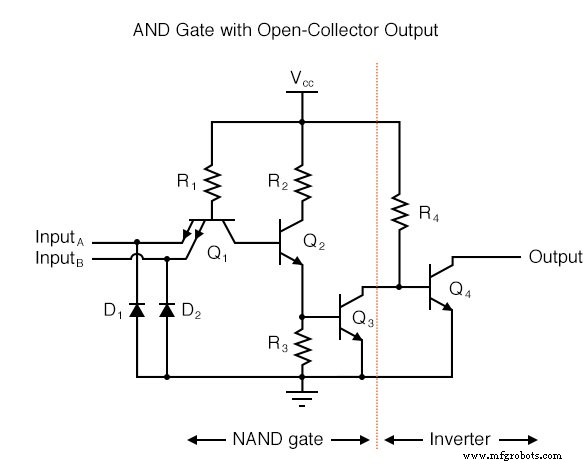

Na seção anterior sobre portas NAND, esse tipo de porta foi criado pegando uma porta AND e aumentando sua complexidade adicionando um inversor (NÃO porta) à saída. No entanto, quando examinamos esse circuito, vemos que a função NAND é, na verdade, o modo de operação mais simples e natural para esse projeto TTL.

Para criar uma função AND usando circuitos TTL, precisamos aumentar a complexidade deste circuito ao adicionar um estágio do inversor à saída, assim como tivemos que adicionar um estágio do transistor adicional ao circuito do inversor TTL para transformá-lo em um buffer:

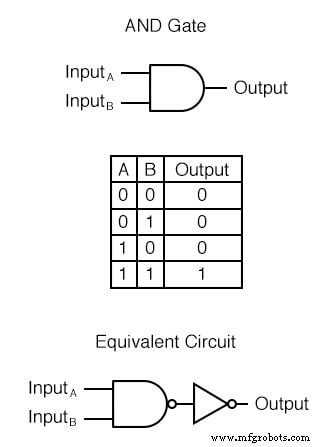

E portão

A tabela verdade e o circuito de porta equivalente (uma porta NAND de saída invertida) são mostrados aqui:

Obviamente, os circuitos de porta NAND e AND podem ser projetados com estágios de saída totem-pole em vez de coletor aberto. Estou optando por mostrar as versões de coletor aberto por uma questão de simplicidade.

REVER:

- Uma porta NAND TTL pode ser feita pegando um circuito inversor TTL e adicionando outra entrada.

- Uma porta AND pode ser criada adicionando um estágio do inversor à saída do circuito da porta NAND.

PLANILHA RELACIONADA:

-

Planilha de portas lógicas TTL

Tecnologia industrial

- Porta NAND S-R Habilitada Trava

- Equações e leis do circuito CC

- Sinais e portas digitais

- TTL NOR e portas OR

- Portões de saída especial

- Acoplamento de entrada e saída

- C - Entrada e Saída

- Materiais e construção do circuito flexível

- Componentes da placa de circuito e suas aplicações

- Retrocessos e soluções no projeto de PCB de RF