TTL NOR e portas OR

Análise de Circuito TTL

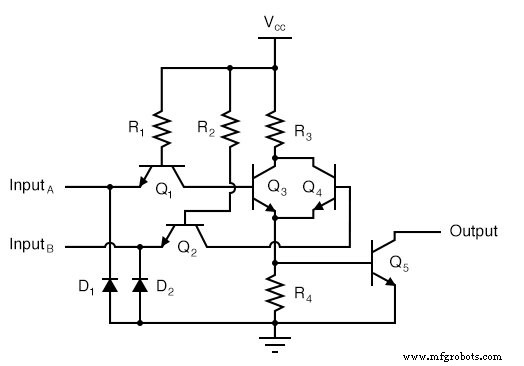

Vamos examinar o seguinte circuito TTL e analisar sua operação:

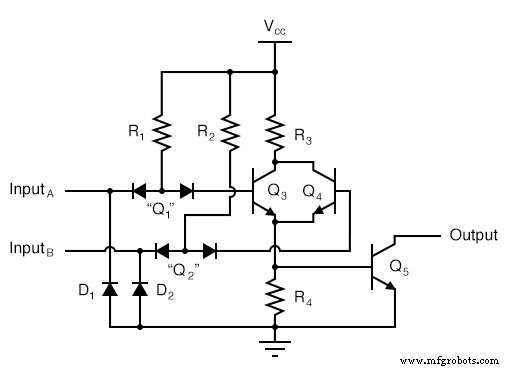

Os transistores Q1 e Q2 são arranjados da mesma maneira que vimos para o transistor Q1 em todos os outros circuitos TTL. Em vez de funcionar como amplificadores, Q1 e Q2 estão sendo usados como redes de "direção" de dois diodos. Podemos substituir Q1 e Q2 por conjuntos de diodos para ajudar a ilustrar:

Se a entrada A for deixada flutuando (ou conectada ao Vcc), a corrente passará pela base do transistor Q3, saturando-o. Se a entrada A é aterrada, essa corrente é desviada para longe da base de Q3 através do diodo de direção esquerdo de "Q1", forçando assim Q3 em corte. O mesmo pode ser dito para a entrada B e transistor Q4:o nível lógico da entrada B determina a condução de Q4:saturada ou corte.

Observe como os transistores Q3 e Q4 estão em paralelo em seus terminais coletor e emissor. Em essência, esses dois transistores atuam como interruptores em paralelo, permitindo a corrente através dos resistores R3 e R4 de acordo com os níveis lógicos das entradas A e B. Se algum entrada está em um nível "alto" (1), então pelo menos um dos dois transistores (Q3 e / ou Q4) será saturado, permitindo a corrente através dos resistores R3 e R4, e ligando o transistor de saída final Q5 para um " saída de nível lógico baixo ”(0). A única maneira de a saída deste circuito assumir um estado "alto" (1) é se ambos Q3 e Q4 são cortados, o que significa ambos as entradas teriam que ser aterradas, ou “baixo” (0).

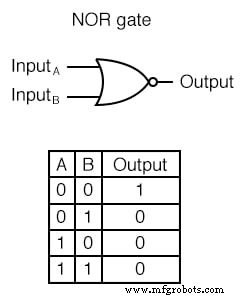

Tabela da verdade do portão NOR

A tabela de verdade deste circuito, então, é equivalente àquela da porta NOR:

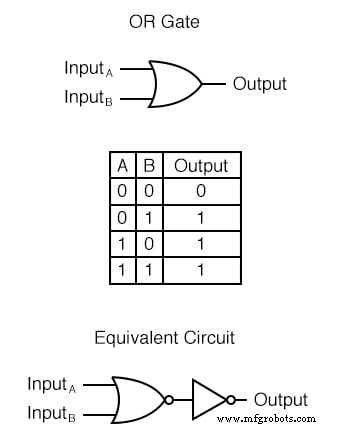

Conversão de um circuito TTL de porta NOR em uma porta OU

Para transformar este circuito de porta NOR em uma porta OR, teríamos que inverter o nível lógico de saída com outro estágio de transistor, assim como fizemos com o exemplo de porta NAND para AND:

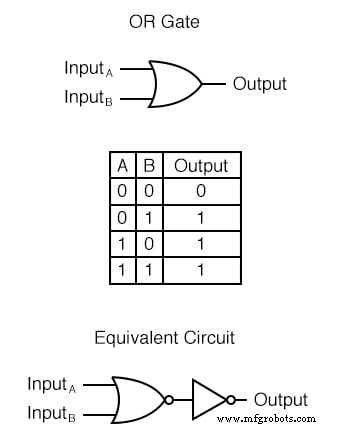

Mesa da verdade do portão OR

A tabela verdade e o circuito de porta equivalente (uma porta NOR de saída invertida) são mostrados aqui:

Obviamente, estágios de saída totem-pole também são possíveis em circuitos lógicos NOR e OR TTL.

REVER:

- Uma porta OR pode ser criada adicionando um estágio do inversor à saída do circuito da porta NOR.

Tecnologia industrial

- Função de Gate Básica

- Porta NOR Trava S-R

- Porta NAND S-R Habilitada Trava

- Equações e leis do circuito CC

- Sinais e portas digitais

- Portas de entrada múltipla

- TTL NAND e portas AND

- Materiais e construção do circuito flexível

- Componentes da placa de circuito e suas aplicações

- Retrocessos e soluções no projeto de PCB de RF