Como parar a simulação em um testbench VHDL

Como você interrompe o simulador VHDL quando a simulação é concluída? Existem várias maneiras de fazer isso. Neste artigo, examinaremos as maneiras mais comuns de encerrar uma execução bem-sucedida do testbench.

O código VHDL apresentado aqui é universal e deve funcionar em qualquer simulador VHDL capaz. Para os métodos envolvendo Tcl, listarei os comandos para os simuladores ModelSim e Vivado.

Você pode baixar um projeto de exemplo com os quatro testbenches diferentes deste artigo se tiver o ModelSim instalado. Digite seu endereço de e-mail no formulário abaixo para receber o arquivo Zip!

Usando finalizar procedimento

O VHDL acabamento procedure é minha maneira favorita de parar um testbench VHDL que termina sem erros. Você tem que importar “finish” do pacote STD.ENV, e você tem que compilar o testbench em VHDL-2008 ou mais recente para usá-lo.

O código abaixo finaliza a simulação quando chegamos à última linha do processo do sequenciador do testbench.

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

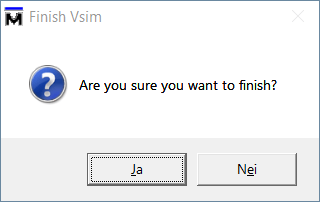

Observe que concluir sai da simulação por padrão. Se você estiver executando o ModelSim na versão GUI, um pop-up aparecerá dizendo “Tem certeza de que deseja terminar?”. Se você clicar em Sim, o ModelSim será encerrado.

Provavelmente não é isso que você quer. Felizmente, podemos evitar esse comportamento adicionando a opção “-onfinish stop” ao comando vsim, conforme mostrado abaixo. Ao fazer isso, o conclui procedimento irá se comportar da mesma forma que o stop procedimento que discutiremos na próxima seção deste artigo.

vsim -onfinish stop work.using_finish_tb

Uma vantagem de usar finalizar é que você pode usar o comportamento padrão ao simular no modo de lote. Se estiver usando scripts para iniciar a simulação, você deseja retornar o controle ao script de chamada após a conclusão da simulação.

O exemplo abaixo mostra um testbench usando o finish procedimento iniciado no modo de lote ModelSim no Linux. Após a conclusão do testbench, o simulador é encerrado e, na última linha, estamos de volta ao shell do Linux.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

O VHDL acabamento procedimento é definido no pacote ENV padrão. Como podemos ver no código abaixo, ele vem em dois sabores sobrecarregados. Tem a versão sem nenhum parâmetro, que é o que sempre uso, e tem outra que recebe um status integer como entrada constante.

procedure FINISH (STATUS: INTEGER); procedure FINISH;

Você pensaria que o inteiro de status se torna o código de saída quando chamado de um shell do Linux, mas esse não é o caso, pelo menos não com ModelSim. O problema de usar esse código de status é que o que ele faz depende do simulador. A redação no padrão VHDL-2008 é “o valor do parâmetro STATUS pode ser usado de maneira definida pela implementação pelo simulador de host “.

No entanto, você pode controlar o valor do código de saída do Linux no ModelSim usando o comando Tcl

exit -code <value> , mas isso é outra história. Usando a parar procedimento

A parada do VHDL procedimento faz com que a simulação seja pausada. Isso pode ser útil se você quiser examinar os valores do sinal manualmente ou mesmo continuar a simulação mais tarde. O simulador o trata como um ponto de interrupção.

O exemplo abaixo mostra como importar e usar o stop procedimento.

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

Um problema ao usar parar em configurações baseadas em script é que ele não sai da simulação. Em vez de devolver o controle ao chamador, o ModelSim abre um shell de comando Tcl, fazendo com que o script de chamada trave indefinidamente.

A lista abaixo mostra a saída da execução do testbench que usa o stop procedimento em modo batch. Após a simulação parar, ainda estamos no ModelSim. Para sair do shell Tcl, teríamos que digitar “exit”.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

Assim como o acabamento procedimento, parar requer VHDL-2008 ou mais recente. Conforme mostrado abaixo, existe uma versão sobrecarregada do procedimento. Recebe um valor de status inteiro, mas o comportamento varia entre os simuladores.

procedure STOP (STATUS: INTEGER); procedure STOP;

Usando a afirmação palavra-chave

Uma maneira universal e à prova de falhas de parar um testbench VHDL é criar uma falha de asserção. Essa foi a primeira maneira que alguém me ensinou a terminar a simulação quando eu estava aprendendo VHDL na universidade.

Nenhuma importação adicional é necessária e funciona em todas as versões VHDL. Apenas certifique-se de usar o nível de gravidade falha , conforme mostrado no exemplo abaixo.

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

E por que odeio essa maneira de interromper uma simulação bem-sucedida?

Em primeiro lugar, parece estranho e confuso ver a impressão do exemplo acima:

# ** Failure: Test: OK

Ele diz que é uma “falha”, mas o teste é “OK” ao mesmo tempo. Isso porque a afirmação A instrução deve indicar uma condição de erro e não a conclusão bem-sucedida da simulação.

O outro problema irritante em que posso pensar é que fica difícil descobrir programaticamente se a simulação foi bem-sucedida.

A maioria dos profissionais de VHDL inicia as simulações a partir de um script em algum momento, por exemplo, como parte de um esquema de teste de regressão maior. Se o testbench também parar em uma falha de asserção quando não houver nada de errado, não podemos usar isso como um marcador para determinar a integridade do módulo VHDL.

Usando Tcl

O último método de parar a simulação que vou abordar é usar Tcl em combinação com VHDL. Em vez de parar o testbench do arquivo VHDL, definimos um sinal VHDL regular quando é hora de parar. E de antemão, configuramos o simulador para escutar uma mudança neste sinal de disparo.

Leia também:

Por que você precisa aprender Tcl

Veja o exemplo abaixo, que define um sinal chamado stop_condition quando todos os casos de teste forem concluídos.

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

Você pode colocar qualquer processo testbench que tenha feito seu trabalho para dormir com uma única espera declaração antes do fim do processo marcação. Isso impedirá que ele reinicie. O código Tcl para realmente interromper a simulação difere entre os simuladores.

No ModelSim

O que queremos é parar o testbench quando a stop_condition O sinal VHDL torna-se true . Podemos fazer isso configurando um retorno de chamada em Tcl antes de executarmos o testbench VHDL.

De acordo com o Manual de Referência de Comandos do ModelSim, podemos conseguir isso usando o Tcl quando comando. No código Tcl abaixo, registramos esse retorno de chamada e iniciamos o simulador usando run -all .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

Observe que o código dentro das chaves não será executado até que o retorno de chamada aconteça. Quando o código VHDL altera a stop_condition sinal para verdadeiro , o simulador irá pausar e executar as duas linhas. No exemplo, paramos a simulação e imprimimos “Test:OK” no console. Você também pode ter um Tcl saída comando lá, que sairia do simulador, assim como o VHDL finalizar procedimento.

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

A listagem acima mostra a saída impressa no console do ModelSim quando o testbench Tcl/VHDL é concluído. Se você quiser experimentá-lo em seu computador, use o formulário abaixo para baixar o projeto ModelSim com todos os exemplos deste artigo!

Em Viva

De acordo com o Guia de Referência de Comandos Tcl do Vivado Design Suite, podemos registrar um retorno de chamada Tcl usando a add_condition comando. O código abaixo mostra o equivalente Xilinx para a versão ModelSim discutida anteriormente.

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

O -notrace switch impede que as linhas de código na função de retorno de chamada sejam ecoadas para o terminal enquanto são executadas. Eu prefiro não ter a desordem extra no console.

A listagem abaixo mostra um trecho da simulação rodando no console do simulador Vivado.

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

Considerações finais

Como você viu, há muitas maneiras de encerrar uma simulação VHDL. No entanto, o único que eu uso é o VHDL-2008 acabamento procedimento.

Todos os simuladores suportam VHDL-2008 até agora, e você não precisa compilar o código RTL em 2008, apenas o testbench. O acabamento O procedimento é o método mais portátil e permite que você pare o simulador ao executar no modo GUI ou saia ao executar no modo de lote. Exatamente o comportamento que eu quero na maioria das vezes.

Mas há vantagens nos métodos Tcl que estão fora do escopo deste artigo. Depois de pausar o simulador no retorno de chamada Tcl, você pode fazer muito mais do que apenas parar o simulador e sair. Você pode examinar sinais VHDL e até manipulá-los usando Tcl, enquanto estiver no retorno de chamada. Isso é verificação usando Tcl.

VHDL

- Como criar uma lista de strings em VHDL

- Como criar um testbench orientado por Tcl para um módulo de bloqueio de código VHDL

- Como criar um controlador PWM em VHDL

- Como gerar números aleatórios em VHDL

- Testbench interativo usando Tcl

- Como criar um testbench de autoverificação

- Como criar uma lista vinculada em VHDL

- Como usar um procedimento em um processo em VHDL

- Como usar uma função em VHDL

- Como parar a ferrugem