Testbench interativo usando Tcl

Um testbench interativo é uma configuração de simulador onde a entrada para o dispositivo em teste (DUT) é fornecida por um operador enquanto o testbench está em execução. Na maioria das vezes, isso significaria digitar comandos no console do simulador para fornecer estímulo ao DUT.

Embora você deva sempre criar um testbench de autoverificação, um testbench interativo pode ser um bom complemento. É mais fácil realizar testes ad-hoc com um testbench interativo em mãos do que alterar o código do testbench de autoverificação.

Muitas vezes, você descobrirá problemas no laboratório que desejará experimentar no testbench. Com um testbench interativo, pode ser tão fácil quanto digitar a sequência de entrada que foi observada para replicar o comportamento indesejável no simulador.

Tcl interagindo com VHDL

A maioria dos simuladores VHDL usa Tcl como sua linguagem de console. Os simuladores têm vários comandos específicos do fornecedor, mas a boa notícia é que eles podem ser tratados como qualquer outro comando Tcl. Você pode usar o Tcl para criar scripts complexos, principalmente portáteis, para gerenciar e dar suporte a seus testbenches VHDL.

Alterando sinais VHDL de Tcl

Para interagir com o VHDL, precisamos encontrar o comando para alterar um valor de sinal. No ModelSim, este é o comando “force”. Conforme especificado no documento de referência do comando, a sinopse do comando é:

force {<object_name> <value> [[@]<time_info>][, <value> [@]<time_info>]...

[-deposit | -drive | -freeze] [-cancel [@]<time_info>] [-repeat [@]<time_info>] O switch que você deseja usar é o sinalizador “-deposit”. Isso altera o valor do sinal VHDL instantaneamente, mas permite que outro driver VHDL ou Tcl o altere para outra coisa posteriormente.

Ao ignorar as opções que não estamos usando, a sinopse simplificada fica assim:

force -deposit <signal_name> <value>

O gatilho VHDL

Agora que sabemos como controlar os sinais VHDL do Tcl, precisamos criar algum tipo de processo receptor em nosso testbench VHDL. O código abaixo mostra um exemplo mínimo de tal testbench.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity interactive is

end interactive;

architecture sim of interactive is

-- Controlled by Tcl

signal trigger : std_logic := '0';

begin

process is

begin

wait until trigger = '1';

report "Triggered!";

end process;

end architecture;

O processo será ativado quando o

trigger sinal muda de algo para '1' . Ele irá imprimir “Triggered!” para o console quando isso acontece, permitindo-nos testar o conceito de controle de processos VHDL a partir do Tcl. Eu fiz exatamente isso é o console ModelSim. Os comandos emitidos, bem como a saída, podem ser visualizados na transcrição abaixo.

VSIM 1> run 10 ns; VSIM 2> force -deposit /trigger '1' VSIM 3> run 0 ns; # ** Note: Triggered! # Time: 10 ns Iteration: 0 Instance: /interactive VSIM 4> force -deposit /trigger '0' VSIM 5> run 10 ns;

Executei o testbench por 10 nanossegundos após iniciar a simulação.

Então, forcei o

trigger sinal para '1' . Na próxima linha, espero 0 nanossegundos. O objetivo disso é criar um ciclo delta. Quero que o processo seja acionado, mas não quero que passe nenhum tempo de simulação. Por fim, forço o

trigger sinal de volta para '0' antes de continuar o banco de testes. Podemos ver que o processo VHDL acordou após a linha “run 0 ns” e imprimiu “Triggered!” para o console.

Ler valores de sinal VHDL em tcl

Para ler os valores do sinal no ModelSim, você pode usar o comando “examinar”. Podemos, por exemplo, ler o valor do

trigger sinal usando este comando no console do ModelSim:VSIM 6> examine /trigger # 0

Você gostaria de atribuir o valor a uma variável Tcl ao usar “examinar” em um script. Vamos tentar isso no console do ModelSim:

VSIM 7> set triggerVal [examine /trigger] # 0

Então podemos, por exemplo, imprimir a variável usando o comando “puts” Tcl:

VSIM 8> puts "triggerVal: $triggerVal" # triggerVal: 0

Parando o simulador após cada teste

A maneira mais fácil de executar o teste por tempo suficiente para que o DUT reaja é simplesmente executar o simulador para um valor de tempo fixo. Por exemplo, se o DUT deve reagir após dois ciclos de clock, e o período de clock é de 10 nanossegundos, usaríamos o comando “run 20 ns” em nosso script Tcl.

Se o DUT não tiver um tempo de reação fixo, uma asserção VHDL pode ser usada para interromper a simulação e entregar o controle a uma função de retorno de chamada Tcl. No ModelSim, isso significaria definir um ponto de interrupção do seu script Tcl usando o comando “when”:

when [[-fast] [-id <id#>] [-label <label>] {<when_condition_expression>} {<command>}] Você também teria que definir uma função de retorno de chamada “onBreak” em Tcl que será executada quando o ponto de interrupção for atingido. A função “onBreak” é especificada na referência do comando ModelSim.

As desvantagens dos testes orientados por Tcl

Existem desvantagens de usar testbenches que dependem muito de scripts Tcl. Os mais aparentes são os problemas de velocidade e portabilidade.

Os testbenches orientados por Tcl funcionam iniciando e parando o simulador várias vezes para interagir com o código VHDL. Iniciar e parar a simulação para executar uma função Tcl no meio consome mais tempo do que executar um testbench VHDL continuamente. Enquanto o Tcl é uma linguagem interpretada, o VHDL é compilado no simulador e roda muito mais rápido que o Tcl.

Enquanto o Tcl é portátil para outros simuladores, os comandos específicos do simulador que você terá que usar, não são. Mesmo que você encontre os comandos equivalentes no outro simulador, eles podem funcionar de forma diferente. Os fornecedores de simuladores criam seu próprio conjunto de regras para os comandos aos quais dão suporte. Portanto, um testbench orientado a Tcl deve ser considerado menos portátil do que um testbench VHDL puro.

Novo curso de VHDL e FPGA

* Estou criando um novo curso de VHDL e FPGA que mergulhará extensivamente em testbenches. Você aprenderá como criar um projeto FPGA do zero. Após concluir o curso, você saberá como criar testbenches de autoverificação e como reutilizar o código para criar um testbench interativo.

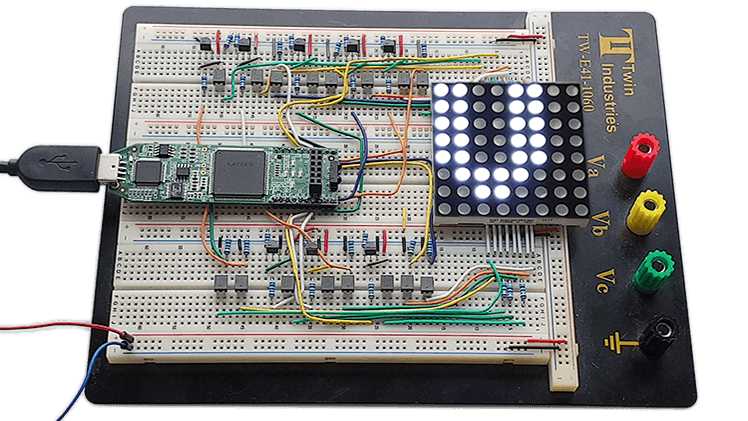

* Atualizado em 12 de outubro de 2020: Eu completei o curso. Clique na imagem abaixo para saber mais.

O produto que vamos criar é um módulo controlador de LED matricial. Usaremos a placa de desenvolvimento Lattice iCEstick de US$ 49. No final, implementaremos o design em uma placa de ensaio. Você poderá digitar no teclado do seu computador e os caracteres aparecerão na tela de LED de matriz de pontos controlada pelo FPGA.

Leia mais sobre o curso Dot Matrix VHDL e FPGA aqui!

Abre:

A ser decidido .

VHDL

- Tutorial - Introdução ao VHDL

- Exemplos de conversões de VHDL

- Declaração de Procedimento - Exemplo de VHDL

- Registros - Exemplo de VHDL

- Assinado vs. Não assinado em VHDL

- C# usando

- Como criar uma lista de strings em VHDL

- Como criar um testbench de autoverificação

- Projetor laser interativo usando sensores Zigbee

- Usando uma fresadora como torno