Nova ferramenta baseada em ML oferece otimização de fluxo de design de chip automatizado

Não há como debater o fato de que o design do chip está ficando cada vez mais complexo à medida que os clientes exigem mais recursos e dispositivos menores e menor consumo de energia. Para atender a essa demanda, os engenheiros estão ficando sobrecarregados e precisam de suporte para acompanhar a demanda e o desenvolvimento de produtos em tempo hábil.

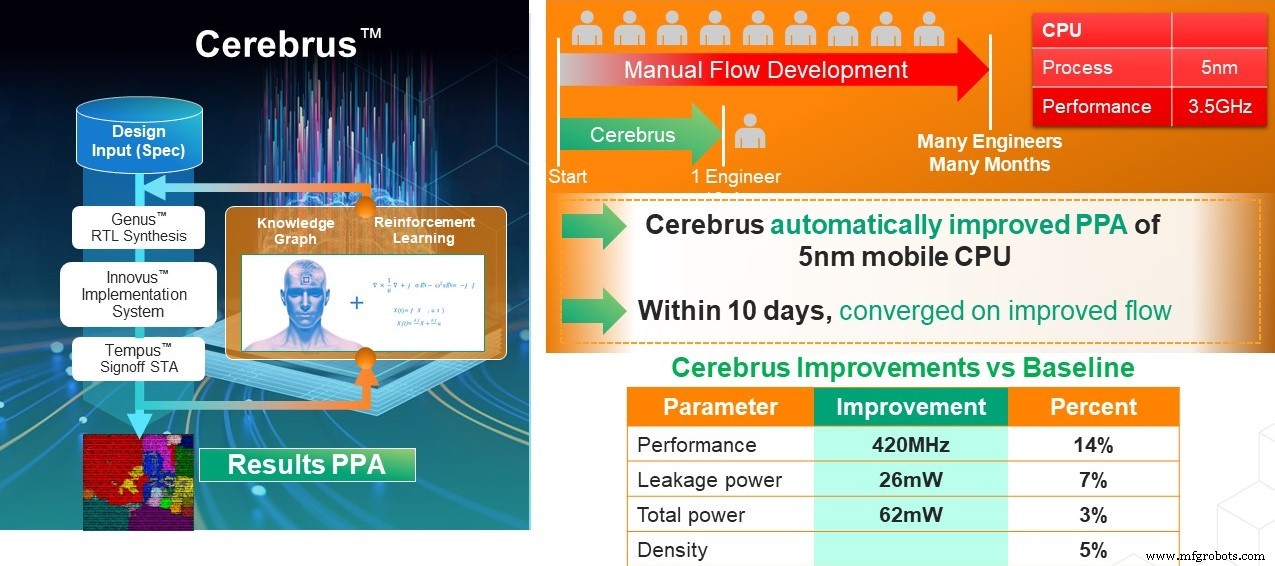

Para resolver isso, Cadence Design Systems introduziu uma nova ferramenta que usa aprendizado de máquina (ML) para conduzir o fluxo de implementação Cadence RTL para aprovação, entregando o que diz ser até 10X de produtividade e 20% de PPA (potência, desempenho e área ) melhorias para implementação. Seu novo Cerebrus Intelligent Chip Explorer oferece recursos de gerenciamento de recursos de computação em nuvem mais eficientes no local do que a exploração de design tradicional dirigida por humanos; e melhora o PPA e a produtividade em muitos nós e vários aplicativos finais, incluindo consumo, computação em hiperescala, comunicações 5G, design automotivo e móvel.

Em um briefing com embedded.com, Rod Metcalfe, diretor do grupo de gerenciamento de produtos da Cadence, disse:“Esta é a primeira ferramenta de otimização digital de fluxo total usando ML. Isso é importante, pois à medida que a complexidade do projeto aumenta, o projeto do chip exige mais recursos e inteligência, embora haja uma restrição no número de engenheiros disponíveis para realizar essas tarefas. Ainda vemos designers fazendo desenvolvimento de fluxo manual e iterando em torno do loop para atingir seus objetivos de design:isso requer uma grande quantidade de esforço de engenharia e não é escalonável. É aí que entra o Cerebrus, usando computação massiva para melhorar a produtividade para automação de design. ”

Metcalfe destacou um exemplo em que a Cerebrus precisava de apenas um engenheiro para convergir em um fluxo de design aprimorado em 10 dias para melhorar automaticamente o PPA de uma CPU móvel de 5 nm (veja o gráfico abaixo).

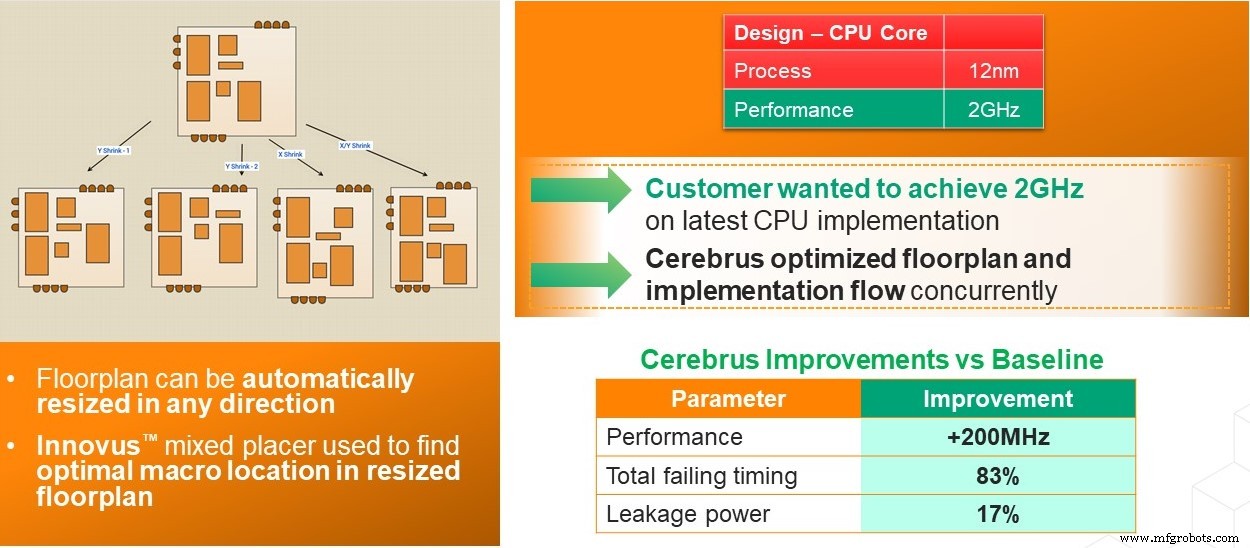

Outro exemplo em um nível superior é a otimização automatizada da planta baixa, como no gráfico abaixo:

O impacto de usar uma ferramenta baseada em ML como o Cerebrus é que as equipes de design têm uma maneira automatizada de reutilizar o conhecimento de design histórico - antes, elas gastariam muito tempo em reaprendizagem manual a cada novo projeto. Conseqüentemente, Cadence disse que a Cerebrus marca uma revolução da indústria de EDA com design de chip digital baseado em ML, onde as equipes de engenharia têm uma oportunidade maior de fornecer maior impacto em suas organizações porque podem descarregar processos manuais. À medida que a indústria continua avançando para nós avançados e o tamanho e a complexidade do projeto aumentam, o Cerebrus ajudará os projetistas a atingir as metas de PPA com mais eficiência.

Os primeiros endossos do cliente para a ferramenta vieram da Renesas e da Samsung Foundry.

Satoshi Shibatani, diretor do departamento de tecnologia de design digital na divisão compartilhada de P&D EDA da Renesas, disse:“Para maximizar com eficiência o desempenho de novos produtos que usam nós de processo emergentes, os fluxos de implementação digital usados por nossa equipe de engenharia precisam ser atualizados continuamente. A otimização automatizada do fluxo de projeto é crítica para realizar o desenvolvimento de produtos com um rendimento muito mais alto. O Cerebrus, com seus recursos inovadores de ML e as ferramentas Cadence RTL-to-signoff, forneceram otimização de fluxo automatizada e exploração de planta baixa, melhorando o desempenho do projeto em mais de 10%. ”

Enquanto isso, na Samsung Foundry, seu vice-presidente de tecnologia de design, Sangyun Kim, disse:“À medida que continuamos a implantar nós de processo atualizados, a eficiência de nosso programa de co-otimização de tecnologia de design (DTCO) é muito importante. . Como parte de nossa parceria de longo prazo com a Cadence, a Samsung Foundry usou o Cerebrus e o fluxo de implementação digital da Cadence em vários aplicativos. Observamos uma redução de energia de mais de 8% em alguns de nossos blocos mais críticos em apenas alguns dias, em comparação com muitos meses de esforço manual. Além disso, estamos usando o Cerebrus para dimensionamento automatizado da rede de distribuição de energia da planta baixa, o que resultou em um tempo de projeto final mais de 50% melhor.

Os principais recursos e benefícios do Cerebrus são:

- ML de reforço : encontra rapidamente soluções de fluxo que os engenheiros humanos podem não tentar ou explorar naturalmente, melhorando o PPA e a produtividade.

- Reutilização do modelo de ML :permite que o aprendizado de design seja aplicado automaticamente a designs futuros, reduzindo o tempo para obter melhores resultados.

- Produtividade aprimorada :permite que um único engenheiro otimize o fluxo completo de RTL para GDS automaticamente para muitos blocos simultaneamente, permitindo que equipes de projeto completas sejam mais produtivas.

- Computação distribuída massivamente :fornece exploração de design escalonável local ou baseado em nuvem para otimização de fluxo mais rápida.

- Interface fácil de usar: O poderoso cockpit do usuário permite análises de resultados interativas e gerenciamento de execução para obter insights valiosos sobre as métricas de design.

Cerebrus é parte do fluxo total digital Cadence mais amplo, trabalhando perfeitamente com a solução de síntese Genus, sistema de implementação Innovus, solução de aprovação de temporização Tempus, solução de energia Joules RTL, solução de integridade de energia Voltus IC e sistema de verificação Pegasus para fornecer aos clientes um caminho rápido para projetar o fechamento e melhor previsibilidade.

Integrado

- Mudando para um novo nível de Edge AI

- Pulsic oferece visualização do layout do chip analógico em tempo real no editor de esquemático

- SIMULIA Engenharia e Design de Pneus

- Pensilvânia oferece novo financiamento para ajudar os alunos da Filadélfia a descobrirem oportunidades de manufatura

- Engenharia de projeto de pré-formas personalizadas

- Bar/Chucker com design de frente aberta e muito mais

- Novo projeto de transistor disfarça hardware de chip de computador chave para proteção contra hackers

- Sandvik apresenta novo conceito de torneamento

- O Cenário de Integração da Nova Linha

- Como adicionar uma nova ferramenta