Criação de interconexões de alto desempenho com várias gerações PCIe

PCI Express e a fome de largura de banda

Como um meio de conexão de computação, processadores host integrados e personalizados a periféricos "terminais", como portas Ethernet, portas USB, placas de vídeo e dispositivos de armazenamento, PCI Express® (PCIe®) se tornou a referência de interconexão de alto desempenho. Aproveitando a comunicação serial de alta velocidade, o PCIe oferece conectividade ponto a ponto eficiente e - aumentando a contagem de canais e a taxa de sinalização - largura de banda de interface escalonável.

A especificação PCIe 1.0 foi publicada em 2002, operando a 2,5 giga-transferências por segundo (GT / s), dando uma largura de banda de interface x16 total de 8 GByte / s. A largura de banda foi posteriormente dobrada em 2006 com a chegada das especificações PCIe 2.0 de segunda geração e novamente em 2010, quando o PCIe 3.0 aumentou a largura de banda para 32 GByte / s para atender às demandas cada vez maiores impostas pelos principais aplicativos contemporâneos, incluindo PC de última geração, jogos, computação empresarial e rede.

PCI Express se tornou a referência de interconexão de alto desempenho para uma ampla gama de designs de sistema.

(Fonte:Diodes Inc.)

Mais recentemente, a rápida disseminação de serviços baseados em nuvem, como mídia social e streaming de vídeo, introduziu requisitos novos e mais exigentes para conectividade de alta velocidade em data centers de grande escala.

Agora, com a era da IoT, sensores em rede instalados em cidades e infraestruturas inteligentes, fábricas inteligentes e outros ativos industriais, edifícios comerciais e residenciais e vestíveis para rastreamento médico e de condicionamento físico estão configurados para gerar grandes quantidades de dados para data centers em hiperescala para capturar, armazenar, processar e analisar. Essas forças estão impulsionando a demanda das próximas gerações de PCIe para conectar com eficiência os servidores do data center a Ethernet de alta velocidade, armazenamento conectado à rede e aceleradores de IA.

Os carros conectados aumentarão ainda mais a carga de dados, adicionando pressão em tempo real, para permitir níveis mais elevados de direção autônoma e, por fim, veículos totalmente autônomos. Atrás dos data centers, o treinamento de redes neurais para inferência de IA é uma tarefa de computação intensiva que expõe nitidamente os gargalos nas comunicações periféricas.

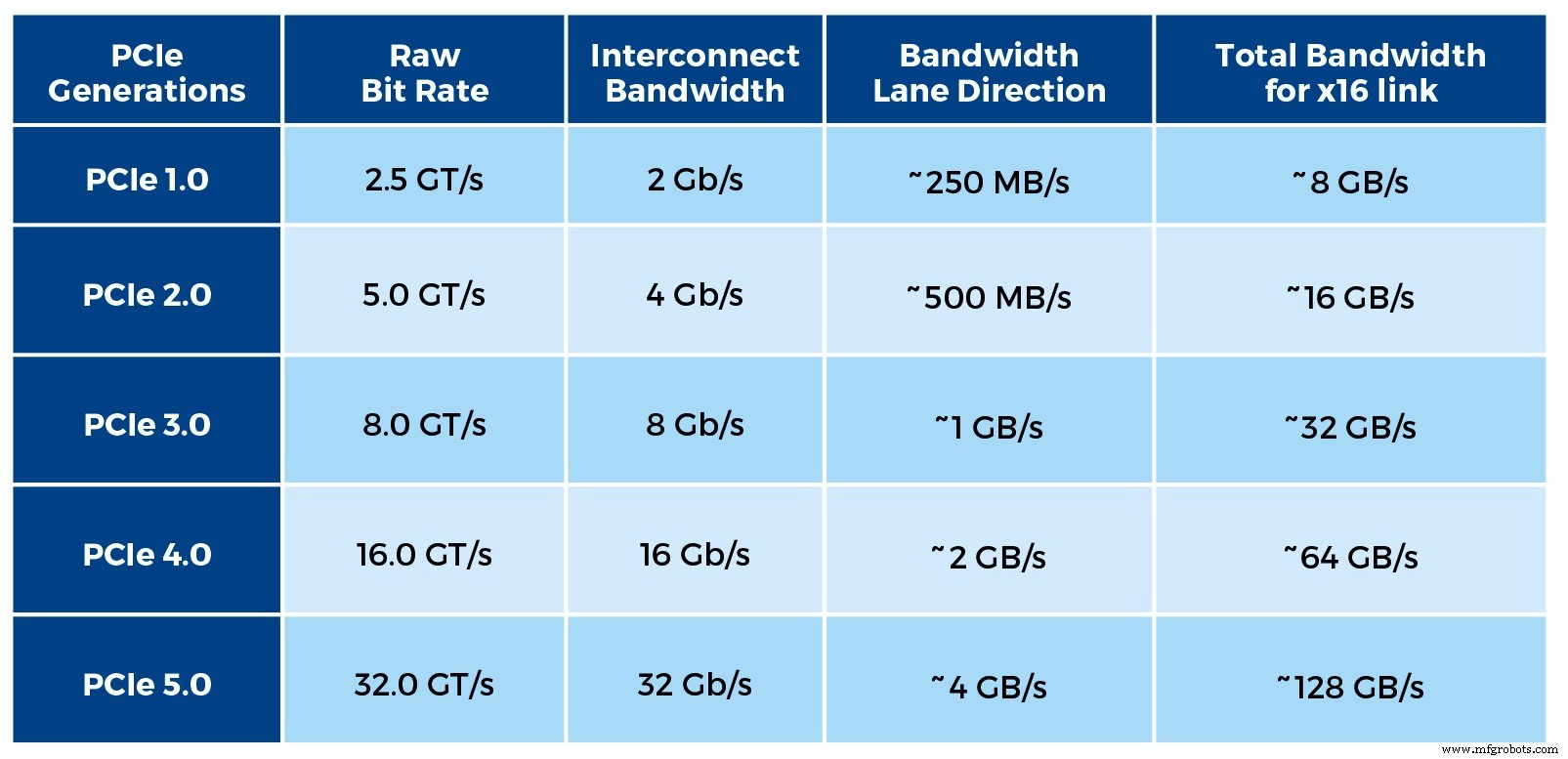

Como esses vários fatores agora entram em jogo, é hora de o PCIe avançar novamente. O PCIe 4.0, anunciado em 2017, foi rapidamente seguido pela publicação do PCIe 5.0 em 2019. A Figura 1 mostra as velocidades agregadas oferecidas por cada versão do PCIe.

Figura 1:Velocidades agregadas oferecidas pelas versões PCIe (Fonte:Diodes Inc.)

Espera-se que o PCIe 5.0 seja amplamente utilizado, pois os principais data centers fazem a transição de Ethernet de 100 Gb para a especificação mais recente de 400 Gb. Na prática, os aumentos na largura de banda PCIe mais ou menos acompanharam os avanços nas velocidades Ethernet, idealmente mantendo um equilíbrio entre os dois padrões para ajudar a evitar gargalos de desempenho.

Padrões PCI “legados” permanecem atuais

Conforme os produtos PCIe 5.0 começam a entrar no mercado, e com o recente anúncio do PCI Special Interest Group (PCI-SIG) de que o trabalho começou na próxima geração, PCIe 6.0 para conclusão em 2021, PCIe é o protocolo de escolha para desempenho - Comunicações periféricas famintas, para o futuro previsível.

Ao mesmo tempo, a compatibilidade com versões anteriores é um ponto forte da linhagem PCIe. Como não há data de expiração para as especificações PCIe, várias gerações podem coexistir no mercado e até mesmo no mesmo aplicativo. Esta é uma vantagem para designers de sistema:enquanto sucessivas novas gerações de PCIe emergem para atender aos requisitos cada vez mais exigentes por largura de banda, as iterações anteriores continuam a agregar valor em um grande número de cenários, como computação pessoal, jogos e alguns aplicativos de computação empresarial e rede.

Resolvendo Desafios de Implementação

A compatibilidade retroativa entre as várias gerações de PCIe permite que os sistemas se beneficiem de velocidades de transferência mais altas à medida que o novo silício se torna disponível, com alterações mínimas de design. Por outro lado, velocidades crescentes de sinal colocam pressão extra nas margens do sinal e podem aumentar a complexidade do projeto. Além disso, há uma necessidade clara de soluções que permitam a ponte de e para PCIe, não apenas entre interfaces legadas, mas também outras interfaces, como portas USB ou gráficas.

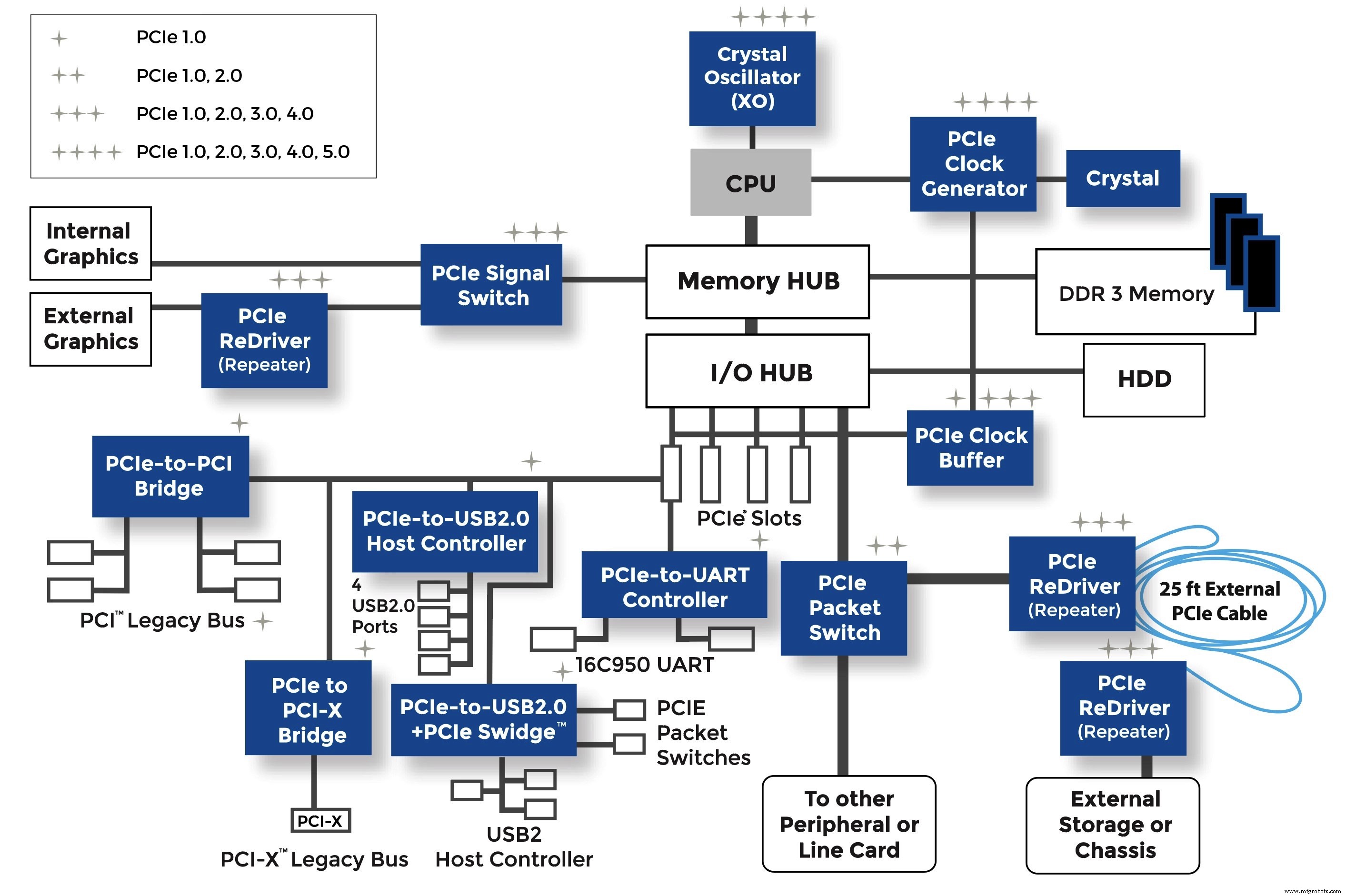

Para lidar com esses desafios, os designers precisam de acesso a dispositivos que suportam várias gerações de PCIe, como geradores de clock, buffers de clock, controladores, comutadores / pontes de pacotes, chips ReDriver ™ e multiplexadores de alta velocidade mostrados na figura 2.

clique para ampliar a imagem

Figura 2:Um exemplo das soluções PCIe disponíveis na Diodes Inc. (Fonte:Diodes Inc.)

Os chips ReDriver podem fornecer uma solução econômica e conveniente para aumentar a integridade do sinal em sistemas de alta velocidade. Usando técnicas como equalização e pré-ênfase, com um driver de saída que introduz latência mínima, o ReDriver compensa as perdas da linha de transmissão para restaurar a margem do sinal e minimizar o jitter para garantir uma baixa taxa de erro de bit no receptor. Comparado com um retimer, que integra funções adicionais, incluindo clock e recuperação de dados, um ReDriver apresenta baixo atraso e é relativamente econômico e fácil de implementar. A Figura 2 mostra como um PCIe ReDriver pode ser usado onde os sinais precisam ser conduzidos por uma trilha de PCB mais longa, como para uma placa gráfica externa ou via cabo para armazenamento externo. Esses ReDrivers são totalmente compatíveis com as versões anteriores, suportando todas as gerações anteriores de PCIe.

Bridges e switches satisfazem os requisitos de interface entre dispositivos host e endpoint de vários tipos. Uma ponte de pacote normalmente fornecerá uma interface entre duas camadas no modelo de referência OSI ou entre dois protocolos. A Figura 2 também mostra como uma ponte pode ser usada para conectar entre PCIe e padrões PCI legados, incluindo PCI-X, ou portas USB ou uma interface de barramento UART. Os switches de pacote são dispositivos multiport / multilane normalmente usados para expandir um único complexo raiz para várias portas com várias vias para acessar outros sistemas de mesmo nível, como um periférico ou placa de linha.

Além de pontes de pacotes individuais e switches com várias configurações de porta e recursos de tradução, as funcionalidades de um switch de pacote PCIe e ponte PCIe-para-USB2.0 são combinadas em dispositivos como PI7C9X442SL PCI Express-para-USB 2.0 'swidge da Diodes Incorporated '. Este dispositivo multifuncional pode se espalhar de uma porta PCIe x1 upstream para duas portas x1 downstream e quatro USB 2.0, e permite que o processador host do sistema acesse vários dispositivos PCIe e USB simultaneamente.

Empresas como a Diodes Inc. podem oferecer um portfólio de multiplexadores / demultiplexadores passivos bidirecionais PCIe 1.0, PCIe 2.0 ou PCIe 3.0 para conectar uma única pista PCIe a múltiplas pistas para expansão da largura de banda para gráficos ou computação. Esses dispositivos também podem ser usados para habilitar conexões de uma única interface multiprotocolo.

Os buffers de clock podem normalmente ter um único sinal de referência como uma entrada e produzir várias saídas para uma distribuição mais ampla em torno de um PCB. Os CIs de buffer de clock estão disponíveis em uma variedade de configurações e o Diodes oferece um design PLL proprietário que garante que o jitter permaneça dentro dos requisitos do PCIe. Os geradores de clock podem gerar um sinal de clock em uma frequência específica com jitter de saída muito baixo, tornando-os adequados para PCIe e também para outros relógios de sistema. Os projetistas podem encontrar uma ampla gama de dispositivos adequados, como geradores de clock e buffers PCIe 4.0 de 1,8 V PI6CG18xxx e 1,5 V PI6CG15xxx PCIe 4.0 em configurações de 2, 4 e 8 canais, que são compatíveis com todas as gerações PCIe anteriores. Ao integrar terminações no chip, esses dispositivos economizam quatro resistores externos por saída, eliminando até 32 componentes da lista de materiais.

Conclusão

PCIe é a interconexão de alto desempenho ideal para aplicativos de computação embarcada e desktop a conectividade de data center de alta largura de banda e treinamento de rede neural. Os projetistas podem tirar proveito da longa vida útil dos padrões PCIe anteriores, com compatibilidade retroativa entre especificações legadas e de geração posterior, para atender a diversos requisitos de sistema de maneira econômica. Com acesso a um portfólio de dispositivos contendo funções como bridges, buffers, ReDrivers, switches e ICs mux / demux, os designers podem fornecer soluções eficientes para aplicativos exigentes.

Integrado

- Fabricação de aditivos líquidos:Construindo objetos 3D com líquido

- Criação de Blockchain Híbrido / Aplicativos em Nuvem com Ethereum e Google

- Criação de aplicativos móveis sem servidor com React Native e AWS

- TECHWAY:Plataforma Kintex-7 FPGA PCIe para impulsionar o desempenho da taxa de dados com 12 links HSS

- Construindo robôs com Raspberry Pi e Python

- Construindo um segway com Raspberry Pi

- Nexam fornecerá Diab com Nexamite de melhoria de propriedades para espuma PET de alto desempenho

- Compostos de resina de engenharia de alto desempenho com conteúdo reciclado

- Como a IoT pode ajudar com Big Data HVAC:Parte 2

- Construindo o futuro da experiência do funcionário com automação inteligente