Sincronização e distribuição de redefinição assíncrona - ASICs e FPGAs

A falta de coordenação entre reinicializações assíncronas e relógios lógicos síncronos leva a falhas intermitentes na inicialização. Nesta série de artigos, discutimos os requisitos e desafios do reset assíncrono e exploramos soluções avançadas para projetos ASIC vs FPGA.

Reinicializações assíncronas são tradicionalmente empregadas em projetos VLSI para trazer o circuito síncrono a um estado conhecido após a inicialização. A operação de liberação de reinicialização assíncrona deve ser coordenada com o sinal de relógio lógico síncrono para eliminar falhas de sincronização devido à possível contenção entre a reinicialização e o relógio. A falta dessa coordenação leva a falhas intermitentes na inicialização. O problema se agrava quando grandes projetos de domínio de múltiplos relógios são considerados. Além dos problemas de sincronização, a distribuição de um reset assíncrono para milhões de flip-flops é um desafio, exigindo técnicas semelhantes ao CTS (Clock Tree Synthesis) e exigindo área e recursos de roteamento semelhantes.

Os requisitos e desafios da reinicialização assíncrona são revisados, com foco nos problemas de sincronização e distribuição. As desvantagens das soluções clássicas para redefinir a sincronização (redefinir a sincronização da origem da árvore) e distribuição (redefinir a síntese da árvore) são discutidas. Soluções avançadas para convergência de temporização mais rápida e simples e sincronização e distribuição de reset mais confiáveis são apresentadas. Diferentes abordagens para projetos ASIC e FPGA são detalhadas.

A Parte 1 descreve os problemas em torno das reconfigurações assíncronas e descreve abordagens para resolver esses problemas. A Parte 2 (este artigo) discute soluções adicionais para a redefinição assíncrona correta em ASIC e FPGA. Alguns casos especiais úteis são discutidos na Parte 3.

2. Técnicas de convergência de tempo de redefinição assíncrona

Um dos principais problemas discutidos na Parte 1 foi a complexidade da liberação de reinicialização para projetos grandes (com uma rede de distribuição de reinicialização de alta latência), especialmente quando um ciclo de clock curto é empregado. A convergência de tempo com base na otimização STA padrão leva a um design caro e, em alguns casos, é até impossível. Aqui, discutimos duas técnicas que atenuam esse problema de tempo. Ambas as técnicas são aplicáveis para projetos ASIC e FPGA.

2.1. Pipelining de redefinição assíncrona

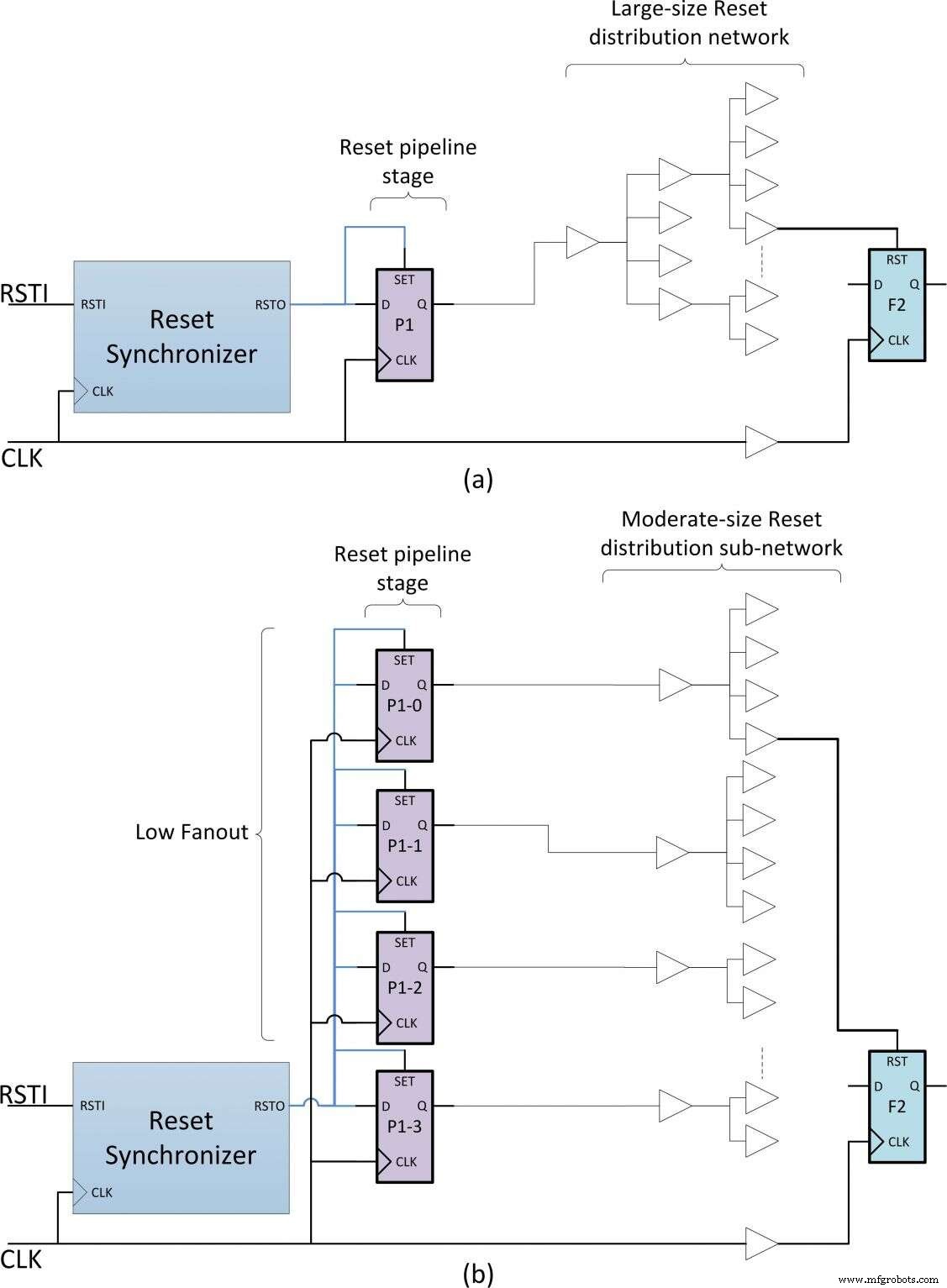

Uma maneira de lidar com o problema de temporização da liberação de reinicialização assíncrona é trocar a latência de liberação de reinicialização por uma temporização mais relaxada. Isso pode ser conseguido canalizando a árvore de redefinição da seguinte maneira. Após cada sincronizador, um estágio flip-flop P1 de conjunto assíncrono adicional é incluído na linha de reinicialização (Figura 6a). Ambas as entradas SET e D do flip-flop são conectadas ao RSTO de reset alto ativo vindo do sincronizador de reset. Na liberação RSTO, as condições de configuração e retenção são satisfeitas para as entradas P1 D e SET, uma vez que são restritas como caminhos síncronos regulares.

clique para ampliar a imagem

Figura 6:Reinicialização assíncrona com pipelining (Fonte:Circuitos vSync)

A operação funcional do novo esquema é semelhante ao normal descrito na Parte 1 (Figura 3d), exceto por uma latência de ciclo único adicional na liberação de reinicialização. A latência de reinicialização mais alta incorrida por essa técnica geralmente é aceitável para a maioria dos aplicativos, pois ocorre apenas uma vez a cada inicialização.

Uma parte complementar desta técnica cobre as restrições de design. Embora os flip-flops do sincronizador devam ser restringidos contra a duplicação, a fim de evitar problemas de caminho de reconvergência, conforme descrito na Parte 1, o estágio de pipeline P1 está sujeito à restrição MAX_FANOUT. Um exemplo de restrição máxima de fanout é mostrado na Figura 6b. O flip-flop P1 é automaticamente duplicado pela ferramenta de síntese, criando quatro sub-redes para a distribuição de reinicialização. Cada sub-rede tem uma latência mais baixa do que a rede original, atendendo ao requisito de tempo para a liberação de reinicialização. Além disso, a saída do sincronizador de reinicialização atende facilmente a fanout de oito.

Essa técnica de redefinição assíncrona de pipelining é escalonável para qualquer tamanho de design e não requer alterações quando o design está mudando, já que a ferramenta de síntese duplica automaticamente o estágio P1, mantendo a sub-rede de redefinição de latência moderada limitada. O fanout de estágio P1 duplicado para a saída do sincronizador é geralmente pequeno e não causa violações de temporização. No entanto, quando um único estágio de pipeline não leva à convergência de tempo, estágios de pipeline adicionais P2 - PN podem ser incluídos e restringidos com diferentes restrições MAX_FANOUT.

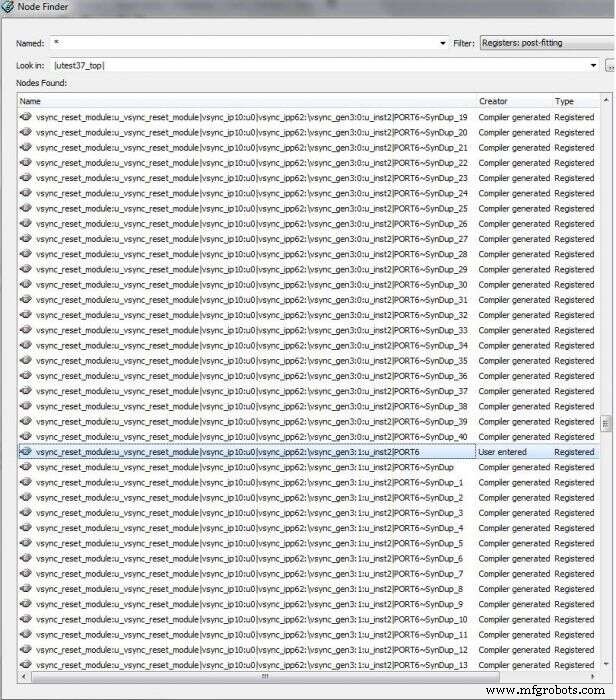

Um exemplo dessa técnica aplicada a um projeto real é mostrado na Figura 7. O registro de estágio P1, denominado PORT6, foi automaticamente duplicado cerca de 40 vezes pela ferramenta de síntese [6] para atender à restrição MAX_FANOUT. Cada uma das 40 sub-redes atendeu ao momento de seu fanout local.

clique para ampliar a imagem

Figura 7:Exemplo de pipelining de redefinição assíncrona (Fonte:Circuitos vSync)

Integrado

- Estruturas e classes em C ++

- Caixas de correio:introdução e serviços básicos

- Semáforos:introdução e serviços básicos

- Anvo-Systems e Mouser assinam acordo de distribuição

- Mouser e Inventek Systems anunciam acordo de distribuição global

- Rutronik e AP Memory assinam acordo de distribuição global

- Distribuição separada da Albis Plastics e Negócios de Compostos

- A arte e a ciência da seleção de sites de distribuição

- Seis maneiras de cortar emissões em armazenamento e distribuição

- Grupo RG fecha parceria de distribuição e integração com AutoGuide Mobile Robots