Compilações de GPU de código aberto em RISC-V

Um grupo de entusiastas está propondo um novo conjunto de instruções gráficas projetadas para gráficos 3D e processamento de mídia. Essas novas instruções são construídas no conjunto de instruções do vetor base RISC-V. Eles irão adicionar suporte para novos tipos de dados que são gráficos específicos como extensões em camadas no espírito da arquitetura do conjunto de instruções RISC-V (ISA). Vetores, matemática transcendental, pixel e texturas e operações de buffer Z / Frame são suportados. Pode ser uma CPU-GPU ISA fundida. O grupo está chamando-o de RV64X, pois as instruções serão de 64 bits (32 bits não serão suficientes para suportar um ISA robusto).

Por que agora?

O mundo tem muitas GPUs para escolher, por que isso? Porque, diz o grupo, as GPUs comerciais são menos eficazes em atender a necessidades incomuns, como recorte de frustum 3D de fase dupla, HPC adaptável (FFTs de profundidade de bit arbitrária), SLAM de hardware. Eles acreditam que a colaboração fornece padrões flexíveis, reduz o esforço de 10 a 20 homens / ano de outra forma necessário e ajudará na verificação cruzada para evitar erros.

A equipe afirma que sua motivação e objetivos são impulsionados pelo desejo de criar um design pequeno e com eficiência de área, com capacidade de programação e extensibilidade personalizadas. Deve oferecer propriedade e desenvolvimento de IP de baixo custo, e não competir com ofertas comerciais. Ele pode ser implementado em alvos FPGA e ASIC e será gratuito e de código aberto. O projeto inicial será voltado para microcontroladores de baixa potência. Ele será compatível com Khronos Vulkan e, com o tempo, oferecerá suporte a outras APIs (OpenGL, DirectX e outros).

O hardware final será um núcleo RISC-V com uma unidade funcional de GPU. Para o programador, parecerá uma única peça de hardware com instruções longas de 64 bits codificadas como instruções escalares. O modelo de programação é um SIMD aparente, ou seja, o compilador gera SIMD a partir de opcodes escalares prefixados. Incluirá problema variável, back-end SIMD predicado, front-end vetorial, exceções precisas, sombra de ramificação e muito mais. Não haverá nenhuma necessidade do mecanismo de chamada RPC / IPC para enviar chamadas API 3D de / para o espaço de memória da CPU não utilizado para o espaço de memória da GPU e vice-versa, diz a equipe. E estará disponível como ponto fixo de 16 bits (ideal para FPGAs), bem como ponto flutuante de 32 bits (ASICs ou FPGAs).

O design empregará o formato Vblock (do esforço da GPU Libre):

- É um pouco como VLIW (mas não realmente)

- Um bloco de instruções é pré-fixado com tags de registro que fornecem contexto extra para instruções escalares dentro do bloco

- Os sub-blocos incluem:comprimento do vetor, swizzling, substituições de vetor / largura e predicação.

- Tudo isso é adicionado aos opcodes escalares

- Não há opcodes vetoriais (e não há necessidade de nenhum)

- No contexto vetorial, funciona assim:se um registro é usado por um opcode escalar, e o registro está listado no contexto vetorial, o modo vetorial é ativado

- A ativação resulta em um for-loop de nível de hardware emitindo várias operações escalares contíguas (em vez de apenas uma).

- Os implementadores são livres para implementar o loop da maneira que desejarem:SIMD, vários problemas, execução única.

O projeto empregará escalares (fixos e flutuantes de 8, 16, 24 e 32 bits), bem como transcendentais (sincos, atan, pow, exp, log, rcp, rsq, sqrt, etc.). Os vetores (RV32-V) suportarão operações de vetor de 2-4 elementos (8, 16 ou 32 bits / elemento), junto com instruções especializadas para um pipeline geral de renderização de gráficos 3D para pontos, pixels, texels (vetores essencialmente especiais )

- pontos XYZW (fixos e flutuantes de 64 e 128 bits)

- pixels RGBA (pixels de 8, 16, 24 e 32 bits)

- texels UVW (8, 16 bits por componente)

- Luzes e materiais (Ia, ka, Id, kd, Is, ks ...)

As matrizes serão 2 × 2, 3 × 3 e 4 × 4 matrizes serão suportadas como um tipo de dados nativo junto com estruturas de memória para suportá-los para vetores de atributos e serão essencialmente representadas em uma matriz 4 × 4.

Entre as vantagens do ISA fundido de CPU-GPU está a capacidade de implementar um pipeline gráfico padrão em microcódigo, fornecer suporte para sombreadores personalizados e implementar extensões de rastreamento de raio. Ele também oferece suporte a vetores para simulações numéricas com tipos de dados inteiros de 8 bits para IA e aprendizado de máquina.

Rasterizadores personalizados podem ser implementados como splines, superfícies SubDiv e patches.

O projeto será flexível o suficiente para implementar estágios de pipeline customizados, estágios de buffer de geometria / pixel / frame customizados, tessellators customizados e operações de instanciação customizadas.

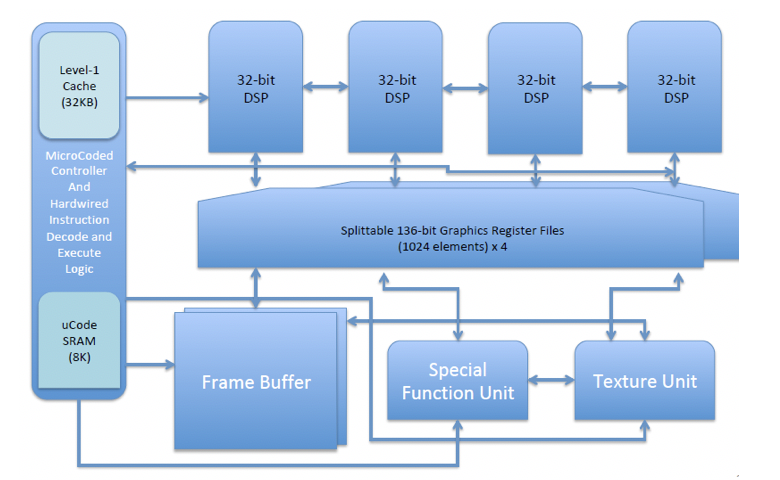

Diagrama de blocos RV64X

A implementação de referência RV64X incluirá:

- Cache de instrução / dados SRAM (32 KB)

- Microcódigo SRAM (8 KB)

- Decodificador de instrução de função dupla

- Implementação de RV32V e X com fio

- Decodificador de instrução micro-codificado para ISA personalizado

- Quad Vector ALU (32 bits / ALU — fixo / flutuante)

- Arquivos de registro de 136 bits (elementos 1K)

- Unidade de função especial

- Unidade de textura

- Frame Buffer local configurável

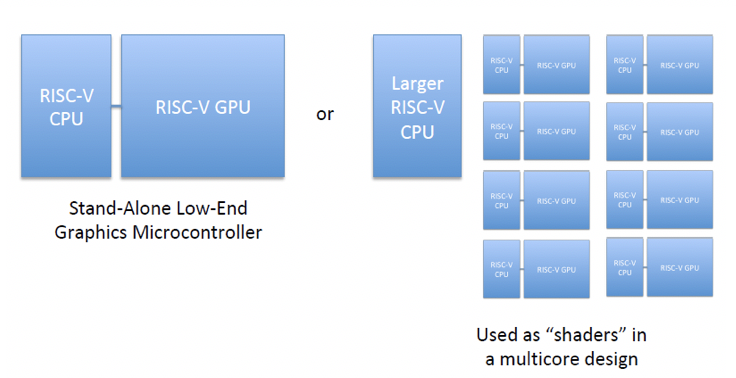

O design deve ser escalonável conforme indicado abaixo.

Design escalável do RV64X

O design RV64X tem várias ideias inovadoras, incluindo CPU-GPU ISA unificada fundida, registros configuráveis para tipos de dados personalizados e micro-código baseado em SRAM definido pelo usuário para extensões de hardware personalizadas definidas pelo aplicativo para:

- Estágios de rasterizador personalizado

- Traçado de raio

- Aprendizado de máquina

- Visão computacional

O mesmo design funciona como um microcontrolador gráfico autônomo ou unidade de sombreador escalável, e os formatos de dados suportam implementações nativas de FPGA ou ASIC.

Por que há necessidade de gráficos abertos?

Os desenvolvedores acham que a maioria dos processadores gráficos cobre o topo de linha, como jogos, negociação de alta frequência, visão computacional e aprendizado de máquina. Eles acreditam que o ecossistema carece de um núcleo gráfico escalonável para aplicativos mais convencionais, como quiosques, outdoors, jogos de cassino, brinquedos, robótica, eletrodomésticos, wearables, interfaces homem-máquina industriais, infoentretenimento e grupos de medidores automotivos. Enquanto isso, linguagens de programação especiais devem ser usadas para programar núcleos de GPU para OpenGL, OpenCL, CUDA, DirectCompute e DirectX.

Uma extensão gráfica para RISC-V resolveria a escalabilidade e as cargas de vários idiomas, permitindo um nível mais alto de inovação de caso de uso.

Próximas etapas

Esta é uma especificação muito antiga, ainda em desenvolvimento e sujeita a alterações com base nas informações das partes interessadas e da indústria. A equipe estabelecerá um fórum de discussão. Um objetivo imediato é construir uma implementação de amostra com simulador de conjunto de instruções, uma implementação FPGA usando IP de código aberto e IP personalizado projetado como um projeto de código aberto. Demonstrações e benchmarks estão sendo projetados. Os desenvolvedores interessados em participar devem contratar o Atif Zafar.

Quanto à GPU Libre-RISC 3D, o objetivo da organização é projetar uma CPU, VPU e GPU híbrida. Não é, como amplamente relatado, uma “GPU exclusiva e dedicada”. Existe a opção de criar um produto de GPU independente. Seu objetivo principal é projetar um SoC de processador all-in-one completo que por acaso inclua um VPU e GPU licenciados pela Libre.

O que achamos?

A população de fornecedores de GPU está aumentando. Agora temos mais de uma dúzia.

AppleLibre-RISC-V 3D GPUQualcommAMDNvidiaRISC-V GraphicsArmIntelThink-SiliconDMPJingjia MicroVeriSilcionImagination Technologies

Um aplicativo não listado como um usuário potencial de uma GPU pequena, flexível e gratuita inclui criptomoeda e mineração.

Se o objetivo da comunidade RISC-V for emular os fornecedores de IP, como Arm e Imagination, então podemos esperar ver designs de DSP, ISP e DP. Há pelo menos uma proposta Open DSP; talvez possa ser trazido para a comunidade RISC-V.

Levará pelo menos dois anos antes que qualquer implementação de hardware surja. Um dos candidatos mais lógicos para a adoção deste design é Xilinx, que agora está usando Arm’s Mali em seu design Zynq. Também esperamos ver várias implementações saindo da China.

>> Este artigo foi publicado originalmente em nosso site irmão, EE Times.

Jon Peddie , um pioneiro na indústria gráfica, é presidente da Jon Peddie Research.

Jon Peddie , um pioneiro na indústria gráfica, é presidente da Jon Peddie Research. Para obter mais informações sobre o Embedded, assine o boletim informativo semanal da Embedded por e-mail.

Integrado

- Introdução à terminologia de código aberto

- Código aberto e a IoT:inovação por meio da colaboração

- Cimeira RISC-V:destaques da agenda

- Segurança industrial IoT construída em hardware

- Um log de projeto para FirePick Delta, a MicroFactory de código aberto

- AT&T, Tech Mahindra colaboram na nova plataforma de IA de código aberto

- Riscos de software:Protegendo código aberto em IoT

- Ferramentas de desenvolvimento de IoT de código aberto vs. Ferramentas com suporte do fornecedor

- A MassRobotics publica os primeiros padrões de interoperabilidade de robôs móveis autônomos de código aberto do mundo

- A necessidade de código aberto na borda (eBook)