As soluções CXL 2.0 / PCIe 5.0 desbloqueiam gargalos heterogêneos de computação e dados

A Astera Labs, startup de semicondutores da Fabless, anunciou novas soluções de conectividade CXL 2.0 e PCIe 5.0 especialmente desenvolvidas para desbloquear arquiteturas de computação heterogêneas e lidar com cargas de trabalho sensíveis à latência no data center. A empresa disse que o objetivo dessas novas soluções é resolver os gargalos de desempenho de todo o sistema em aplicativos centrados em dados.

A proliferação de dados e a integração de cargas de trabalho especializadas - como inteligência artificial (IA) e aprendizado de máquina (ML) - exigem aceleradores desenvolvidos para trabalhar lado a lado com CPUs de uso geral na mesma placa-mãe ou no mesmo rack enquanto compartilhando um espaço de memória comum. A interconexão CXL 2.0 é a chave para habilitar essas topologias de sistema coerentes de cache.

O primeiro produto no novo portfólio da Astera Labs é seu portfólio de retimer inteligente Aries Compute Express Link (CXL 2.0) (PT5161LX, PT5081LX) para conectividade CXL.io de baixa latência, que está sendo testado ativamente para clientes estratégicos. O CEO da empresa, Jitendra Mohan, disse:"Com nossa expansão no ecossistema CXL, a Astera Labs está dando outro salto gigante para fornecer soluções específicas que desbloqueiam topologias complexas de computação heterogênea e sistema de desagregação compostável."

A especificação CXL 2.0 foi lançada pelo CXL Consortium em novembro de 2020. CXL é uma interconexão aberta padrão da indústria que oferece coerência e semântica de memória usando alta largura de banda e conectividade de baixa latência entre o processador host e dispositivos como aceleradores, buffers de memória e dispositivos inteligentes Dispositivos de E / S. A especificação CXL 2.0 adiciona suporte para comutação para fan-out para conectar a mais dispositivos; pooling de memória para maior eficiência de utilização de memória e fornecimento de capacidade de memória sob demanda; e suporte para memória persistente. Tudo isso enquanto preserva os investimentos da indústria, oferecendo compatibilidade total com versões anteriores do CXL 1.1 e 1.0.

O presidente do CXL Consortium, Barry McAuliffe, disse:“Como um dos primeiros membros do CXL Consortium, a Astera Labs contribuiu com sua experiência em conectividade para o avanço do padrão CXL. É ótimo ver sua primeira implementação de silício CXL chegar ao mercado em apoio a um ecossistema CXL de rápido crescimento. ”

Novas soluções PCIe 5.0 em colaboração com Intel

A Astera Labs também anunciou a disponibilidade de um novo modo de baixa latência em seu portfólio de retimer inteligente Aries para conectividade PCIe com processadores escalonáveis Intel Xeon. Este desenvolvimento foi o resultado de uma estreita colaboração com a Intel Corporation para reduzir ainda mais a latência em links PCIe para sub-10ns e aprimorar o desempenho em cargas de trabalho centradas em dados. A Astera Labs afirmou que é o primeiro fornecedor a demonstrar interoperabilidade robusta de PCIe 5.0 com os processadores escaláveis Intel Xeon de codinome ‘Sapphire Rapids’.

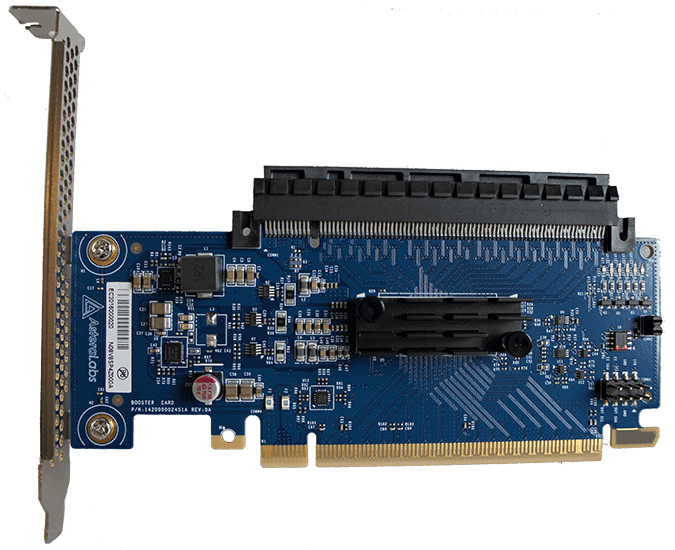

Ao mesmo tempo, também foi lançada uma nova placa de expansão Smart retimer plug-and-play para aplicações PCIe / CXL, chamada Equinox. Também desenvolvido em parceria com a Intel, a placa e o firmware específico associado simplificarão o desenvolvimento de sistemas habilitados para PCIe 5.0 com os mais recentes processadores escalonáveis Xeon da Intel. Isso representa a transição da Astera Labs para oferecer placas plug-and-play fáceis de usar para implementar rapidamente topologias de sistema complexas.

“PCIe Gen5 e CXL são tecnologias fundamentais para cargas de trabalho de computação heterogêneas e arquiteturas de data center hoje e amanhã”, disse Zane Ball, VP corporativo e gerente geral de engenharia e arquitetura de data center da Intel. “A Intel está colaborando com líderes de ecossistemas como a Astera Labs para reduzir significativamente a latência de interconexão PCIe e CXL na próxima plataforma escalável Intel Xeon com o codinome‘ Sapphire Rapids ’e plataformas adicionais.”

Conteúdos Relacionados:

- Retiming USB4 sobre USB-C

- Construindo interconexões de alto desempenho com várias gerações de PCIe

- Xilinx visa o descarregamento do data center com hardware ‘combinável’

- Como a supercomputação de ponta transformará o grande dilúvio de dados

Integrado

- Problemas legais em computação em nuvem e suas soluções

- MÓDULO DE DADOS:soluções de sinalização digital orientadas para o cliente em exposição no ISE

- Microchip:os buffers de clock atendem aos padrões DB2000Q / QL mais especificações PCIe Gen 4 e 5 de baixo jitter

- Apacer:SSDs PCIe NVMe Gen3, a próxima etapa lógica para armazenamento de nível industrial

- Swissbit:soluções de segurança baseadas em hardware para proteger dados e dispositivos

- TECHWAY:Plataforma Kintex-7 FPGA PCIe para impulsionar o desempenho da taxa de dados com 12 links HSS

- Estratégia e soluções do Exército para manutenção baseada em condições

- Os benefícios da adaptação de IIoT e soluções de análise de dados para EHS

- Combate a inundações em áreas urbanas com soluções de rede IoT

- Como a Internet das Coisas está transformando a cadeia de suprimentos:Parte 2, Soluções futuras