Circuito de porta CMOS

Até este ponto, nossa análise de circuitos lógicos de transistor foi limitada ao TTL paradigma de design, em que transistores bipolares são usados, e a estratégia geral de entradas flutuantes sendo equivalente a “alto” (conectado a V cc ) entradas - e, correspondentemente, a permissão de estágios de saída de “coletor aberto” - é mantida. Essa, no entanto, não é a única maneira de construir portas lógicas.

Transistores de efeito de campo

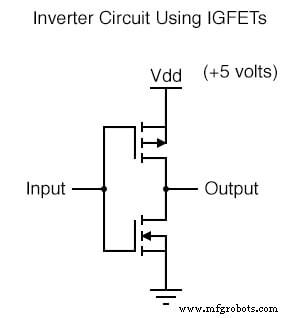

Transistores de efeito de campo, particularmente a variedade de porta isolada, podem ser usados no projeto de circuitos de porta. Sendo dispositivos controlados por voltagem em vez de dispositivos controlados por corrente, os IGFETs tendem a permitir projetos de circuito muito simples. Tome, por exemplo, o seguinte circuito do inversor construído usando IGFETs de canal P e N:

Observe o “V dd ”No terminal positivo da fonte de alimentação. Este rótulo segue a mesma convenção que “V cc ”Em circuitos TTL:representa a tensão constante aplicada ao dreno de um transistor de efeito de campo, em referência ao terra.

Transistores de efeito de campo em circuitos de porta

Entrada baixa

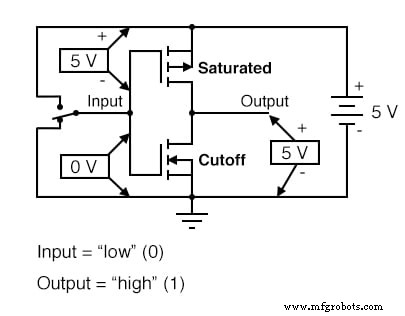

Vamos conectar este circuito de portão a uma fonte de alimentação e interruptor de entrada e examinar sua operação. Observe que esses transistores IGFET são do tipo E (modo de aprimoramento) e, portanto, estão normalmente desligados dispositivos.

É necessária uma tensão aplicada entre a porta e o dreno (na verdade, entre a porta e o substrato) da polaridade correta para enviá-los em .

O transistor superior é um IGFET de canal P. Quando o canal (substrato) é tornado mais positivo do que a porta (porta negativa em relação ao substrato), o canal é aumentado e a corrente é permitida entre a fonte e o dreno.

Portanto, na ilustração acima, o transistor superior está ligado. O transistor inferior, com tensão zero entre a porta e o substrato (fonte), está em seu modo normal: desligado .

Assim, a ação desses dois transistores é tal que o terminal de saída do circuito da porta tem uma conexão sólida com V dd e uma conexão de aterramento de altíssima resistência. Isso torna a saída “alta” (1) para o estado “baixo” (0) da entrada.

Alta entrada

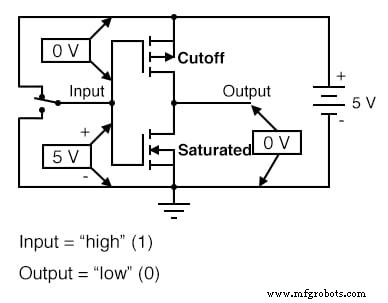

A seguir, moveremos a chave de entrada para a outra posição e veremos o que acontece:

Agora, o transistor inferior (canal N) está saturado porque tem tensão suficiente da polaridade correta aplicada entre a porta e o substrato (canal) para ligá-lo (positivo na porta, negativo no canal). O transistor superior, com tensão zero aplicada entre sua porta e substrato, está em seu modo normal: desligado .

Assim, a saída deste circuito de porta agora é “baixa” (0). Claramente, este circuito exibe o comportamento de um inversor, ou porta NÃO.

Semicondutores de óxido de metal complementar (CMOS)

O uso de transistores de efeito de campo em vez de transistores bipolares simplificou muito o projeto da porta do inversor. Observe que a saída desta porta nunca flutua como é o caso com o circuito TTL mais simples:ela tem uma configuração “totem-pole” natural, capaz de gerar e drenar a corrente de carga.

A chave para o design elegante deste circuito de portão é o complementar uso de IGFETs de canal P e N. Uma vez que os IGFETs são mais comumente conhecidos como MOSFETs ( M etal- O xide- S emicondutor F campo E ffeito T ransistor), e este circuito usa transistores de canal P e N juntos, a classificação geral dada a circuitos de porta como este é CMOS : C omplementar M etal O xide S emicondutor.

Portas CMOS:desafios e soluções

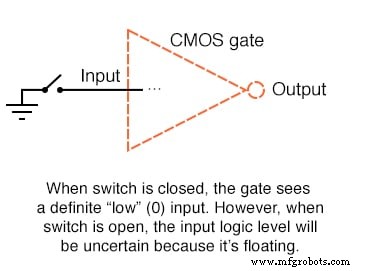

Os circuitos CMOS não são afetados pelas não linearidades inerentes dos transistores de efeito de campo, porque, como circuitos digitais, seus transistores sempre operam no saturado ou corte modos e nunca no ativo modo. Suas entradas são, no entanto, sensíveis a altas tensões geradas por fontes eletrostáticas (eletricidade estática) e podem até ser ativadas em estados "alto" (1) ou "baixo" (0) por fontes de tensão espúrias se deixadas flutuando.

Por esta razão, não é aconselhável permitir que uma entrada de porta lógica CMOS flutue sob quaisquer circunstâncias. Observe que isso é muito diferente do comportamento de uma porta TTL, onde uma entrada flutuante foi interpretada com segurança como um nível lógico “alto” (1).

Problemas de CMOS com entradas flutuantes

Isso pode causar um problema se a entrada para uma porta lógica CMOS for acionada por uma chave de acionamento único, onde um estado tem a entrada solidamente conectada a V dd ou terra e o outro estado tem a entrada flutuante (não conectada a nada):

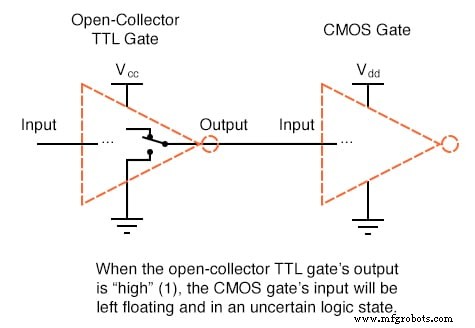

Além disso, este problema surge se uma entrada de porta CMOS está sendo conduzida por um coletor aberto Portão TTL. Porque a saída de tal porta TTL flutua quando vai "alta" (1), a entrada da porta CMOS será deixada em um estado incerto:

Solução para entradas flutuantes

Resistores pullup

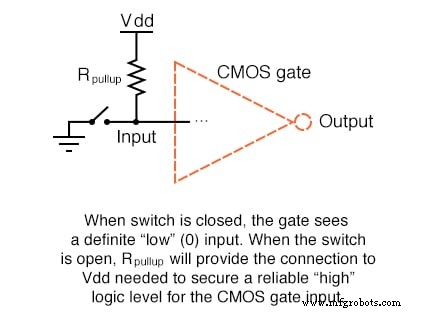

Felizmente, existe uma solução fácil para esse dilema, usada com frequência em circuitos lógicos CMOS. Sempre que um switch de disparo único (ou qualquer outro tipo de saída de portão incapaz de ambos sourcing and sinking current) está sendo usado para conduzir uma entrada CMOS, um resistor conectado a V dd ou o solo pode ser usado para fornecer um nível lógico estável para o estado no qual a saída do dispositivo de acionamento está flutuando.

O valor deste resistor não é crítico:10 kΩ geralmente é suficiente. Quando usado para fornecer um nível lógico "alto" (1) no caso de uma fonte de sinal flutuante, este resistor é conhecido como um resistor pullup :

Resistores Pulldown

Quando tal resistor é usado para fornecer um nível lógico "baixo" (0) no caso de uma fonte de sinal flutuante, ele é conhecido como um resistor suspenso . Novamente, o valor de um resistor suspenso não é crítico:

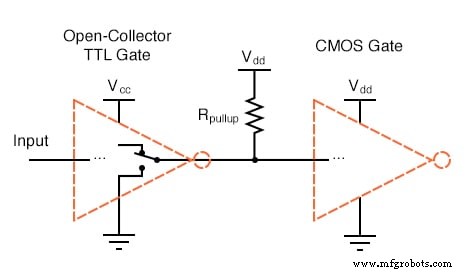

Porque as saídas TTL de coletor aberto sempre afundam, nunca fornecem, corrente, puxam para cima resistores são necessários ao fazer a interface de tal saída para uma entrada de porta CMOS:

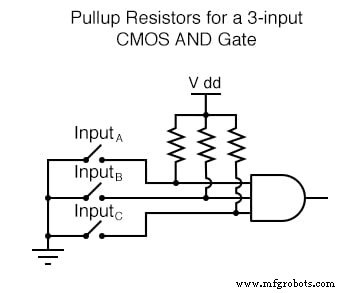

Vários resistores pullup e pulldown

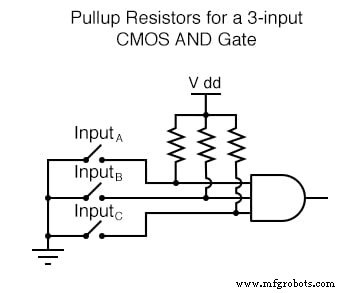

Embora as portas CMOS usadas nos exemplos anteriores fossem todas inversores (entrada única), o mesmo princípio de resistores pullup e pulldown se aplica às portas CMOS de entrada múltipla. Claro, um resistor pullup ou pulldown separado será necessário para cada entrada de porta:

Isso nos leva à próxima questão:como projetamos portas CMOS de entrada múltipla, como AND, NAND, OR e NOR? Não surpreendentemente, a (s) resposta (s) a esta pergunta revelam uma simplicidade de design muito parecida com a do inversor CMOS sobre seu equivalente TTL.

Portas CMOS NAND

Por exemplo, aqui está o diagrama esquemático para uma porta CMOS NAND:

Observe como os transistores Q 1 e Q 3 assemelham-se ao par complementar conectado em série do circuito inversor. Ambos são controlados pelo mesmo sinal de entrada (entrada A), o transistor superior desligando e o transistor inferior ligando quando a entrada está “alta” (1), e vice-versa.

Observe também como os transistores Q 2 e Q 4 são controlados de forma semelhante pelo mesmo sinal de entrada (entrada B) e como eles também exibirão o mesmo comportamento liga / desliga para os mesmos níveis lógicos de entrada. Os transistores superiores de ambos os pares (Q 1 e Q 2 ) têm seus terminais de fonte e dreno em paralelo, enquanto os transistores inferiores (Q 3 e Q 4 ) estão conectados em série.

O que isso significa é que a saída será “alta” (1) se for transistor superior satura e irá para "baixo" (0) somente se ambos os transistores inferiores saturam.

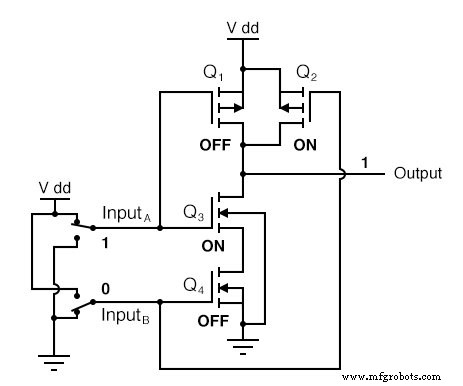

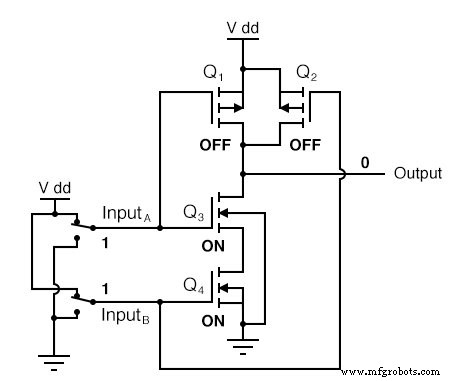

Comportamentos do circuito CMOS para todas as entradas lógicas

A seguinte sequência de ilustrações mostra o comportamento desta porta NAND para todas as quatro possibilidades de níveis lógicos de entrada (00, 01, 10 e 11):

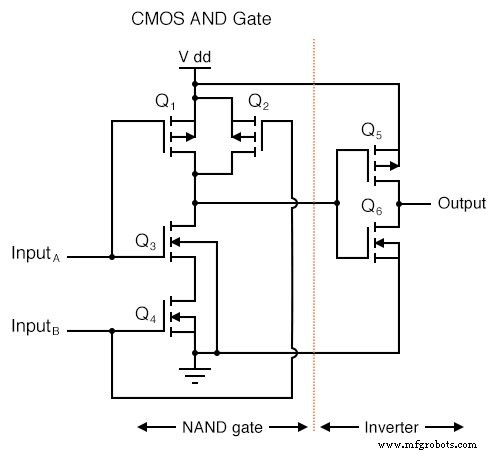

CMOS E portão

Tal como acontece com a porta TTL NAND, o circuito da porta CMOS NAND pode ser usado como o ponto de partida para a criação de uma porta AND. Tudo o que precisa ser adicionado é outro estágio de transistores para inverter o sinal de saída:

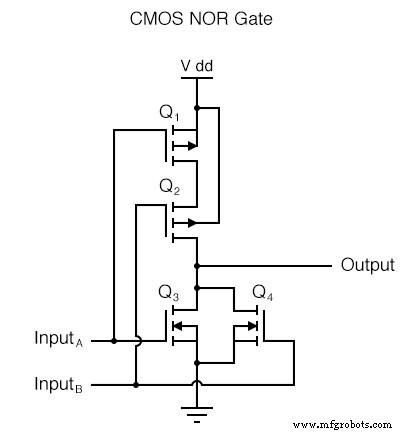

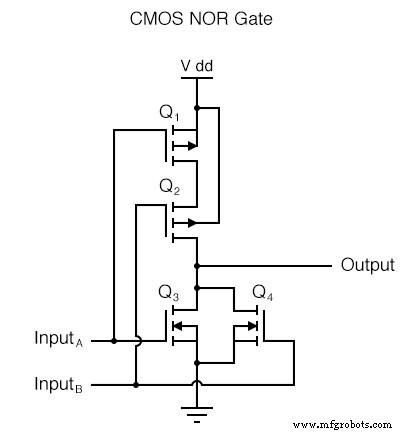

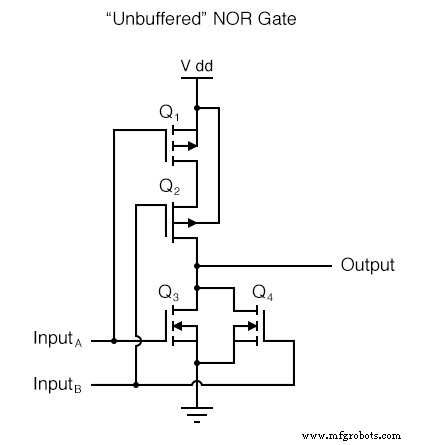

Portas CMOS NOR

Um circuito de porta CMOS NOR usa quatro MOSFETs exatamente como a porta NAND, exceto que seus transistores são arranjados de forma diferente. Em vez de dois sourcing em paralelo transistores (superiores) conectados a V dd e dois afundamento conectados em série transistores (inferiores) conectados ao aterramento, a porta NOR usa dois transistores sourcing conectados em série e dois transistores sinking conectados em paralelo como este:

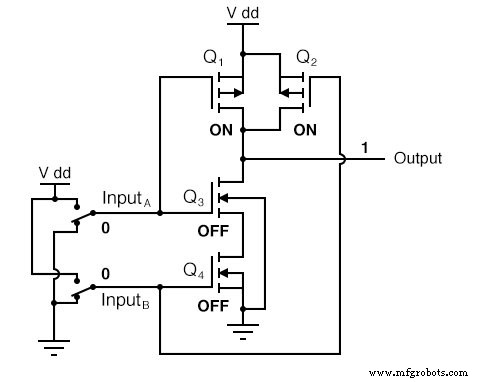

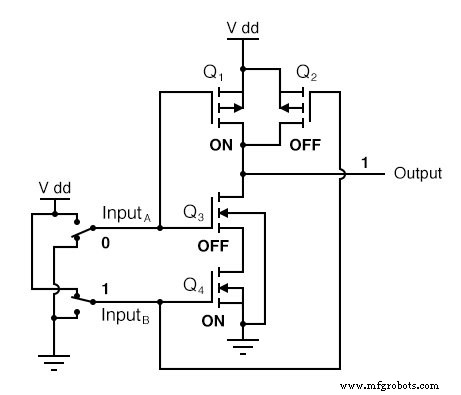

Tal como acontece com a porta NAND, transistores Q 1 e Q 3 funcionam como um par complementar, assim como os transistores Q 2 e Q 4 . Cada par é controlado por um único sinal de entrada. Se qualquer um insira A ou entrada B são “altas” (1), pelo menos um dos transistores inferiores (Q 3 ou Q 4 ) ficará saturado, tornando a saída “baixa” (0).

Apenas no caso de ambos sendo as entradas “baixas” (0), ambos os transistores inferiores estarão no modo de corte e ambos os transistores superiores estarão saturados, as condições necessárias para a saída ir “alta” (1). Esse comportamento, é claro, define a função lógica do NOR.

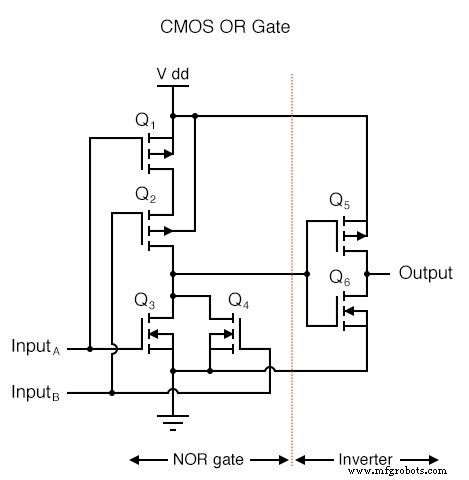

CMOS OU Gates

A função OR pode ser construída a partir da porta NOR básica com a adição de um estágio de inversor na saída:

TTL vs. CMOS:vantagens e desvantagens

Visto que parece que qualquer porta possível de construir usando a tecnologia TTL pode ser duplicada no CMOS, por que essas duas “famílias” de projeto lógico ainda coexistem? A resposta é que TTL e CMOS têm suas próprias vantagens exclusivas.

Em primeiro lugar na lista de comparações entre TTL e CMOS está a questão do consumo de energia. Nesta medida de desempenho, o CMOS é o vencedor incontestável. Como os pares MOSFET dos canais P e N complementares de um circuito de porta CMOS (idealmente) nunca conduzem ao mesmo tempo, há pouca ou nenhuma corrente puxada pelo circuito do V dd fonte de alimentação, exceto para a corrente necessária para fornecer corrente para uma carga. O TTL, por outro lado, não pode funcionar sem alguma corrente consumida o tempo todo, devido aos requisitos de polarização dos transistores bipolares dos quais é feito.

No entanto, há uma advertência para essa vantagem. Enquanto a dissipação de potência de uma porta TTL permanece bastante constante, independentemente de seu (s) estado (ões) operacional (is), uma porta CMOS dissipa mais potência conforme a frequência de seu (s) sinal (es) de entrada aumenta. Se uma porta CMOS é operada em uma condição estática (inalterada), ela dissipa energia zero (idealmente).

No entanto, os circuitos de porta CMOS consomem corrente transitória durante cada mudança de estado de saída de "baixo" para "alto" e vice-versa. Portanto, quanto mais frequentemente uma porta CMOS alterna entre os modos, mais frequentemente ela extrairá corrente do V dd fornecimento, portanto, maior dissipação de energia em frequências maiores.

Vantagens do CMOS

Uma porta CMOS também puxa muito menos corrente de uma saída de porta de condução do que uma porta TTL porque os MOSFETs são dispositivos controlados por tensão, não por corrente. Isso significa que uma porta pode acionar muito mais entradas CMOS do que entradas TTL. A medida de quantas entradas de porta uma única saída de porta pode conduzir é chamada de fanout .

Outra vantagem que os designs de porta CMOS desfrutam em relação ao TTL é uma faixa permitida muito mais ampla de tensões de fonte de alimentação. Considerando que as portas TTL são restritas à fonte de alimentação (V cc ) tensões entre 4,75 e 5,25 volts, as portas CMOS são normalmente capazes de operar em qualquer tensão entre 3 e 15 volts!

A razão por trás dessa disparidade nas tensões da fonte de alimentação são os respectivos requisitos de polarização do MOSFET versus os transistores de junção bipolar. Os MOSFETs são controlados exclusivamente pela tensão da porta (em relação ao substrato), enquanto os BJTs são controlados por corrente dispositivos.

As resistências do circuito da porta TTL são calculadas com precisão para correntes de polarização adequadas, assumindo uma fonte de alimentação regulada de 5 volts. Quaisquer variações significativas na tensão da fonte de alimentação resultarão em correntes de polarização do transistor incorretas, resultando em operação não confiável (imprevisível).

O único efeito que as variações na tensão da fonte de alimentação têm em uma porta CMOS é a definição de tensão de um estado “alto” (1). Para uma porta CMOS operando a 15 volts de tensão de alimentação (V dd ), um sinal de entrada deve ser próximo a 15 volts para ser considerado “alto” (1). O limite de tensão para um sinal “baixo” (0) permanece o mesmo:próximo a 0 volts.

Desvantagens do CMOS

Uma desvantagem decidida do CMOS é a velocidade lenta, em comparação com o TTL. As capacitâncias de entrada de uma porta CMOS são muito, muito maiores do que a de uma porta TTL comparável - devido ao uso de MOSFETs em vez de BJTs - e, portanto, uma porta CMOS será mais lenta para responder a uma transição de sinal (baixo para alto ou vice-versa) do que uma porta TTL, todos os outros fatores sendo iguais.

A constante de tempo RC formada pelas resistências do circuito e a capacitância de entrada da porta tende a impedir os tempos de subida e descida rápidos de um nível lógico digital, degradando assim o desempenho de alta frequência.

Estratégias para combater as desvantagens

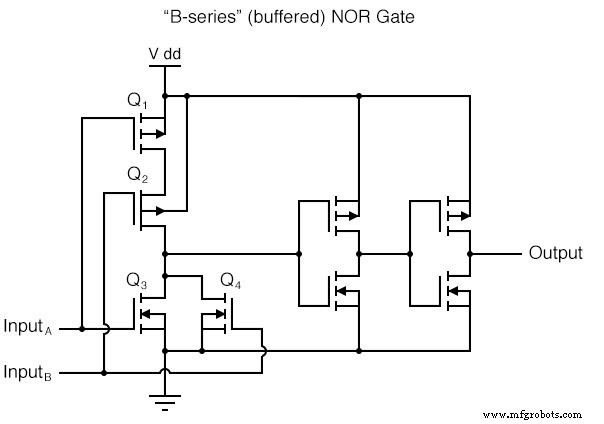

Uma estratégia para minimizar esta desvantagem inerente do circuito de porta CMOS é "buffer" o sinal de saída com estágios de transistor adicionais, para aumentar o ganho de tensão geral do dispositivo. Isso fornece uma tensão de saída de transição mais rápida (alta para baixa ou baixa para alta) para uma tensão de entrada que muda lentamente de um estado lógico para outro.

Considere este exemplo de uma porta NOR “sem buffer” versus uma porta “armazenada em buffer” ou série B , Porta NOR:

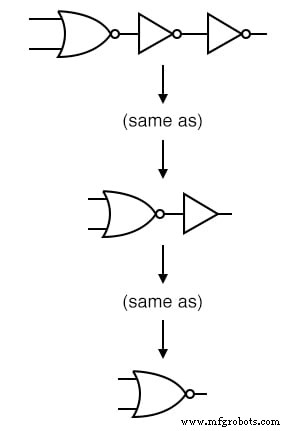

Em essência, o aprimoramento do design da série B adiciona dois inversores à saída de um circuito NOR simples. Isso não serve para nada no que diz respeito à lógica digital, uma vez que dois inversores em cascata simplesmente cancelam:

No entanto, adicionar esses estágios do inversor ao circuito serve ao propósito de aumentar o ganho geral de tensão, tornando a saída mais sensível às mudanças no estado de entrada, trabalhando para superar a lentidão inerente causada pela capacitância de entrada da porta CMOS.

REVER:

- As portas lógicas CMOS são feitas de transistores IGFET (MOSFET) em vez de transistores de junção bipolar.

- As entradas de porta CMOS são sensíveis à eletricidade estática. Eles podem ser danificados por altas tensões e podem assumir qualquer nível lógico se deixados flutuando.

- Pullup e suspenso resistores são usados para evitar que uma entrada de porta CMOS flutue se estiver sendo conduzida por uma fonte de sinal capaz apenas de gerar ou drenar corrente.

- As portas CMOS dissipam muito menos energia do que as portas TTL equivalentes, mas sua dissipação de energia aumenta com a frequência do sinal, enquanto a dissipação de energia de uma porta TTL é aproximadamente constante em uma ampla gama de condições operacionais.

- As entradas de porta CMOS consomem muito menos corrente do que as entradas TTL, porque os MOSFETs são dispositivos controlados por tensão, não por corrente.

- As portas CMOS são capazes de operar em uma gama muito mais ampla de tensões de fonte de alimentação do que TTL:normalmente 3 a 15 volts contra 4,75 a 5,25 volts para TTL.

- As portas CMOS tendem a ter uma frequência operacional máxima muito mais baixa do que as portas TTL devido às capacitâncias de entrada causadas pelas portas MOSFET.

- série B As portas CMOS têm saídas “armazenadas em buffer” para aumentar o ganho de tensão da entrada para a saída, resultando em uma resposta de saída mais rápida às mudanças do sinal de entrada. Isso ajuda a superar a lentidão inerente das portas CMOS devido à capacitância de entrada do MOSFET e à constante de tempo RC assim gerada.

PLANILHAS RELACIONADAS:

-

Planilha de transistores de efeito de campo de porta isolada

-

Planilha CMOS Logic Gates

Tecnologia industrial

- Como construir um circuito de espelho atual

- Função de Gate Básica

- Porta NOR Trava S-R

- Transistores, Bipolar

- Transistores, efeito de campo de junção (JFET)

- Transistores, efeito de campo de porta isolada (IGFET ou MOSFET)

- Transistores, híbridos

- Circuitos integrados

- Introdução aos transistores de efeito de campo de porta isolada

- Modelagem de nível de portão