Contadores assíncronos

Na seção anterior, vimos um circuito usando um flip-flop J-K que contava regressivamente em uma sequência binária de dois bits, de 11 a 10 a 01 a 00.

Uma vez que seria desejável ter um circuito que pudesse contar para a frente e não apenas para trás, valeria a pena examinar uma sequência de contagem progressiva novamente e procurar mais padrões que possam indicar como construir tal circuito.

Como sabemos que as sequências de contagem binária seguem um padrão de divisão de frequência de oitava (fator de 2), e que os multivibradores flip-flop JK configurados para o modo "toggle" são capazes de realizar este tipo de divisão de frequência, podemos imaginar um circuito composto de vários flip-flops JK, em cascata para produzir quatro bits de saída.

O principal problema que enfrentamos é determinar como para conectar esses flip-flops juntos para que eles alternem nos momentos certos para produzir a sequência binária adequada.

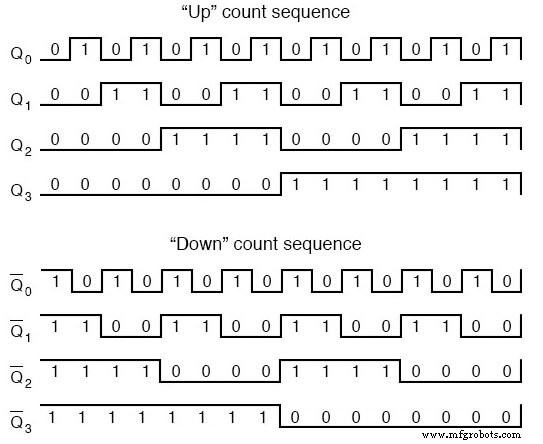

Examine a seguinte sequência de contagem binária, prestando atenção aos padrões que precedem a "alternância" de um bit entre 0 e 1:

Observe que cada bit nesta sequência de quatro bits alterna quando o bit anterior (o bit com menor significado ou peso de posição) alterna em uma direção específica:de 1 a 0.

As setas pequenas indicam aqueles pontos na sequência onde um bit alterna, a ponta da seta apontando para o bit anterior em transição de um estado "alto" (1) para um estado "baixo" (0):

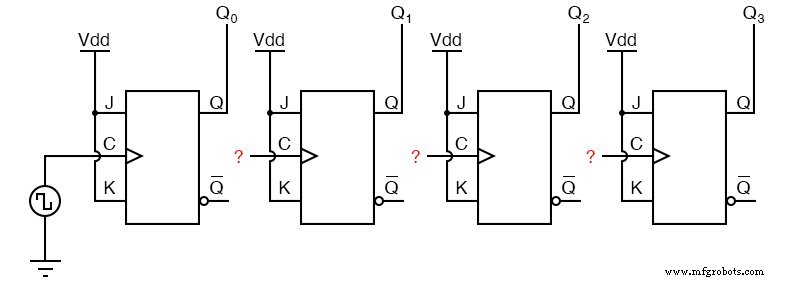

Começando com quatro flip-flops JK conectados de forma a estarem sempre no modo "toggle", precisamos determinar como conectar as entradas de clock de forma que cada bit sucessivo alterne quando o bit anterior fizer a transição de 1 a 0.

As saídas Q de cada flip-flop servirão como os respectivos bits binários da contagem final de quatro bits:

Se usássemos flip-flops com disparo de borda negativa (símbolos de bolha nas entradas de clock), poderíamos simplesmente conectar a entrada de clock de cada flip-flop à saída Q do flip-flop anterior a ele, de modo que quando o bit anterior muda de 1 para 0, a "borda descendente" desse sinal "cronometraria" o próximo flip-flop para alternar o próximo bit:

Contador “Up” de quatro bits

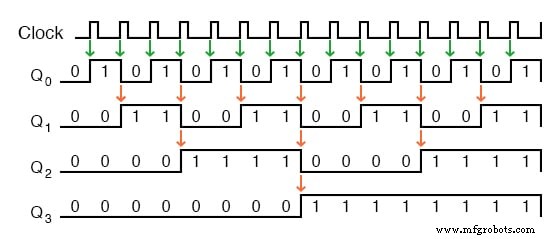

Este circuito produziria as seguintes formas de onda de saída, quando "sincronizado" por uma fonte repetitiva de pulsos de um oscilador:

O primeiro flip-flop (aquele com Q 0 saída), tem uma entrada de clock acionada por borda positiva, de modo que alterna com cada borda de subida do sinal de clock.

Observe como o sinal de clock neste exemplo tem um ciclo de trabalho inferior a 50%.

Eu mostrei o sinal desta maneira com o propósito de demonstrar como o sinal do relógio não precisa ser simétrico para obter bits de saída "limpos" confiáveis em nossa sequência binária de quatro bits.

No primeiro circuito flip-flop mostrado neste capítulo, usei o próprio sinal de clock como um dos bits de saída.

Esta é uma prática ruim no projeto do contador, porque requer o uso de um sinal de onda quadrada com um ciclo de trabalho de 50% (tempo "alto" =tempo "baixo") a fim de obter uma sequência de contagem onde cada etapa faz uma pausa pelo mesmo período de tempo.

Usar um flip-flop J-K para cada bit de saída, entretanto, nos livra da necessidade de ter um sinal de clock simétrico, permitindo o uso de praticamente qualquer variedade de forma de onda alta / baixa para incrementar a sequência de contagem.

Conforme indicado por todas as outras setas no diagrama de pulso, cada bit de saída sucessivo é alternado pela ação do bit anterior em transição de "alto" (1) para "baixo" (0).

Este é o padrão necessário para gerar uma sequência de contagem crescente.

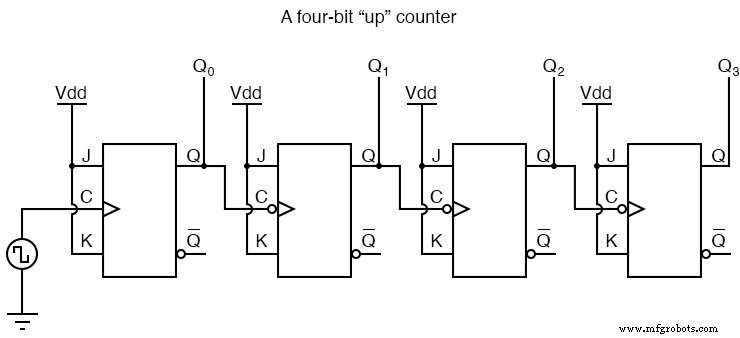

Uma solução menos óbvia para gerar uma sequência "para cima" usando flip-flops acionados por borda positiva é "cronometrar" cada flip-flop usando a saída Q 'do flip-flop anterior em vez da saída Q.

Uma vez que a saída Q 'será sempre o estado oposto exato da saída Q em um flip-flop JK (nenhum estado inválido com este tipo de flip-flop), uma transição de alto para baixo na saída de Q será acompanhada por uma transição de baixo para alto na saída Q '.

Em outras palavras, cada vez que a saída Q de um flip-flop muda de 1 para 0, a saída Q 'do mesmo flip-flop mudará de 0 para 1, fornecendo o pulso de clock positivo que precisaríamos alternar um flip-flop acionado por borda positiva no momento certo:

Contador “Up” alternativo de quatro bits

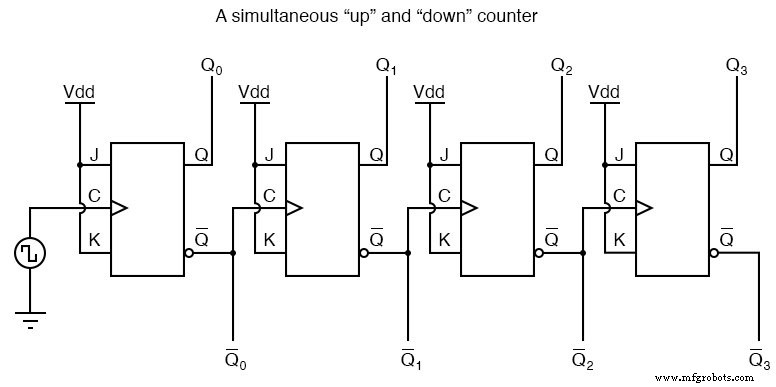

Uma maneira de expandir as capacidades de qualquer um desses dois contra-circuitos é considerar as saídas Q 'como outro conjunto de quatro bits binários.

Se examinarmos o diagrama de pulso de tal circuito, vemos que as saídas Q 'geram um baixo sequência de contagem, enquanto as saídas Q geram um up - sequência de contagem:

Contador “Up” e “Down” simultâneos

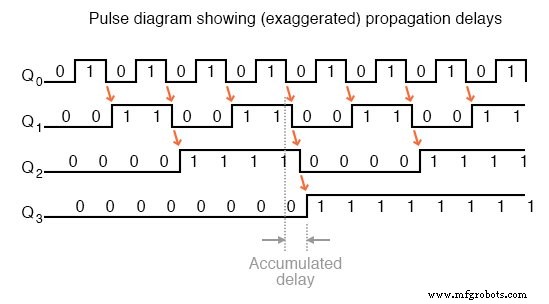

Infelizmente, todos os contra-circuitos mostrados até agora compartilham um problema comum:a ondulação efeito.

Este efeito é visto em certos tipos de adicionador binário e circuitos de conversão de dados, e é devido a atrasos de propagação acumulativos entre portas em cascata.

Quando a saída Q de um flip-flop muda de 1 para 0, ele comanda o próximo flip-flop para alternar.

Se a próxima alternância do flip-flop for uma transição de 1 para 0, ele comandará o flip-flop seguinte para alternar também, e assim por diante.

No entanto, uma vez que sempre há uma pequena quantidade de atraso de propagação entre o comando para alternar (o pulso do clock) e a resposta de alternância real (estados de mudança das saídas Q e Q '), quaisquer flip-flops subsequentes a serem alternados irão alternar algum tempo depois o primeiro flip-flop foi alternado.

Assim, quando vários bits alternam em uma sequência de contagem binária, eles não alternam exatamente ao mesmo tempo:

Desvantagem do circuito de contador assíncrono:atraso de propagação

Como você pode ver, quanto mais bits alternam com um determinado pulso de clock, mais severo é o tempo de atraso acumulado de LSB para MSB.

Quando um pulso de clock ocorre em tal ponto de transição (digamos, na transição de 0111 para 1000), os bits de saída irão "ondular" em sequência de LSB para MSB, conforme cada bit sucessivo alterna e comanda o próximo bit para alternar também , com uma pequena quantidade de atraso de propagação entre cada alternância de bit.

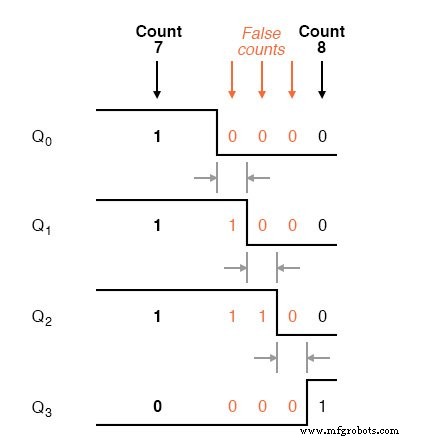

Se olharmos de perto este efeito durante a transição de 0111 para 1000, podemos ver que haverá falso contagens de saída geradas no breve período de tempo em que ocorre o efeito de "ondulação":

Em vez de uma transição limpa de uma saída "0111" para uma saída "1000", o circuito do contador irá ondular muito rapidamente de 0111 a 0110 a 0100 a 0000 a 1000, ou de 7 a 6 a 4 a 0 e depois para 8. Este comportamento dá ao circuito do contador o nome de contador de ondulação ou contador assíncrono .

Circuito do contador de sinal estroboscópico

Em muitas aplicações, esse efeito é tolerável, uma vez que a ondulação acontece muito, muito rapidamente (a largura dos atrasos foi exagerada aqui para auxiliar no entendimento dos efeitos).

Se tudo o que quiséssemos fazer fosse acionar um conjunto de diodos emissores de luz (LEDs) com as saídas do contador, por exemplo, esta breve ondulação não teria nenhuma consequência.

No entanto, se quiséssemos usar este contador para acionar as entradas "selecionadas" de um multiplexador, indexar um ponteiro de memória em um circuito de microprocessador (computador) ou realizar alguma outra tarefa onde saídas falsas pudessem causar erros espúrios, não seria aceitável .

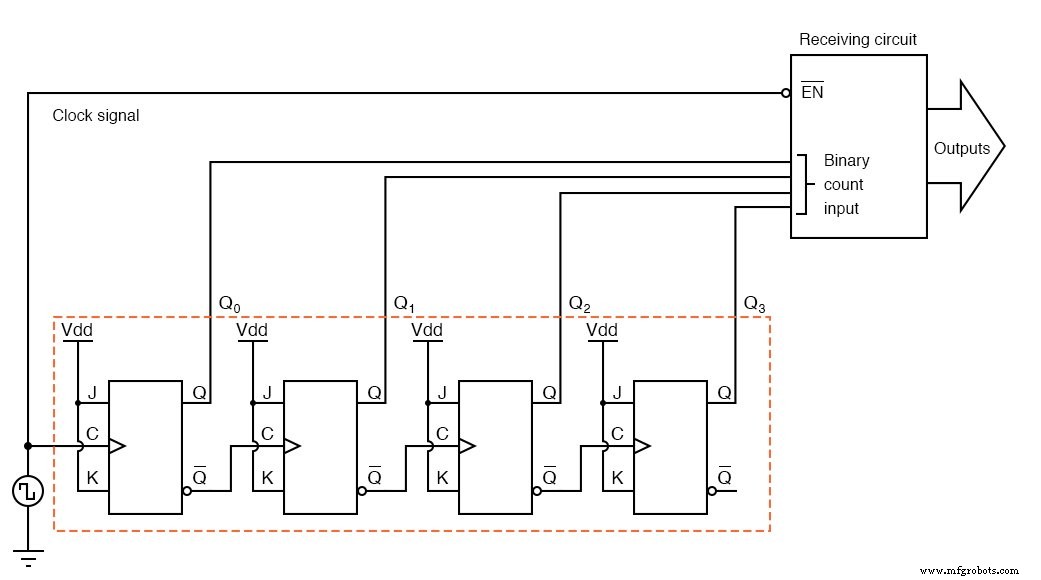

Existe uma maneira de usar este tipo de circuito de contador em aplicativos sensíveis a saídas falsas geradas por ondulação, e envolve um princípio conhecido como strobing .

A maioria dos circuitos decodificadores e multiplexadores são equipados com pelo menos uma entrada chamada "habilitar".

A (s) saída (s) de tal circuito estarão ativas somente quando a entrada de habilitação for ativada.

Podemos usar esta entrada de habilitação para strobe o circuito recebendo a saída do contador de ondulação de modo que seja desabilitado (e, portanto, não respondendo à saída do contador) durante o breve período de tempo em que as saídas do contador podem estar ondulando, e habilitado apenas quando tempo suficiente tiver passado desde o último pulso de clock que todas as ondulações terão cessado.

Na maioria dos casos, o sinal estroboscópico pode ser o mesmo pulso de clock que aciona o circuito do contador:

Com uma entrada de habilitação ativo-baixo, o circuito de recepção responderá à contagem binária do circuito contador de quatro bits apenas quando o sinal do relógio estiver "baixo".

Assim que o pulso do clock fica "alto", o circuito receptor para de responder à saída do circuito do contador.

Uma vez que o circuito do contador é acionado por borda positiva (conforme determinado pelo primeiro entrada de relógio flip-flop), toda a ação de contagem ocorre na transição de baixo para alto do sinal de relógio, o que significa que o circuito de recepção será desabilitado antes que qualquer alternância ocorra nos quatro bits de saída do circuito do contador.

O circuito de recepção não será habilitado até que o sinal do relógio retorne a um estado baixo, o que deve ser um tempo longo o suficiente depois toda ondulação deixou de ser “segura” para permitir que a nova contagem tenha efeito no circuito receptor.

O parâmetro crucial aqui é o tempo "alto" do sinal do relógio:deve ser pelo menos tão longo quanto o período de ondulação máximo esperado do circuito do contador.

Do contrário, o sinal do relógio habilitará prematuramente o circuito de recepção, enquanto alguma ondulação ainda está ocorrendo.

Desvantagem do circuito do contador assíncrono:velocidade limitada

Outra desvantagem do contra-circuito assíncrono, ou ondulação, é a velocidade limitada.

Embora todos os circuitos de porta sejam limitados em termos de frequência máxima de sinal, o projeto de contra-circuitos assíncronos agrava esse problema, tornando os atrasos de propagação aditivos.

Assim, mesmo se o estroboscópio for usado no circuito receptor, um circuito contador assíncrono não pode ser cronometrado em qualquer frequência mais alta do que aquela que permite que o maior retardo de propagação acumulado possível decorra bem antes do próximo pulso.

A solução para esse problema é um contra-circuito que evita a ondulação por completo.

Esse circuito de contador eliminaria a necessidade de projetar um recurso de "estroboscópio" em quaisquer circuitos digitais que usem a saída do contador como uma entrada e também desfrutaria de uma velocidade operacional muito maior do que seu equivalente assíncrono.

Este projeto de circuito do contador é o assunto da próxima seção.

REVER:

- Um contador "para cima" pode ser feito conectando as entradas de relógio dos flip-flops J-K acionados por borda positiva às saídas Q 'dos flip-flops anteriores. Outra maneira é usar flip-flops disparados por borda negativa, conectando as entradas de clock às saídas Q dos flip-flops anteriores. Em ambos os casos, as entradas J e K de todos os flip-flops são conectadas a V cc ou V dd para estar sempre “alto”.

- Circuitos de contador feitos de flip-flops J-K em cascata, onde cada entrada de relógio recebe seus pulsos da saída do flip-flop anterior invariavelmente exibe um efeito cascata , onde falsas contagens de saída são geradas entre algumas etapas da sequência de contagem. Esses tipos de contra-circuitos são chamados de contadores assíncronos , ou contadores de ondulação .

- Estroboscópico é uma técnica aplicada a circuitos que recebem a saída de um contador assíncrono (ondulação), de forma que as contagens falsas geradas durante o tempo de ondulação não tenham nenhum efeito prejudicial. Basicamente, o habilitar A entrada de tal circuito é conectada ao pulso do relógio do contador de tal forma que é habilitada apenas quando as saídas do contador não estão mudando, e será desabilitada durante os períodos de mudanças nas saídas do contador onde ocorre ondulação.

PLANILHAS RELACIONADAS:

- Planilha do contador ondulado

Tecnologia industrial