Registradores de deslocamento universal:entrada paralela, saída paralela

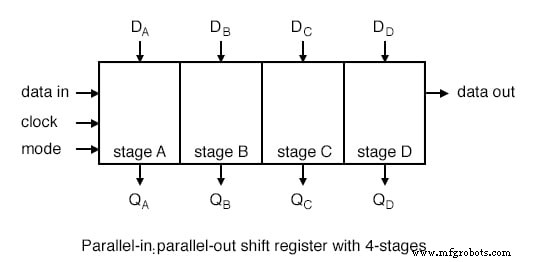

O objetivo do registro de deslocamento de entrada / saída paralela é pegar dados paralelos, deslocá-los e, em seguida, gerá-los como mostrado abaixo.

Um registrador de deslocamento universal é um dispositivo que faz tudo, além da função de entrada / saída paralela.

Acima, aplicamos quatro bits de dados a um registrador de deslocamento de entrada / saída paralela em D A D B D C D D . O controle de modo, que pode ser várias entradas, controla o carregamento paralelo versus deslocamento.

O controle de modo também pode controlar a direção da mudança em alguns dispositivos reais. Os dados serão deslocados uma posição de bit para cada pulso de clock.

Os dados deslocados estão disponíveis nas saídas Q A Q B Q C Q D . Os “dados de entrada” e “dados de saída” são fornecidos para cascateamento de vários estágios.

Porém, acima, podemos apenas cascatear dados para deslocamento para a direita. Poderíamos acomodar a cascata de dados de deslocamento para a esquerda adicionando um par de sinais apontando para a esquerda, “entrada de dados” e “saída de dados”, acima.

Os detalhes internos de um registro de deslocamento paralelo de entrada / saída paralelo com deslocamento para a direita são mostrados abaixo.

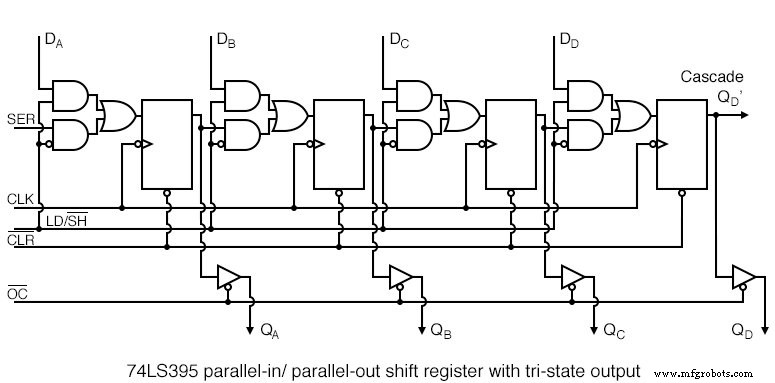

Os buffers de três estados não são estritamente necessários para o registro de deslocamento de entrada / saída paralela, mas fazem parte do dispositivo do mundo real mostrado abaixo.

O 74LS395 se assemelha tanto ao nosso conceito de um hipotético registro de deslocamento paralelo para dentro / fora do deslocamento para a direita que usamos uma versão excessivamente simplificada dos detalhes da planilha de dados acima.

Veja o link para a folha de dados completa para mais detalhes, mais adiante neste capítulo.

LD / SH ’ controla o multiplexador AND-OR na entrada de dados para os FFs. Se LD / SH ’=1 , as quatro portas AND superiores são habilitadas, permitindo a aplicação de entradas paralelas D A D B D C D D às quatro entradas de dados FF.

Observe a bolha do inversor na entrada do clock dos quatro FFs. Isso indica que o 74LS395 clica os dados no relógio negativo, que é a transição de alto para baixo.

Os quatro bits de dados serão sincronizados em paralelo de D A D B D C D D para Q A Q B Q C Q D no próximo relógio negativo. Nesta "parte real", OC ’ deve ser baixo se os dados precisarem estar disponíveis nos pinos de saída reais, em oposição a apenas nos FFs internos.

Os dados carregados anteriormente podem ser deslocados para a direita em uma posição de bit se LD / SH ’=0 para as bordas negativas sucessivas do relógio.

Quatro relógios deslocariam os dados inteiramente para fora de nosso registrador de deslocamento de 4 bits. Os dados seriam perdidos a menos que nosso dispositivo fosse conectado em cascata a partir de Q D ’ para SER de outro dispositivo.

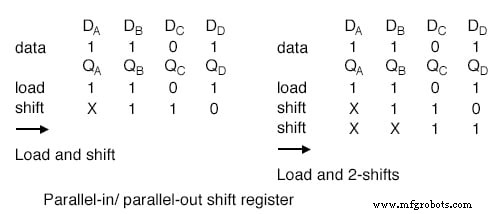

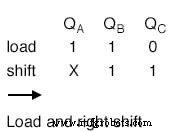

Acima, um padrão de dados é apresentado às entradas D A D B D C D D . O padrão é carregado em Q A Q B Q C Q D . Em seguida, ele é deslocado um pouco para a direita.

Os dados recebidos são indicados por X , o que significa que não sabemos o que é. Se a entrada ( SER ) foram aterrados, por exemplo, saberíamos quais dados ( 0 ) foi deslocado para dentro.

Também mostrado, está mudando para a direita em duas posições, exigindo dois relógios.

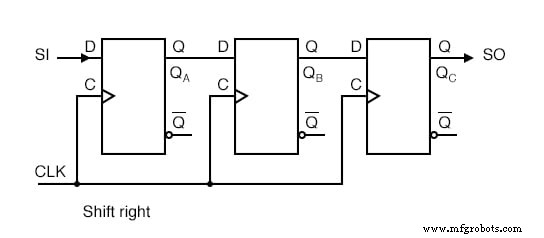

A figura acima serve como referência para o hardware envolvido no deslocamento para a direita dos dados.

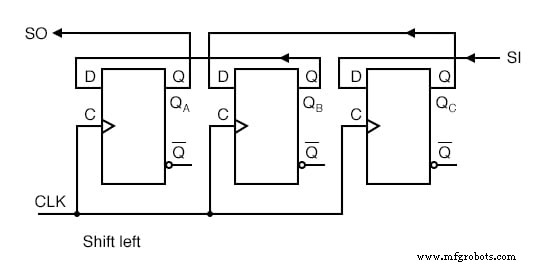

É muito simples até mesmo se preocupar com esta figura, exceto para comparação com figuras mais complexas a seguir.

O deslocamento para a direita de dados é fornecido acima para referência ao deslocador para a direita anterior.

Se precisarmos deslocar para a esquerda, os FFs precisam ser reconectados. Compare com o shifter direito anterior. Além disso, SI e ASSIM foram revertidos. SI muda para Q C . Q C muda para Q B . Q B muda para Q A . Q A sai no SO conexão, onde poderia cascatear para outro shifter SI . Esta sequência de deslocamento para a esquerda está ao contrário da sequência de deslocamento para a direita.

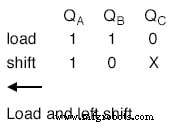

Acima, mudamos o mesmo padrão de dados para a esquerda em um bit.

Há um problema com a figura “deslocar para a esquerda” acima. Não há mercado para isso. Ninguém fabrica uma peça com deslocamento para a esquerda.

Um “dispositivo real” que muda uma direção pode ser conectado externamente para mudar a outra direção. Ou, deveríamos dizer que não há esquerda ou direita no contexto de um dispositivo que se desloca em apenas uma direção.

No entanto, existe um mercado para um dispositivo que se deslocará para a esquerda ou direita sob o comando de uma linha de controle. Claro, esquerda e direita são válidos nesse contexto.

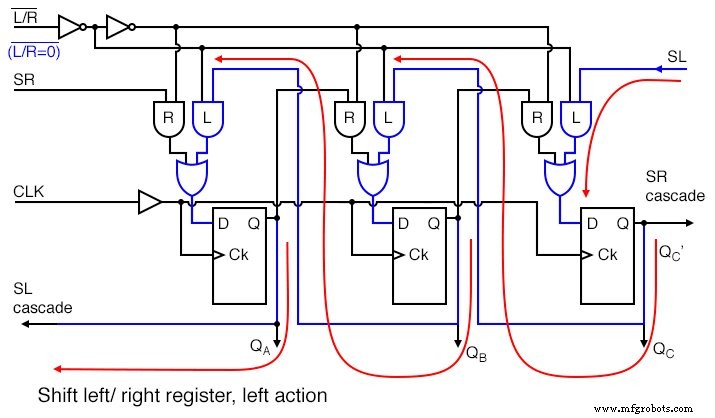

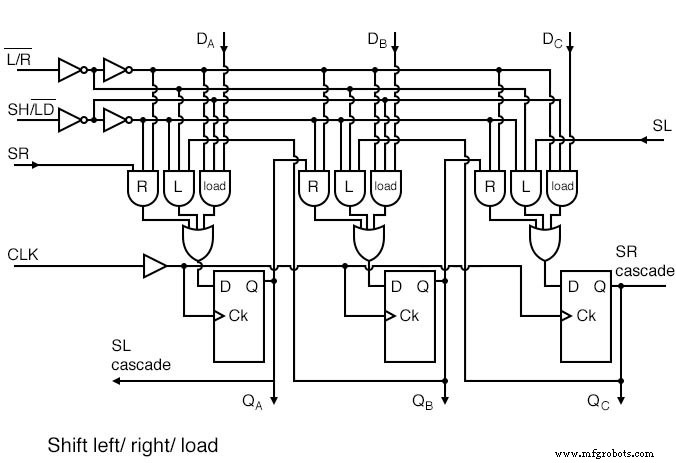

O que temos acima é um registrador de deslocamento hipotético capaz de mudar qualquer direção sob o controle de L ’/ R .

É configurado com L ’/ R =1 para mudar a direção normal, certo. L ’/ R =1 ativa o multiplexador E as portas rotuladas R .

Isso permite que os dados sigam o caminho ilustrado pelas setas, quando um relógio é aplicado. O caminho de conexão é o mesmo da figura "muito simples" “deslocar para a direita” acima.

Os dados mudam em SR , para Q A , para Q B , para Q C , de onde sai na cascata SR . Este pino pode conduzir SR de outro dispositivo à direita.

E se mudarmos L ’/ R para L ’/ R =0 ?

Com L ’/ R =0 , o multiplexador E as portas rotuladas L são ativados, produzindo um caminho, mostrado pelas setas, o mesmo que a figura acima “deslocar para a esquerda”.

Dados mudam em SL , para Q C , para Q B , para Q A , de onde sai em cascata SL . Este pino pode conduzir SL de outro dispositivo à esquerda.

A principal virtude das duas figuras acima que ilustram o “registro de deslocamento para a esquerda / direita” é a simplicidade.

A operação do controle esquerdo direito L ’/ R =0 é fácil de seguir. Uma parte comercial precisa do carregamento de dados paralelo implícito no título da seção. Isso aparece na figura abaixo.

Agora que podemos deslocar tanto para a esquerda quanto para a direita via L ’/ R , vamos adicionar SH / LD ’ , shift / load e as portas AND rotuladas como “load” para fornecer carregamento paralelo de dados das entradas D A D B D C .

Quando SH / LD ’=0 , E portas R e L estão desabilitados, AND gates “load” estão habilitados para passar dados D A D B D C às entradas de dados FF. o próximo relógio CLK irá cronometrar os dados para Q A Q B Q C .

Enquanto os mesmos dados estiverem presentes, eles serão recarregados nos relógios seguintes. No entanto, os dados presentes para apenas um relógio serão perdidos das saídas quando não estiverem mais presentes nas entradas de dados.

Uma solução é carregar os dados em um relógio e, em seguida, passar para os próximos quatro relógios. Este problema é corrigido no 74ALS299 pela adição de outra porta AND ao multiplexador.

Se SH / LD ’ é alterado para SH / LD ’=1 , as portas AND rotuladas como "carga" são desativadas, permitindo o controle esquerdo / direito L ’/ R para definir a direção da mudança no L ou R E portas. O deslocamento é como nas figuras anteriores.

A única coisa necessária para produzir um dispositivo integrado viável é adicionar a quarta porta AND ao multiplexador como aludido para o 74ALS299.

Isso é mostrado na próxima seção dessa parte.

Dispositivos de entrada / saída paralela e universais

Vamos dar uma olhada mais de perto nos registradores de deslocamento de entrada / saída paralela disponíveis como circuitos integrados, cortesia da Texas Instruments.

Para folhas de dados completas do dispositivo, siga os links.

-

SN74LS395A registro de deslocamento de 4 bits de entrada / saída paralela

-

SN74ALS299 registro de deslocamento universal de 8 bits com entrada / saída paralela

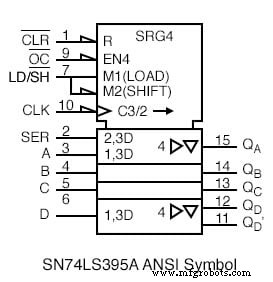

Já vimos os detalhes internos do SN74LS395A, consulte a figura anterior acima, 74LS395 registro de deslocamento de entrada / saída paralela com saída tri-state.

Logo acima está o símbolo ANSI para o 74LS395.

Por que apenas 4 bits, conforme indicado por SRG4 acima? Ter entradas e saídas paralelas, além de pinos de controle e de alimentação, não permite mais bits de E / S (entrada / saída) em um DIP de 16 pinos (Dual Inline Package).

R indica que os estágios de registro de deslocamento são reiniciados pela entrada CLR ’ (meia-seta de inversão baixa ativa na entrada) da seção de controle na parte superior do símbolo. OC ’ , quando baixo, (inverter a seta novamente) habilitará ( EN4 ) os quatro buffers de saída tristate ( Q A Q B Q C Q D ) na seção de dados.

Carregar / deslocar '( LD / SH' ) no pino (7) corresponde aos internos M1 (carregar) e M2 (mudança). Procure os prefixos de 1 e 2 no resto do símbolo para verificar o que é controlado por eles.

O relógio sensível a borda negativa (indicado pela seta invertida no pino 10) C3 / 2 tem duas funções.

Primeiro, o 3 de C3 / 2 afeta qualquer entrada com um prefixo de 3 , diga 2,3D ou 1,3D na seção de dados.

Isso seria uma carga paralela em A, B, C, D atribuído a M1 e C3 para 1,3D . Em segundo lugar, 2 de C3 / 2 -a seta para a direita indica a sincronização de dados em qualquer lugar 2 aparece em um prefixo ( 2,3D no pino 2).

Assim, temos clocking de dados em SER em Q A com modo 2 . A seta para a direita depois de C3 / 2 considera o deslocamento nos estágios internos do registro de deslocamento Q A Q B Q C Q D .

Os triângulos que apontam para a direita indicam buffering; o triângulo invertido indica tri-state, controlado pelo EN4 .

Observe, todos os 4 s no símbolo associado ao EN são freqüentemente omitidos. Estágios Q B Q C são considerados como tendo os mesmos atributos que Q D . Q D ’ cascata para o SER do próximo pacote Para a direita.

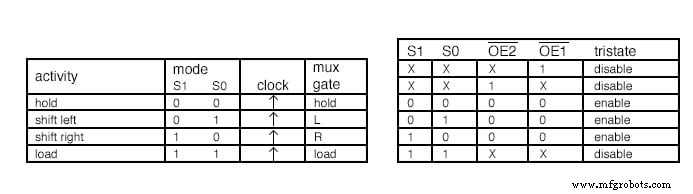

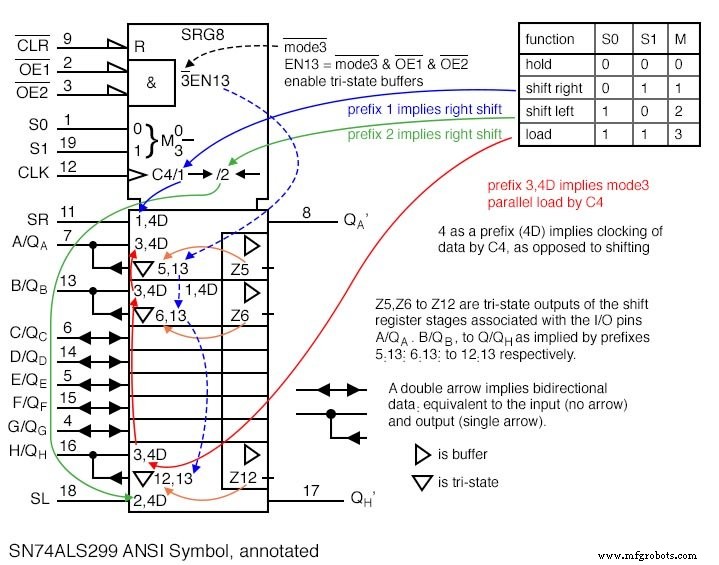

A tabela acima, condensada a partir da folha de dados 299, resume a operação do registro universal de deslocamento / armazenamento 74ALS299.

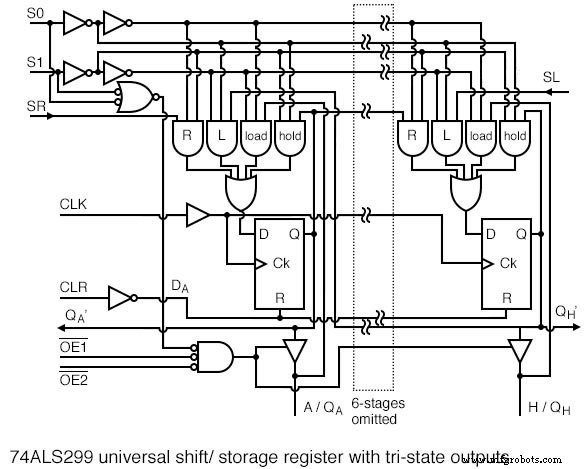

Siga o link ‘299 acima para detalhes completos. As portas do multiplexador R , L , carregar operar como nas figuras anteriores de “registro de deslocamento para a esquerda / direita”.

A diferença é que o modo de entrada S1 e S0 selecione shift left, shift right e carregue com o modo definido para S1 S0 = para 01 , 10 , e 11 respectivamente, conforme mostrado na tabela, habilitando portas de multiplexador L , R , e carregar respectivamente.

Veja a tabela. Uma pequena diferença é o caminho de carga paralelo das saídas tri-state. Na verdade, os buffers tri-state são (devem ser) desabilitados por S1 S0 =11 para flutuar o bus de E / S para uso como entradas.

Um ônibus é uma coleção de sinais semelhantes. As entradas são aplicadas a A , B através de H (mesmos pinos que Q A , Q B , por meio de Q H ) e encaminhado para o carregamento portão nos multiplexadores e no D entradas dos FFs. Os dados são uma carga paralela em um pulso de clock.

A única nova porta do multiplexador é a porta AND rotulada como espera , habilitado por S1 S0 =00 . A espera portão ativa um caminho do Q saída do FF de volta para a espera porta, para a entrada D do mesmo FF. O resultado é que com o modo S1 S0 =00 , a saída é continuamente recarregada com cada novo pulso de clock. Assim, os dados são mantidos. Isso está resumido na tabela.

Para ler dados de saídas Q A , Q B , por meio de Q H , os buffers tri-state devem ser habilitados por OE2 ’, OE1’ =00 e modo = S1 S0 =00, 01 ou 10 .

Ou seja, o modo é qualquer coisa, exceto carregar . Veja a segunda tabela.

Desloca os dados para a direita de um pacote para a esquerda, muda para o SR entrada. Quaisquer dados deslocados para a direita do estágio Q H cascata para a direita via Q H ’.

Essa saída não é afetada pelos buffers tri-state. A sequência de deslocamento para a direita para S1 S0 =10 é:

SR> Q A > Q B > Q C > Q D > Q E > Q F > Q G > Q H (Q H ’)

Os dados de deslocamento à esquerda de um pacote para os deslocamentos à direita no SL entrada. Quaisquer dados deslocados para a esquerda do estágio Q A cascata para a esquerda via Q A ', Também não afetado pelos buffers tri-state. A sequência de deslocamento para a esquerda para S1 S0 =01 é:

(Q A ’) Q A

BCDEFGH (Q SL ’)

A mudança pode ocorrer com os buffers tri-state desativados por um dos OE2 ’ ou OE1 ’=1 . Porém, as saídas de conteúdo do registro não estarão acessíveis. Veja a tabela.

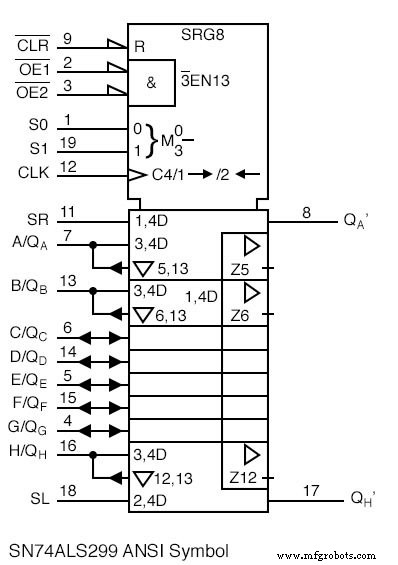

O símbolo ANSI “limpo” para o SN74ALS299 com entrada / saída paralela universal de 8 bits com saída tri-state é mostrado para referência acima.

A versão anotada do símbolo ANSI é mostrada para esclarecer a terminologia nele contida.

Observe que o modo ANSI (S0 S1) é invertido da ordem (S1 S0) usada na tabela anterior.

Isso inverte os números do modo decimal (1 e 2). Em qualquer caso, estamos de acordo com a ficha oficial, copiando esta inconsistência.

Aplicações práticas

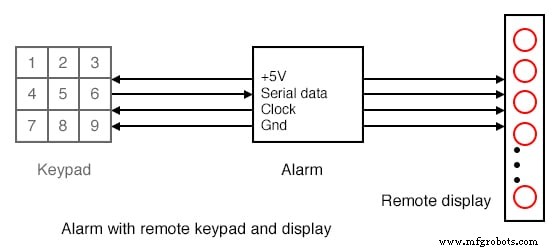

O diagrama de blocos do alarme com teclado remoto é repetido abaixo. Anteriormente, construímos o leitor de teclado e o visor remoto como unidades separadas.

Agora vamos combinar o teclado e o display em uma única unidade usando um registrador de deslocamento universal.

Embora separados no diagrama, o teclado e a tela estão ambos contidos no mesmo gabinete remoto.

Carregaremos em paralelo os dados do teclado no registrador de deslocamento em um único pulso de clock e, em seguida, os transferiremos para a caixa de alarme principal.

Ao mesmo tempo, mudaremos os dados do LED do alarme principal para o registrador de deslocamento remoto para iluminar os LEDs.

Estaremos transferindo simultaneamente os dados do teclado e os dados do LED para o registrador de deslocamento.

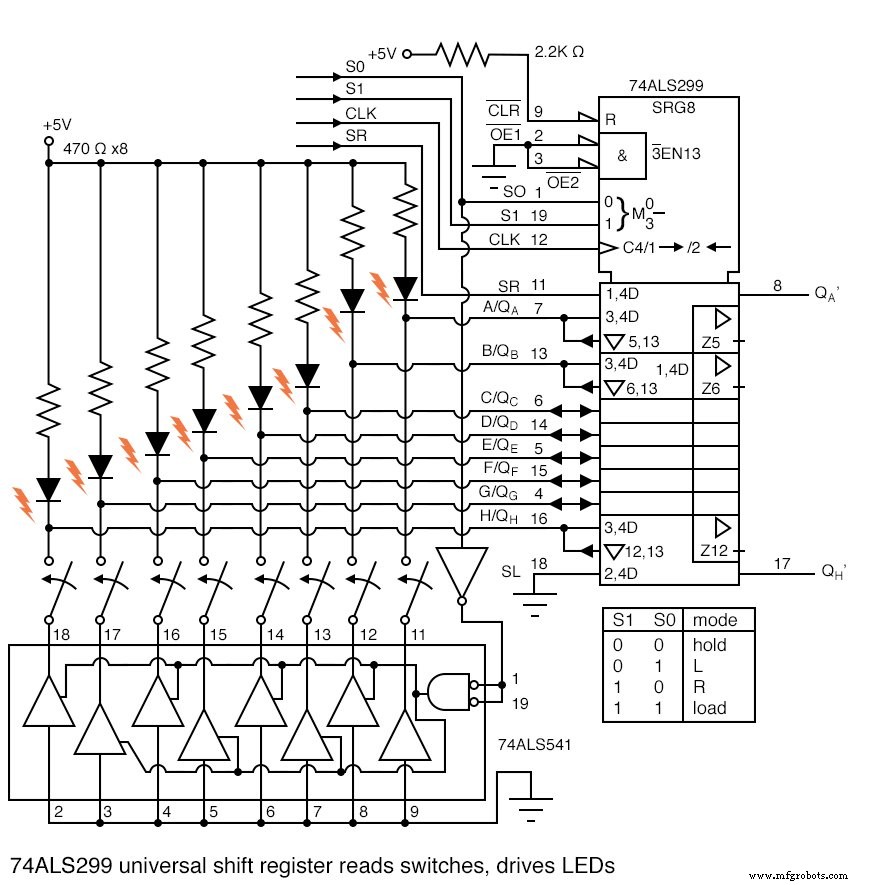

Oito LEDs e resistores limitadores de corrente são conectados aos oito pinos de E / S do registrador de deslocamento universal 74ALS299.

Os LEDS só podem ser acionados durante o Modo 3 com S1 =0 S0 =0 . O OE1 ’ e OE2 ’ habilitações tristate são aterradas para habilitar permanentemente as saídas tristate durante os modos 0, 1, 2 .

Isso fará com que os LEDS se acendam (pisquem) durante a mudança. Se isso fosse um problema, o EN1 ’E EN2’ pode ser não aterrado e em paralelo com S1 e S0 respectivamente para habilitar apenas os buffers tristate e acender os LEDS durante a espera, modo 3 . Vamos mantê-lo simples para este exemplo.

Durante o carregamento paralelo, S0 =1 invertido para 0, permite que os buffers tristate octal aterrem os limpadores de chave.

Os contatos de comutação superiores abertos são puxados para o nível lógico alto pela combinação de resistor-LED nas oito entradas.

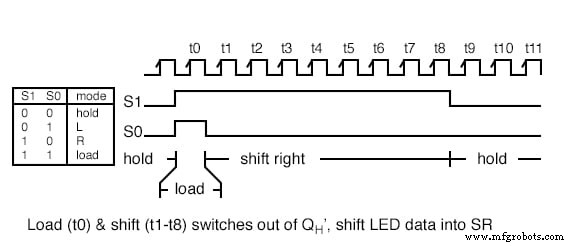

Qualquer fechamento de interruptor causará um curto na entrada baixa. Carregamos em paralelo os dados do switch no ‘299 no relógio t0 quando ambos S0 e S1 são altos. Veja as formas de onda abaixo.

Uma vez S0 vai baixo, oito relógios ( t0 para t8 ) dados de fechamento do interruptor de deslocamento para fora do '299 por meio do Q h ’ alfinete.

Ao mesmo tempo, novos dados de LED são transferidos em SR de 299 pelos mesmos oito relógios. Os dados do LED substituem os dados de fechamento da chave conforme a mudança prossegue.

Após o relógio do 8º turno, t8 , S1 vai para baixo para o modo de retenção de rendimento ( S1 S0 =00 ) Os dados no registrador de deslocamento permanecem os mesmos, mesmo se houver mais relógios, por exemplo, T9 , t10 etc.

De onde vêm as formas de onda? Eles poderiam ser gerados por um microprocessador se a taxa de clock não fosse superior a 100 kHz, caso em que seria inconveniente gerar qualquer clock após t8 .

Se o relógio estivesse na faixa de megahertz, ele funcionaria continuamente. O relógio, S1 e S0 seria gerado pela lógica digital, não mostrada aqui.

PLANILHAS RELACIONADAS:

- Planilha de registros de turnos

Registradores de deslocamento:Conversão de entrada serial, saída paralela (SIPO) Contadores de toque

Tecnologia industrial