Delta-Sigma ADC

Uma das tecnologias de ADC mais avançadas é o chamado delta-sigma, ou ΔΣ (usando a notação de letra grega apropriada). Em matemática e física, a letra grega maiúscula delta (Δ) representa a diferença ou alterar , enquanto a letra maiúscula sigma (Σ) representa a soma :a adição de vários termos juntos. Às vezes, esse conversor é referido pelas mesmas letras gregas na ordem inversa:sigma-delta ou ΣΔ.

Em um conversor ΔΣ, o sinal de tensão de entrada analógica é conectado à entrada de um integrador, produzindo uma taxa de mudança de tensão, ou inclinação, na saída correspondente à magnitude de entrada. Essa tensão em rampa é então comparada com o potencial de terra (0 volts) por um comparador.

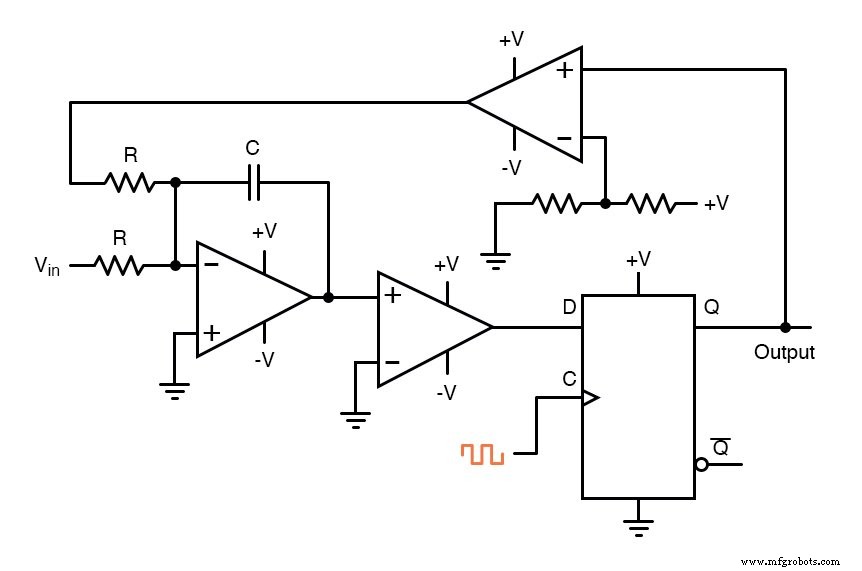

O comparador atua como uma espécie de ADC de 1 bit, produzindo 1 bit de saída (“alto” ou “baixo”) dependendo se a saída do integrador é positiva ou negativa. A saída do comparador é então travada por meio de um flip-flop tipo D sincronizado em alta frequência e realimentado para outro canal de entrada no integrador, para conduzir o integrador na direção de uma saída de 0 volt. O circuito básico é assim:

Diagrama Esquemático

O amplificador operacional mais à esquerda é o integrador (somador). O próximo amplificador operacional que o integrador alimenta é o comparador, ou ADC de 1 bit. Em seguida, vem o flip-flop tipo D, que trava a saída do comparador a cada pulso de clock, enviando um sinal "alto" ou "baixo" para o próximo comparador no topo do circuito.

Este comparador final é necessário para converter a tensão de saída de nível lógico 0V / 5V de polaridade única do flip-flop em um sinal de tensão + V / -V a ser alimentado de volta ao integrador. Se a saída do integrador for positiva, o primeiro comparador produzirá um sinal “alto” para a entrada D do flip-flop.

No próximo pulso de clock, este sinal “alto” será emitido da linha Q para a entrada não inversora do último comparador. Este último comparador, vendo uma tensão de entrada maior do que a tensão limite de 1/2 + V, satura em uma direção positiva, enviando um sinal + V completo para a outra entrada do integrador.

Este sinal de feedback + V tende a conduzir a saída do integrador em uma direção negativa. Se essa tensão de saída se tornar negativa, o loop de feedback enviará um sinal corretivo (-V) de volta à entrada superior do integrador para conduzi-lo em uma direção positiva.

Este é o conceito delta-sigma em ação:o primeiro comparador detecta uma diferença (Δ) entre a saída do integrador e zero volts. O integrador soma (Σ) a saída do comparador com o sinal de entrada analógico.

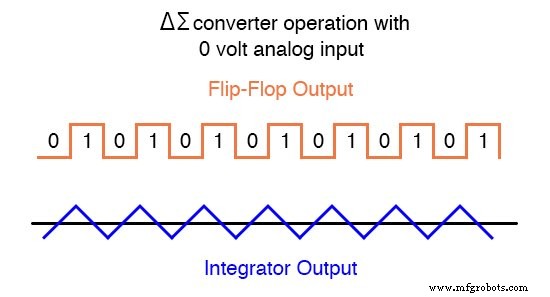

Funcionalmente, isso resulta em um fluxo serial de bits emitidos pelo flip-flop. Se a entrada analógica for zero volts, o integrador não terá tendência a aumentar tanto positiva quanto negativa, exceto em resposta à tensão de feedback.

Neste cenário, a saída do flip-flop irá oscilar continuamente entre "alto" e "baixo", enquanto o sistema de feedback "caça" para frente e para trás, tentando manter a saída do integrador em zero volts:

Formas de onda de saída

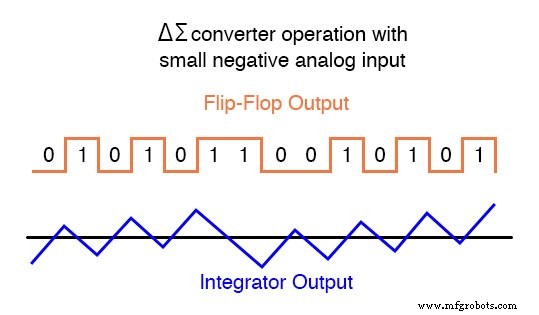

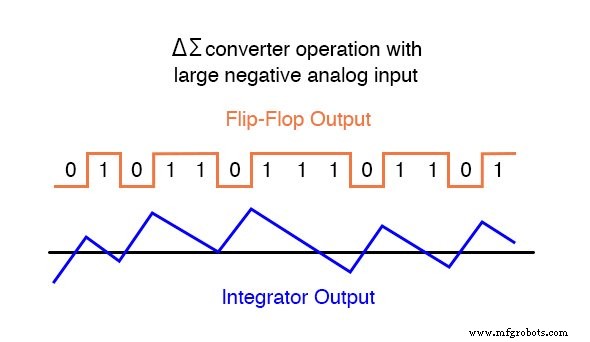

Se, no entanto, aplicarmos uma tensão de entrada analógica negativa, o integrador terá uma tendência a aumentar sua saída em uma direção positiva. O feedback só pode aumentar a rampa do integrador por uma tensão fixa ao longo de um tempo fixo e, portanto, a saída do fluxo de bits pelo flip-flop não será exatamente o mesmo:

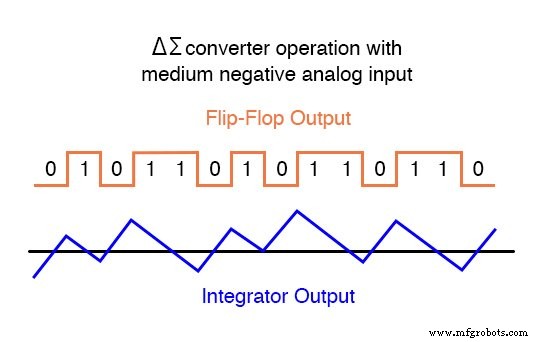

Ao aplicar um sinal de entrada analógico maior (negativo) ao integrador, forçamos sua saída a aumentar de forma abrupta em uma direção positiva. Assim, o sistema de feedback deve produzir mais 1 do que antes para trazer a saída do integrador de volta para zero volts:

À medida que o sinal de entrada analógico aumenta em magnitude, também aumenta a ocorrência de 1 na saída digital do flip-flop:

Uma saída de número binário paralela é obtida a partir deste circuito calculando a média do fluxo serial de bits juntos. Por exemplo, um circuito de contador pode ser projetado para coletar o número total de saída de 1 pelo flip-flop em um determinado número de pulsos de relógio. Essa contagem seria então indicativa da tensão de entrada analógica.

Existem variações sobre este tema, empregando vários estágios integradores e / ou circuitos comparadores com saída de mais de 1 bit, mas um conceito comum a todos os conversores ΔΣ é o de sobreamostragem . Oversampling é quando várias amostras de um sinal analógico são obtidas por um ADC (neste caso, um ADC de 1 bit), e essas amostras digitalizadas são calculadas.

O resultado final é um aumento efetivo no número de bits resolvidos do sinal. Em outras palavras, um ADC de 1 bit com sobreamostragem pode fazer o mesmo trabalho que um ADC de 8 bits com amostragem única, embora em uma taxa mais lenta.

PLANILHA RELACIONADA:

- Planilha de conversão analógico para digital

Tecnologia industrial