Tutorial - Introdução ao VHDL

VHDL é uma sigla horrível. Significa V HSIC H hardware D inscrição L língua. Uma sigla dentro de uma sigla, incrível! VHSIC significa V ery H alto S fiz xixi eu C integrado ircuito. Portanto, o VHDL expandido é V Circuito Integrado de Alta Velocidade H hardware D inscrição L língua. Ufa, isso é um bocado. VHDL é uma das duas linguagens usadas pela educação e negócios para projetar FPGAs e ASICs. Você pode se beneficiar primeiro de uma introdução a FPGAs e ASICs se não estiver familiarizado com essas peças fascinantes de circuitos. VHDL e Verilog são as duas linguagens que os designers digitais usam para descrever seus circuitos e são diferentes por design das linguagens de software tradicionais, como C e Java.

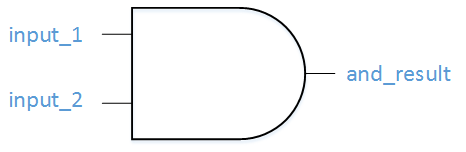

Para o exemplo abaixo, criaremos um arquivo VHDL que descreve um E Portão. Para relembrar, um And Gate simples tem duas entradas e uma saída. A saída é igual a 1 somente quando ambas as entradas são iguais a 1. Abaixo está uma imagem do And Gate que descreveremos com VHDL.

An And Gate

An And Gate Vamos lá! A unidade fundamental do VHDL é chamada de sinal . Por enquanto, vamos supor que um sinal pode ser 0 ou 1 (na verdade, existem outras possibilidades, mas chegaremos a isso). Aqui está alguma lógica básica de VHDL:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

A primeira linha de código define um sinal do tipo std_logic e é chamado and_gate. Std_logic é o tipo mais comumente usado para definir sinais, mas há outros que você aprenderá. Este código irá gerar uma porta AND com uma única saída (and_gate) e 2 entradas (input_1 e input_2). A palavra-chave “and” é reservada em VHDL. O operador <=é conhecido como operador de atribuição. Ao analisar verbalmente o código acima, você pode dizer em voz alta:“The signal and_gate GETS input_1 and-ed with input_2.”

Agora você pode estar se perguntando de onde vêm input_1 e input_2. Bem, como o nome indica, eles são entradas para este arquivo, então você precisa informar as ferramentas sobre eles. As entradas e saídas de um arquivo são definidas em uma entidade . Uma entidade contém uma porta que define todas as entradas e saídas de um arquivo. Vamos criar uma entidade simples:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

Esta é a sua entidade básica. Ele define uma entidade chamada example_and e 3 sinais, 2 entradas e 1 saída, todos do tipo std_logic. Uma outra palavra-chave VHDL é necessária para completar isso e é arquitetura . Uma arquitetura é usada para descrever a funcionalidade de uma entidade específica. Pense nisso como um trabalho de tese:a entidade é o índice e a arquitetura é o conteúdo. Vamos criar uma arquitetura para esta entidade:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

O código acima define uma arquitetura chamada rtl de entidade example_and. Todos os sinais usados pela arquitetura devem ser definidos entre as palavras-chave “is” e “begin”. A lógica da arquitetura real fica entre as palavras-chave “begin” e “end”. Você está quase terminando com este arquivo. Uma última coisa que você precisa dizer às ferramentas é qual biblioteca usar. Uma biblioteca define como certas palavras-chave se comportam em seu arquivo. Por enquanto, apenas tome como certo que você precisa ter essas 2 linhas no topo do seu arquivo:

library ieee; use ieee.std_logic_1164.all;

Parabéns! Você criou seu primeiro arquivo VHDL. Você pode ver o arquivo completo aqui:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

Parece que você teve que escrever muito código apenas para criar um portão estúpido? Em primeiro lugar, e os portões não são estúpidos. Em segundo lugar, você está correto; VHDL é uma linguagem muito detalhada. Acostume-se com o fato de que fazer algo que era muito fácil no software levará muito mais tempo em um HDL como Verilog ou VHDL. Mas basta pedir a um cara de software para tentar gerar uma imagem para um monitor VGA que exibe o Jogo da Vida de Conway e ver sua cabeça girar com espanto! A propósito, esse vídeo é criado com VHDL e um FPGA. Você será capaz de fazer isso em breve!

VHDL

- Registros - Exemplo de VHDL

- Uma introdução à estereolitografia (SLA)

- Uma introdução à liga de titânio

- Introdução aos Circuitos DC

- Introdução aos circuitos CA

- Introdução ao SPICE

- C Tutorial

- Tutorial Verilog

- Introdução aos harmônicos:parte 1

- Introdução ao SINUMERIK 808D – Vídeo Tutorial Torneamento Parte 1