Como criar um vetor de sinal em VHDL:std_logic_vector

O

std_logic_vector tipo pode ser usado para criar barramentos de sinal em VHDL. O std_logic é o tipo mais comumente usado em VHDL, e o std_logic_vector é a versão de matriz dele. Enquanto o

std_logic é ótimo para modelar o valor que pode ser carregado por um único fio, não é muito prático para implementar coleções de fios indo ou vindo de componentes. O std_logic_vector é um tipo composto, o que significa que é uma coleção de subelementos. Sinais ou variáveis do std_logic_vector tipo pode conter um número arbitrário de std_logic elementos. Esta postagem do blog faz parte da série de tutoriais básicos de VHDL.

A sintaxe para declarar

std_logic_vector sinais é:signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>; ou

signal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>; onde

<name> é um nome arbitrário para o sinal e <initial_value> é um valor inicial opcional. O <lsb> é o índice do bit menos significativo e <msb> é o índice do bit mais significativo. O

to ou downto especifica a direção do alcance do barramento, basicamente sua endianess. Embora ambos funcionem igualmente bem, é mais comum para o designer de VHDL declarar vetores usando downto . Portanto, recomendo que você sempre use downto quando você declara vetores de bits para evitar confusão. O código VHDL para declarar um sinal vetorial que pode conter um byte:

signal MySlv : std_logic_vector(7 downto 0); O código VHDL para declarar um sinal vetorial que pode conter um bit:

signal MySlv : std_logic_vector(0 downto 0); O código VHDL para declarar um sinal vetorial que pode conter zero bits (um intervalo vazio ):

signal MySlv : std_logic_vector(-1 downto 0); Exercício

Neste tutorial em vídeo, aprenderemos como declarar

std_logic_vector sinais e dar-lhes valores iniciais. Também aprendemos como iterar sobre os bits em um vetor usando um For-Loop para criar um registrador de deslocamento :O código final que criamos neste tutorial:

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

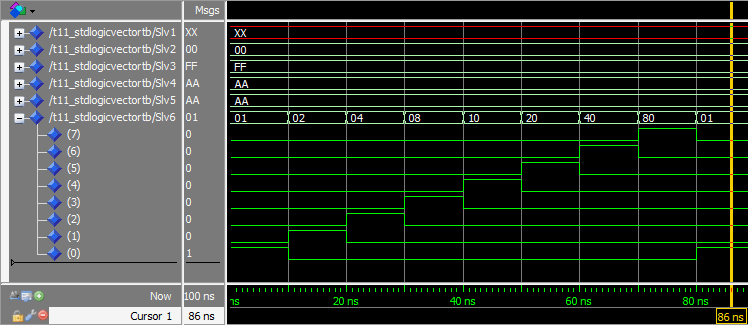

A janela de forma de onda no ModelSim depois que pressionamos executar e ampliamos a linha do tempo:

Análise

Neste exercício, declaramos seis

std_logic_vector barramentos, cada um com oito bits de comprimento (um byte). Sinal

Slv1 foi declarado sem um valor inicial. O barramento é visto com o valor XX na captura de tela da forma de onda. Isso ocorre porque o valor exibido no barramento está em hexadecimais e XX indica um valor não hexadecimal. Mas quando expandimos o barramento na forma de onda, pudemos ver que os bits individuais eram de fato U. Sinal

Slv2 foi declarado usando um valor inicial de todos os 0's. Em vez de especificar o valor exato para cada bit, usamos (other => '0') no lugar do valor inicial. Isso é conhecido como um agregado atribuição. A parte importante é que ele definirá todos os bits no vetor para o que você especificar, não importa quanto tempo seja. Sinal

Slv3 foi declarado usando uma atribuição agregada para dar a todos os bits o valor inicial de 1. Podemos ver FF exibido neste sinal na forma de onda, que é hexadecimal para oito 1s. Sinal

Slv4 foi declarado com um valor inicial especificado em hexadecimal, AA. Cada dígito hexadecimal tem 4 bits, portanto, devemos fornecer dois dígitos (AA) para o nosso vetor que tem 8 bits. Sinal

Slv5 declara exatamente o mesmo valor inicial que Slv4 , mas agora nós o especificamos como o valor binário 10101010. Podemos ver pela forma de onda que ambos os sinais têm o valor hexadecimal AA. Sinal

Slv6 foi declarado com um valor inicial de zeros, exceto para o bit mais à direita que era '1' . Usamos um processo para criar um registrador de deslocamento a partir deste sinal. O registrador de deslocamento, como o nome indica, desloca o conteúdo do vetor uma posição para a esquerda a cada 10 nanossegundos. Nosso processo acorda a cada 10 ns e o For-Loop desloca todos os bits do vetor uma posição para a esquerda. O bit final é deslocado de volta para o primeiro índice pelo

Slv6(Slv6'right) <= Slv6(Slv6'left); declaração. Na forma de onda podemos ver o '1' ondulação através do vetor. Esta é uma visualização de como o

'1' propaga através do nosso registrador de deslocamento:

Usando o

'left' e 'right atributos, tornamos nosso código mais genérico. Se alterarmos a largura de Sig6 , o processo ainda funcionará. É uma boa prática de design usar atributos onde você puder em vez de codificar valores. Você pode estar se perguntando se existem mais atributos que você pode usar, e existem. Não falarei mais sobre eles nesta série de tutoriais, porque os considero recursos avançados de VHDL.

Retirada

- Vetores de N bits devem ser declarados usando

std_logic_vector(N-1 downto 0) - Um vetor pode ser atribuído como um todo ou bits dentro dele podem ser acessados individualmente

- Todos os bits em um vetor podem ser zerados usando a atribuição agregada

(others => '0') - O código pode ser mais genérico usando atributos como

'lefte'right

Faça o Basic VHDL Quiz – parte 2 »

ou

Vá para o próximo tutorial »

VHDL

- Exemplos de conversões de VHDL

- Assinado vs. Não assinado em VHDL

- Como criar uma lista de strings em VHDL

- Como criar um testbench orientado por Tcl para um módulo de bloqueio de código VHDL

- Como parar a simulação em um testbench VHDL

- Como criar um controlador PWM em VHDL

- Como gerar números aleatórios em VHDL

- Como criar um buffer de anel FIFO em VHDL

- Como criar um testbench de autoverificação

- Como criar uma lista vinculada em VHDL