Um guia para acelerar aplicativos com instruções personalizadas RISC-V certas

A arquitetura de conjunto de instruções abertas (ISA) de RISC-V permite ampla flexibilidade na implementação e oferece recursos opcionais que podem permitir novas abordagens para resolver as compensações de design de hardware-software. Com base em uma estrutura modular, várias extensões e opções padrão podem ser usadas para configurar o processador básico como ponto de partida. Ainda assim, o verdadeiro valor reside nas oportunidades que o RISC-V oferece aos desenvolvedores para criar novas extensões, instruções e configurações que atendam exclusivamente às necessidades de suas idéias de aplicativos inovadores.

O desafio do software para ISAs fixos

Tradicionalmente, as ISAs são propriedade intelectual (IP) de organizações comerciais que desejam vender microprocessadores ou microcontroladores ou licenciar seus projetos para uso de terceiros. Os desenvolvedores integrados são deixados para executar o software de benchmarking para determinar qual solução é melhor otimizada para as necessidades de seus aplicativos. Devido ao custo de desenvolver um ISA independente com todo o ecossistema necessário, os fornecedores de semicondutores contam cada vez mais com os ISAs fixos padrão oferecidos pelos principais provedores de IP, contando com a Lei de Moore e periféricos integrados para oferecer diferenciação, como energia ultrabaixa , para seus clientes.

O desafio aqui é que as instruções usadas para executar o código não podem ser alteradas. Portanto, as eficiências que poderiam ser potencialmente obtidas por, por exemplo, uma instrução otimizada para um algoritmo de criptografia, não podem ser realizadas. Isso pode significar que o aplicativo do desenvolvedor é muito lento, potencialmente usa muita energia ou perde regularmente um prazo final em tempo real em um loop de controle. Mesmo com a melhor vontade do mundo, esses são fatores que são desafiadores para resolver puramente com melhorias na fabricação de semicondutores ou redução de processos.

O RISC-V ISA começou como um projeto na University of California, Berkeley e agora é mantido pela RISC-V International Association, um grupo sem fins lucrativos com mais de 300 membros. Eles contribuem com as especificações do ISA, ferramentas de software, como simuladores e compiladores, e o resto do ecossistema necessário para dar suporte a tal empreendimento. Se faz sentido ou não usar depende de se um de dois fatores pode ser alavancado:é gratuito em termos de licença ou a liberdade que oferece.

Sendo aberto e disponível gratuitamente, ele fornece uma plataforma de processamento básica que pode ser facilmente usada tanto pela academia para ensino e pesquisa, quanto por aplicações comerciais. Um ISA aberto também oferece suporte a uma série de modelos de negócios para desenvolvedores que buscam obter IP de semicondutores, desde o provedor de IP comercial até projetos de código aberto e projetos autoconstruídos. As organizações comerciais também acham isso atraente, utilizando-o em FPGAs, SoCs ou mesmo no núcleo de um microcontrolador ou oferta de produto padrão.

Graças à liberdade que oferece, a academia pode investigar novas abordagens para enfrentar os desafios de computação, implementando qualquer coisa, desde novas instruções e outros aceleradores, designs heterogêneos de vários núcleos e múltiplos núcleos, além de diferentes opções de microarquitetura. Muitas dessas opções também são atraentes para startups e empresas que buscam enfrentar desafios complexos, como chipsets de inteligência artificial (IA) de baixa potência que operam na borda, adicionando instruções personalizadas ajustadas aos requisitos do aplicativo final.

Como o ecossistema foi estabelecido com a flexibilidade RISC-V incorporada, qualquer configuração padrão ou extensão personalizada deve ser capaz de aproveitar as ferramentas e o software dentro da estrutura compatível com ISA.

Compreendendo a flexibilidade do ISA RISC-V aberto

Graças à acessibilidade do ISA RISC-V e ferramentas associadas, é simples iniciar um projeto investigativo para avaliar sua adequação para uso em uma aplicação específica. As ferramentas de simulação permitem que um ISA básico padrão seja testado para determinar o desempenho pronto para uso. Por exemplo, um bom ponto de partida seria uma configuração RISC-V de 32 bits com extensões inteiras “I” e multiplicação “M” (que podem ser referenciadas como RV32IM) fornecendo suporte para um conjunto base de instruções inteiras de 32 bits; mais opções estão disponíveis, mas isso é suficiente para este exemplo. Isso é então instanciado junto com uma memória simulada incluindo atrasos de acesso e estados de espera.

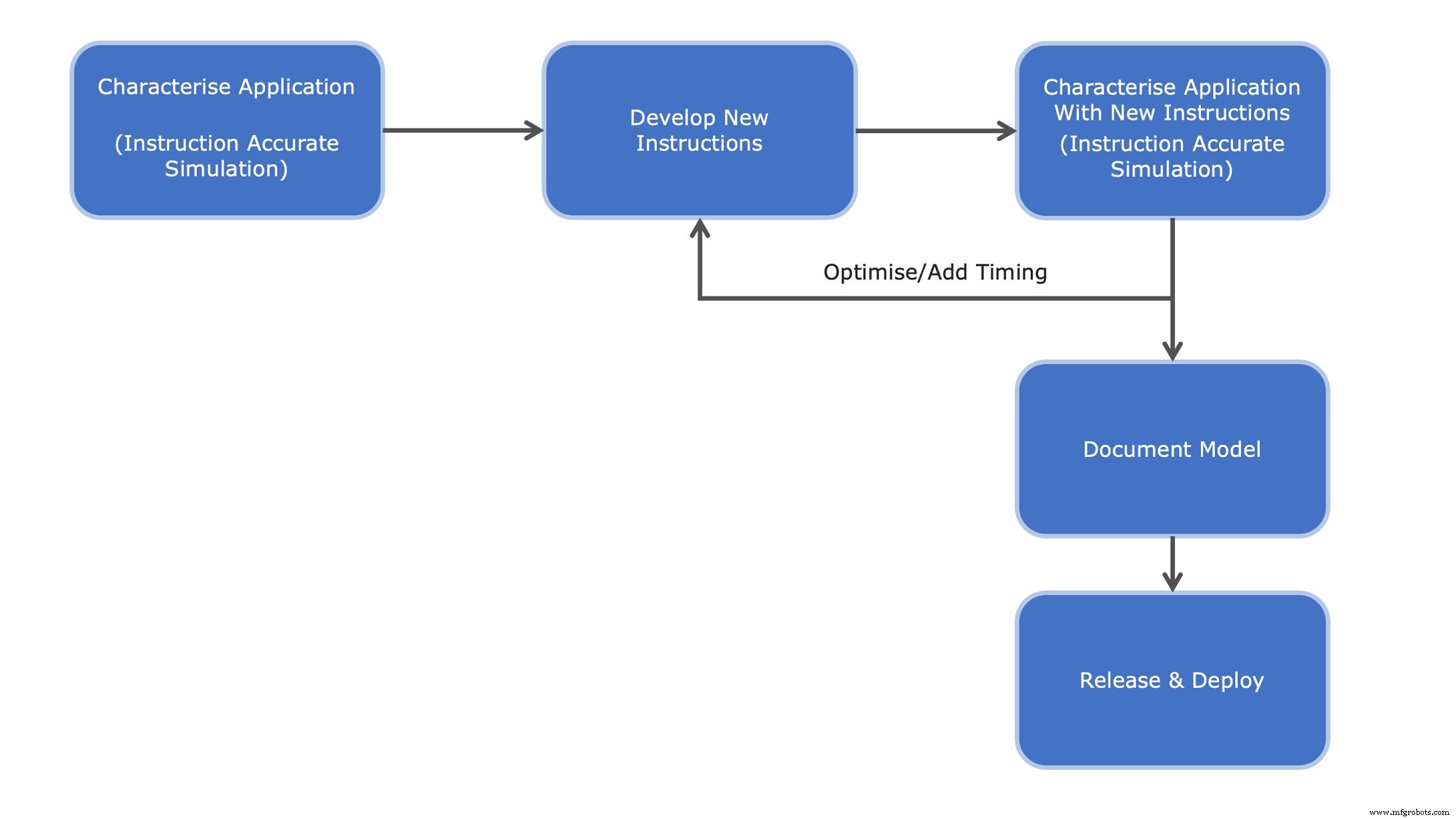

Um aplicativo escrito em C / C ++ pode ser compilado cruzado usando cadeias de ferramentas padrão. Isso pode ser executado em bare metal ou como parte de um sistema operacional (tempo real) (RTOS / OS). O código binário resultante é então executado usando ferramentas como um simulador de conjunto de instruções (ISS) que permite que o modelo de processador de base escolhido seja integrado e simulado (figura 1). Este ambiente também fornece funcionalidade de entrada / saída padrão e acesso ao sistema de arquivos host. Ferramentas de ambiente de desenvolvimento integrado (IDE) padrão, como Eclipse, podem então ser usadas para controlar a execução de código, fazendo interface por meio do depurador GNU GDB.

A partir daqui, por meio de um processo de criação de perfil e análise, os candidatos à instrução são identificados, projetados e modelados. Usando o código do aplicativo original como o modelo funcional básico, a melhoria resultante pode ser rapidamente testada, verificada e o desempenho comparado. Essa iteração rápida de criação de perfil e análise permite a rápida seleção e otimização de instruções que valem a pena implementar. A documentação pode ser gerada a partir do modelo e forma a base de uma especificação de função para o projeto da lógica de transferência de registro (RTL) e um modelo otimizado.

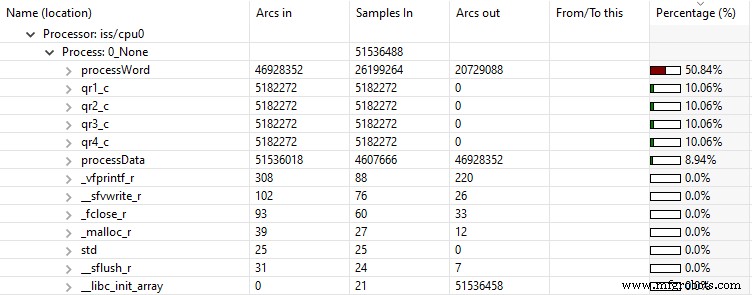

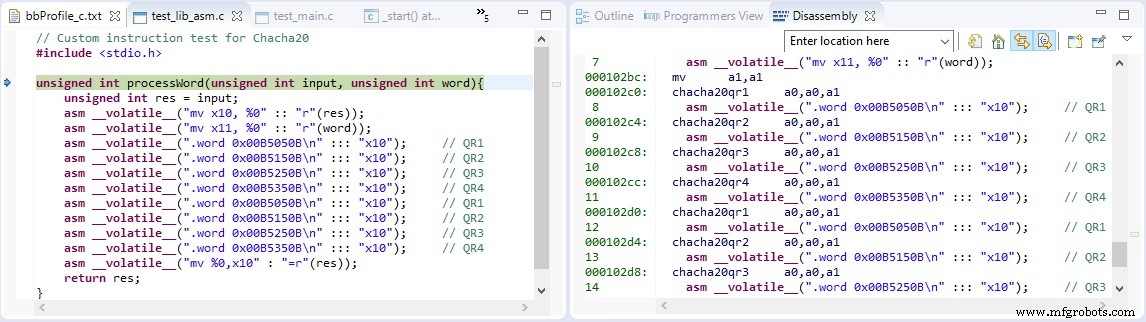

Por exemplo, um algoritmo de criptografia como ChaCha20 pode ser crítico para um aplicativo específico. O código-fonte disponível pode ser compilado para uma base RV32IM “vanilla”, executado e, em seguida, analisado com o tempo estimado do ciclo de instrução usando o perfil de bloco básico para determinar quanto tempo foi gasto em quais seções do código. O núcleo do algoritmo ChaCha20 faz uso intenso de instruções XOR e de rotação conhecidas como quartos de volta (figura 2). Os resultados da criação de perfil de bloco imediatamente destacam que a maior parte do tempo de execução é gasto nessas funções.

A visualização gráfica desses pontos de acesso também pode ser gerada usando uma ferramenta de verificação, análise e perfil (VAP). Em vez de fornecer uma saída textual, o tempo de execução é fornecido como uma árvore de estatísticas recolhíveis, ajudando a visualizar melhor os pontos de acesso com uma alta proporção de instruções executadas. Isso pode ser visto na figura 3, onde a função processWord () implementa o algoritmo ChaCha20, chamando por sua vez os quatro qrx_c funções para implementar as funções de um quarto de volta necessárias.

Revendo o código assembler gerado pelo compilador e / ou executando o perfil de bloco básico, é então possível determinar quais instruções e combinações de instruções foram usadas para implementar o algoritmo. A partir daqui, a próxima etapa é determinar quais instruções personalizadas, dentro dos limites das especificações do ISA, podem potencialmente aumentar a velocidade de execução.

Determinar a melhoria potencial que o RISC-V pode proporcionar

O algoritmo ChaCha20 faz uso intenso de um XOR acoplado a uma rotação à esquerda de 7, 8, 12 e 16 bits. Usar as instruções disponíveis da especificação base RV32IM mostra que isso requer uma instrução XOR seguida por uma instrução shift-left. Isso significa que há potencial para otimizar essas duas etapas em quatro instruções dedicadas que implementam um XOR junto com 7, 8, 12 ou 16 bits de rotação à esquerda.

Sendo uma arquitetura de armazenamento de carga, quaisquer instruções personalizadas devem assumir que os dados a serem manipulados já residem em um dos registros de 32 bits deste RISC-V. Isso determina imediatamente que uma instrução de tipo R (registro) será necessária que pode ser localizada em custom-1 decodifique o espaço (figura 4).

O ISA fornece uma estrutura clara para tais instruções. Seguindo essas regras, podemos determinar rapidamente como codificar nossas novas instruções. Os 7 bits inferiores são definidos como o opcode, que é atribuído um valor que o marca como uma instrução personalizada no custom-1 decodificar o espaço. Isso é oposto ao OP ou OP-IMM opcodes que são usados para as instruções XOR e shift-left existentes, respectivamente.

O ISA fornece uma estrutura clara para tais instruções. Seguindo essas regras, podemos determinar rapidamente como codificar nossas novas instruções. Os 7 bits inferiores são definidos como o opcode, que é atribuído um valor que o marca como uma instrução personalizada no custom-1 decodificar o espaço. Isso é oposto ao OP ou OP-IMM opcodes que são usados para as instruções XOR e shift-left existentes, respectivamente. Três blocos predefinidos de bits são reservados na definição ISA para prescrever os dois registradores de origem e o registrador de destino para o resultado. Isso deixa um bloco de bits conhecido como funct3 . Esses três bits nos fornecem espaço para codificar oito instruções possíveis, quatro das quais serão usadas neste exemplo.

Sem exigir a implementação detalhada do hardware do RTL para essas instruções, é possível simulá-las no ambiente do ISS para ver se teriam algum benefício para o desafio enfrentado. As quatro novas instruções são modeladas usando a interface de programação de aplicativos (API) VMI de plataformas virtuais abertas (OVP). Isso permite ao desenvolvedor iterar rapidamente o design das instruções que fornecem o resultado ideal desejado com base nas novas instruções para o aplicativo de destino. Somente quando isso for alcançado, é necessário comprometer recursos para uma implementação de RTL.

Para o propósito de avaliação funcional inicial das instruções, existem duas abordagens possíveis. A primeira é chamar a versão C / C ++ original do algoritmo, vinculando as novas instruções a esta função (figura 5a). A segunda é implementá-los como instruções de metamorfose VMI que criam o mesmo comportamento (figura 5b). Isso tem a vantagem de ser mais eficiente e é a abordagem recomendada.

Obviamente, a mera existência de novas instruções não significa que um compilador possa fazer uso delas imediatamente. Portanto, o aplicativo C / C ++ original precisa ser reescrito usando o montador embutido e compilado cruzado para fazer uso das novas instruções. Como o perfil e a análise de instruções candidatas podem ser uma tarefa iterativa, a abordagem baseada em intrínseca fornece a maneira mais eficiente de adaptar o aplicativo C original para usar as novas instruções personalizadas.

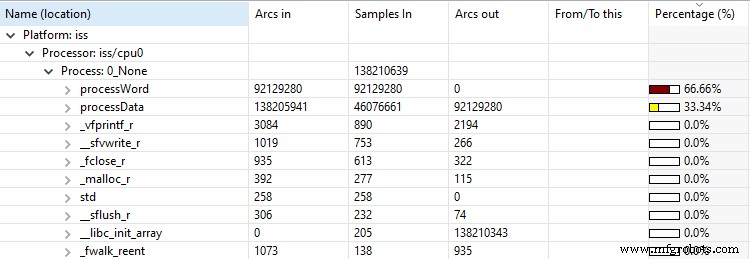

A implementação da base RISC-V carregada no simulador também precisa estar ciente das novas instruções para se beneficiar delas. Isso é obtido incluindo-os no modelo antes de executar novamente a simulação. Neste exemplo particular, repetir o perfil indica menos tempo geral gasto na execução do algoritmo (figura 6). A ferramenta de criação de perfil Imperas VAP mostra que o processWord () , usando as instruções in-lined dedicadas, agora é responsável por 66% da execução geral do algoritmo, mas o tempo de execução geral do algoritmo é bastante reduzido (figura 6b).

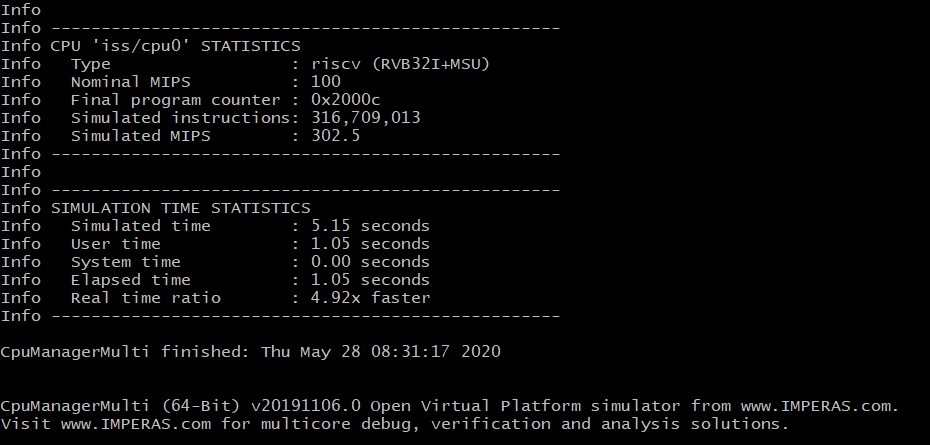

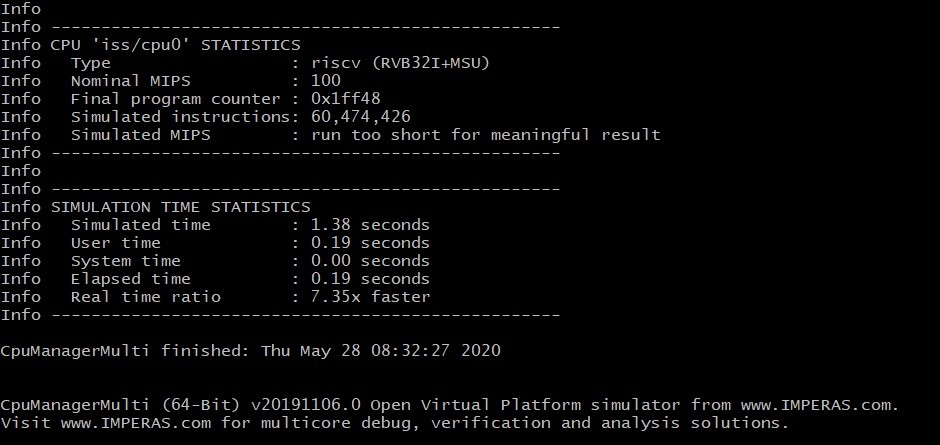

Resultados com implementação C original

Instruções Simuladas de Informações:316.709.013

Tempo Simulado de Informações:5,15 segundos

Resultados com instruções personalizadas

Instruções simuladas de informações:60.474.426

Tempo simulado de informações:1,38 segundos

Uma vez que a funcionalidade correta tenha sido determinada, o modelo é refinado ainda mais, declarando o tempo de execução para cada instrução nos ciclos do processador. Outras rodadas de simulação podem ser usadas para determinar qualquer melhoria de desempenho, mesmo levando em consideração os estados de espera associados aos acessos à memória que podem ocorrer em uma eventual implementação de hardware.

Graças à forte integração com IDEs de código aberto comuns e ferramentas GDB, a depuração completa da solução pode ser realizada em conjunto com o design RISC-V otimizado antes de comprometer o design com uma implementação de hardware (figura 7).

Movendo da simulação para a implementação

Com a potencial melhoria de desempenho determinada, a próxima etapa requer a implementação das quatro novas instruções em RTL. Graças ao trabalho preliminar realizado, esta se torna a especificação funcional que define os requisitos e também pode ser usada como parte do plano de teste de verificação RTL como um modelo de referência de ouro. Embora o uso de funções intrínsecas no aplicativo C ajudasse na criação de perfil e análise de instruções customizadas, essa abordagem também pode ser utilizada para o desenvolvimento de código de produção futuro ou pode ser considerada para aprimoramentos potenciais da cadeia de ferramentas do compilador.

A outra tarefa essencial remanescente, a documentação, também é um processo simples. Todos os modelos de processador rápido de plataformas virtuais abertas (OVP) incluem documentação que pode ser estendida para cobrir a funcionalidade de alterações e modificações. Seguindo o modelo fornecido, as novas instruções podem ser declaradas e descritas, permitindo que a comunidade de desenvolvedores descubra sua capacidade e faça uso delas. A documentação é então convertida em um arquivo TeX a partir do qual um PDF pode ser gerado (figura 8).

Resumo

Com as liberdades do ISA aberto de RISC-V, além das opções e recursos padrão definidos na especificação, os usuários podem desenvolver outras extensões e instruções personalizadas. Na sua forma mais simples, permite modelos de negócios novos e criativos, incluindo implementações comerciais e de código aberto, além de permitir uma liberdade mais ampla para explorar recursos de valor agregado além das abordagens tradicionais convencionais.

No entanto, o verdadeiro valor vem de tomar um núcleo de base totalmente desenvolvido, documentado e com suporte e modificá-lo para atender às necessidades específicas do aplicativo. Por meio de análise cuidadosa do aplicativo, criação de perfil de código e simulação, melhorias significativas de desempenho podem ser obtidas, o que não poderia ser realizado por meio de ISAs fixos. Tudo isso pode ser desenvolvido e traçado com cargas de trabalho de aplicativos reais antes de iniciar a implementação detalhada do hardware.

Integrado

- Criação de perfil de aplicativos distribuídos com Perf

- Um breve guia para impressão 3D com jato de pasta

- Microchip:dimensione aplicações espaciais com MCUs Core COTS-to-radiação-tolerantes

- Renesas:RX72M MCUs com suporte EtherCAT para aplicações industriais

- Axiomtek:sistema integrado com switch PoE gerenciado de camada 2 integrado

- Renegociação de custos com fornecedores existentes:um guia

- Roteador de madeira CNC - com aplicativos incríveis

- Introdução à IA em seguros:um guia introdutório

- 5 Aplicações do mundo real de IA na medicina (com exemplos)

- Um guia para sapatas e pastilhas de freio personalizadas para aplicações ferroviárias de alta velocidade