Qual tipo de codificação devo usar? Aplicativos FPGA de exemplo

Siga três experimentos que mostram o processo de determinação de qual tipo de codificação é adequado para um determinado FPGA.

Qual tipo de codificação devo usar para meu FPGA? Conforme discutido no artigo anterior, um compilador geralmente decidirá isso por você - e eu recomendo que você siga o que o compilador decidir.

No entanto, é importante entender as diferenças entre os tipos de codificação e por que um compilador pode chegar a uma determinada conclusão. Com isso em mente, este artigo o conduzirá por um experimento que mostra um exemplo de aplicativo FPGA e discute, passo a passo, qual tipo de codificação é melhor.

Até agora nesta série, discutimos como criar uma máquina de estado finito (FSM) com Verilog, o estado inicial e como a memória afeta a codificação FPGA e uma visão geral de alto nível comparando a codificação binária vs. one-hot vs. Gray .

O sistema em teste

Para este experimento, eu queria instanciar uma máquina de estado um grande número de vezes para ampliar as diferenças no hardware resultante quando as codificações binárias, Gray e one-hot são usadas.

O sistema que finalmente escolhi é o Jogo da Vida de Conway, um autômato celular que simula o comportamento de células vivas em seu ambiente, que é uma matriz retangular de células 2D. O Jogo da Vida de Conway é uma simulação dessas células nascendo, reproduzindo e morrendo, de acordo com um conjunto simples de regras que cada célula segue para determinar o que acontece no próximo ciclo. Cada célula viva pode sobreviver ou morrer, e cada célula morta pode permanecer morta ou tornar-se viva. Aqui estão as regras para cada ciclo:

- Células vivas com dois ou três vizinhos vivos sobrevivem.

- Células mortas com três vizinhos vivos ganham vida.

- Todas as outras células morrem ou permanecem mortas.

Essas regras criam muitos comportamentos e padrões interessantes que foram amplamente estudados na ciência da computação.

É assim que o Jogo da Vida de Conway se parece ao executar o que é conhecido como um canhão planador único Gosper.

Uma variação do Jogo da Vida de Conway, conhecido como Arma Planador de Bill Gosper. Gif criado por Lucas Vieira [CC BY-SA 3.0]

Código Verilog

De volta ao nosso sistema de teste, cada célula foi projetada como uma máquina de estados com oito estados. É certo que a lógica de uma célula no Jogo da Vida de Conway pode ser resolvida em um ciclo, mas decidi fazer uma máquina de 8 estados para ter uma diferença notável ao usar codificações diferentes. Os estados são usados para contar os vizinhos vivos de uma célula.

O seguinte trecho de código Verilog mostra a estrutura do módulo de célula para essas máquinas, incluindo a codificação binária original de estados.

`define STATE_0 3'b000 `define STATE_1 3'b001 `define STATE_2 3'b010 `define STATE_3 3'b011 `define STATE_4 3'b100 `define STATE_5 3'b101 `define STATE_6 3'b110 `define STATE_7 3'b111 módulo LifeCell ( input clk, entrada nrst, input seed, input [7:0] vizinhos, output reg alive); reg [2:0] estado; always @ (posedge clk) if (nrst ==0) estado <=`STATE_0; else caso (estado) `STATE_0:começo // ... estado <=`STATE_1; fim `STATE_1:começar // ... estado <=`STATE_2; fim // ... `STATE_7:começar // ... estado <=`STATE_1; fim endcase endmodule Se você quiser dar uma olhada no código, sinta-se à vontade para verificar o projeto no GitHub.

Implementações de codificação FPGA

O sistema foi sintetizado e implementado como um mundo de células 23x23, em um total de 27 variantes:três FSMs diferentes foram usados, todos com as três codificações mencionadas acima, todos em três FPGAs alvo diferentes.

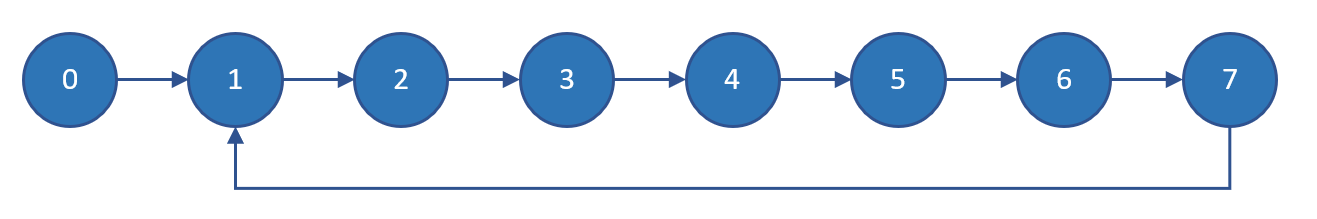

FSM # 1:Modelo Original

Essa máquina tem um estado inicial que é executado uma vez e, em seguida, é executado em um ciclo pelos sete estados restantes. Esta é uma sequência quase completa, então a codificação Gray parecia promissora para mim no início.

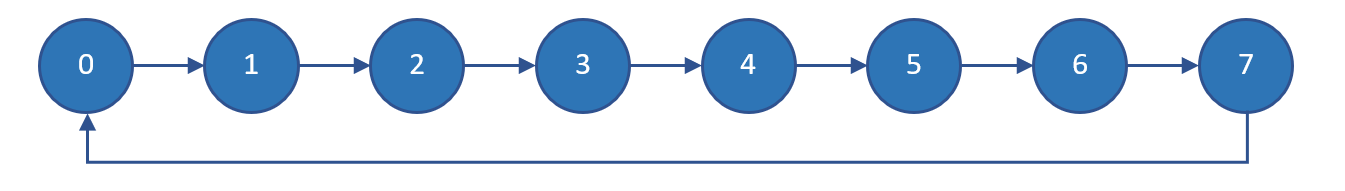

FSM # 2:Sequência A

Esta máquina se comporta como um contador de 3 bits, então eu também esperava que a codificação Gray esmagasse a concorrência.

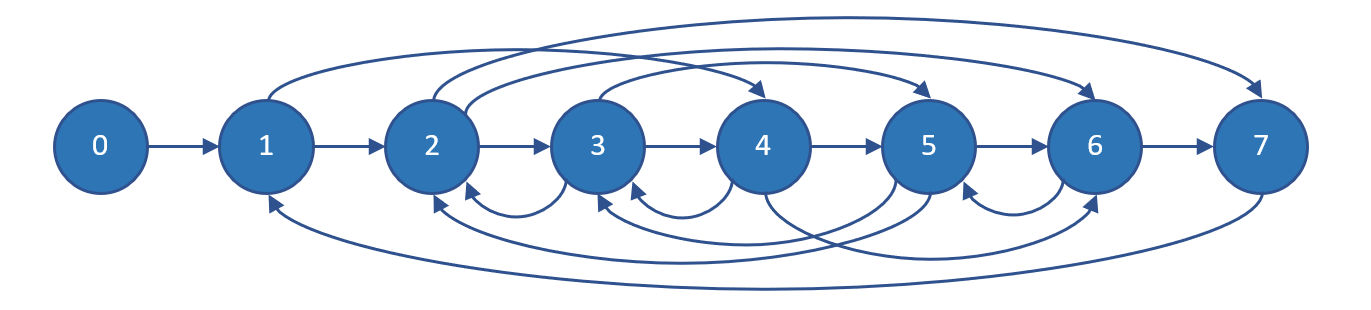

FSM # 3:Um emaranhado arbitrário

Esta máquina tem o mesmo caminho crítico do FSM # 1, mas passa por um caminho arbitrário quando o número de vizinhos vivos é superior a 3.

Para esse comportamento de transição de estado arbitrário, eu esperava que a codificação one-hot fosse a melhor escolha.

Arquiteturas de destino

O sistema foi implementado para três FPGAs alvo, usando a ferramenta de desenvolvimento de seu fornecedor:

- Xilinx Vivado Suite, para um FPGA Artix 7

- Intel Quartus Prime, para um Cyclone V FPGA

- Lattice Diamond, para um LatticeXP2 FPGA

Comparando os resultados

Comparar o desempenho de dois ou mais sistemas é difícil, principalmente porque o veredicto depende das métricas que usamos e de quais aspectos consideramos mais importantes do que outros. Para este experimento, reuni os seguintes dados para produzir uma pontuação para cada implementação:

- Número de unidades lógicas. São LUTs (tabelas de pesquisa) para FPGAs Xilinx e Lattice ou ALMs para FPGAs Intel. Pontuação:1 ponto.

- Número de registros. Pontuação:1 ponto.

- Freqüência máxima estimada. Pontuação:2 pontos.

- Energia estimada do chip. Pontuação:2 pontos.

Para cada implementação, esses quatro aspectos foram comparados entre as três codificações, portanto, entre as codificações, obtive o melhor, o pior e o resultado intermediário:o melhor obtém sua pontuação positiva, o pior obtém sua pontuação negativa e o do meio obtém 0.

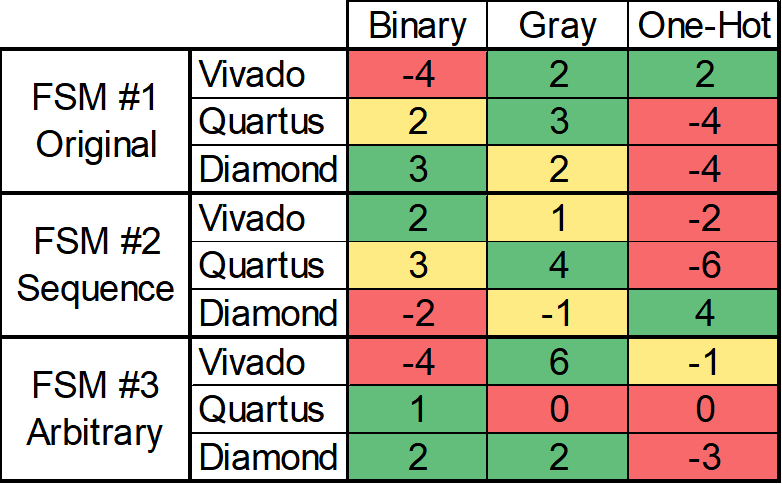

Depois de somar todas as pontuações de cada modelo, obtive os seguintes resultados:

Tabela de resultados para todas as 27 implementações. Em cada linha, a melhor codificação é mostrada em verde, a pior em vermelho e o meio em amarelo se não houver empates.

Isso parece sugerir ficar longe da codificação one-hot, com apenas dois casos em que ela vence, um dos quais é um empate. Além disso, embora eu originalmente esperasse que one-hot fosse a melhor codificação para o modelo FSM # 3, acabou sendo sua pior codificação, sem nenhuma ferramenta de desenvolvimento recomendando-a. Dito isso, há casos em que o one-hot vence o resto, principalmente nas métricas de frequência e potência.

No geral, a codificação Gray parece ser a melhor escolha para este sistema específico.

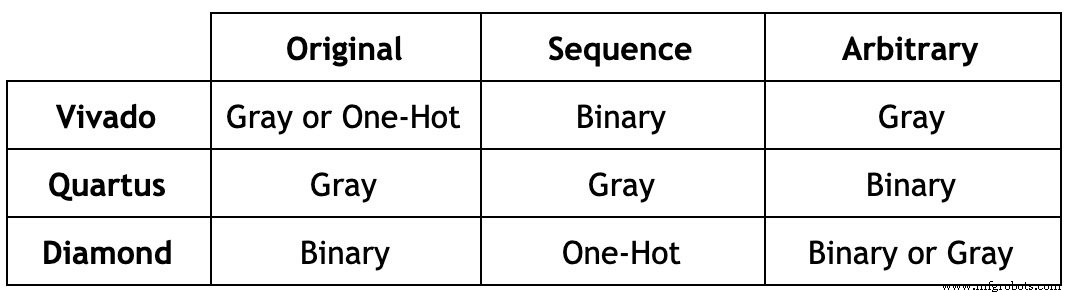

Extraindo os vencedores desta tabela, obtemos o seguinte:

O veredicto

Mesmo que essa comparação pareça favorecer a codificação Gray em vez de binária e one-hot, os resultados dependem muito das métricas que usamos, e essas métricas refletem o que é importante para nós. Por exemplo, nesta comparação, considerei a frequência e a potência mais importantes do que o uso (o número de elementos lógicos e registros no projeto). Se eu tivesse valorizado o uso sobre a frequência e a frequência sobre a potência, certamente teria resultado uma classificação diferente.

Essa comparação não pretendia ser um trabalho definitivo sobre o desempenho obtido com o uso dessas codificações. Em vez disso, mostra a classificação produzida por minhas preferências pessoais nas arquiteturas que usei.

Mais uma vez, se você quiser dar uma olhada no código, confira as 27 implementações ou veja minha simulação do Jogo da Vida de Conway em ação, confira o projeto no GitHub.

Integrado

- Swissbit:chave da unidade flash USB 3.1 para aplicações industriais

- AAEON:COM Express Type 6 para aplicativos exigentes

- Como selecionar um controlador

- Quando devo usar o teste de placa nua?

- Por que você deve usar um reator de linha

- Quando você deve usar um guindaste de cabeça de martelo? Um guia

- Quais indústrias usam materiais de Kevlar?

- Por que você deve usar uma solução Remote Expert?

- Saber qual liga de alumínio usar

- Titânio versus alumínio:qual metal não ferroso usar