Como os conversores de dados devem ser modelados para simulações do sistema?

Este artigo inicia uma série que explora a questão de como modelar conversores de dados para simulações de sistema.

Os engenheiros costumam se perguntar. Enquanto trabalham em vários projetos com cronogramas de design apertados, eles muitas vezes se perguntam sobre as perguntas para as quais gostariam de encontrar as respostas, mas não têm tempo para isso. Eles ainda se perguntam.

No decorrer de seu trabalho de engenharia, seu autor questionou várias questões relacionadas à transferência de dados de e para um sinal analógico de RF e sinais digitais I e Q. Recentemente, ele teve tempo de buscar as respostas a algumas dessas perguntas e disponibilizou todos os resultados que conseguiu obter em artigos técnicos. Um desses artigos anteriores abordou a questão de "A combinação e separação I e Q devem ser feitas digitalmente ou analógicamente?" e outro oferecido "Requisitos para o bom desempenho do link de comunicações".

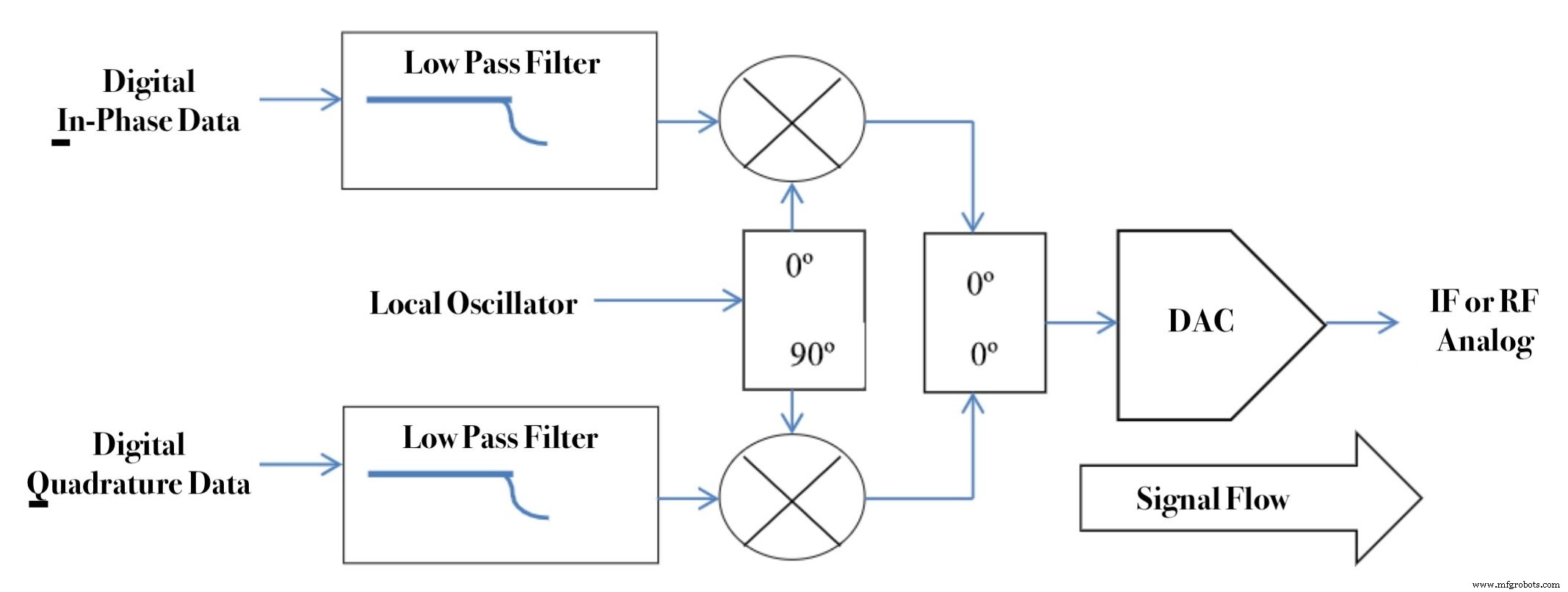

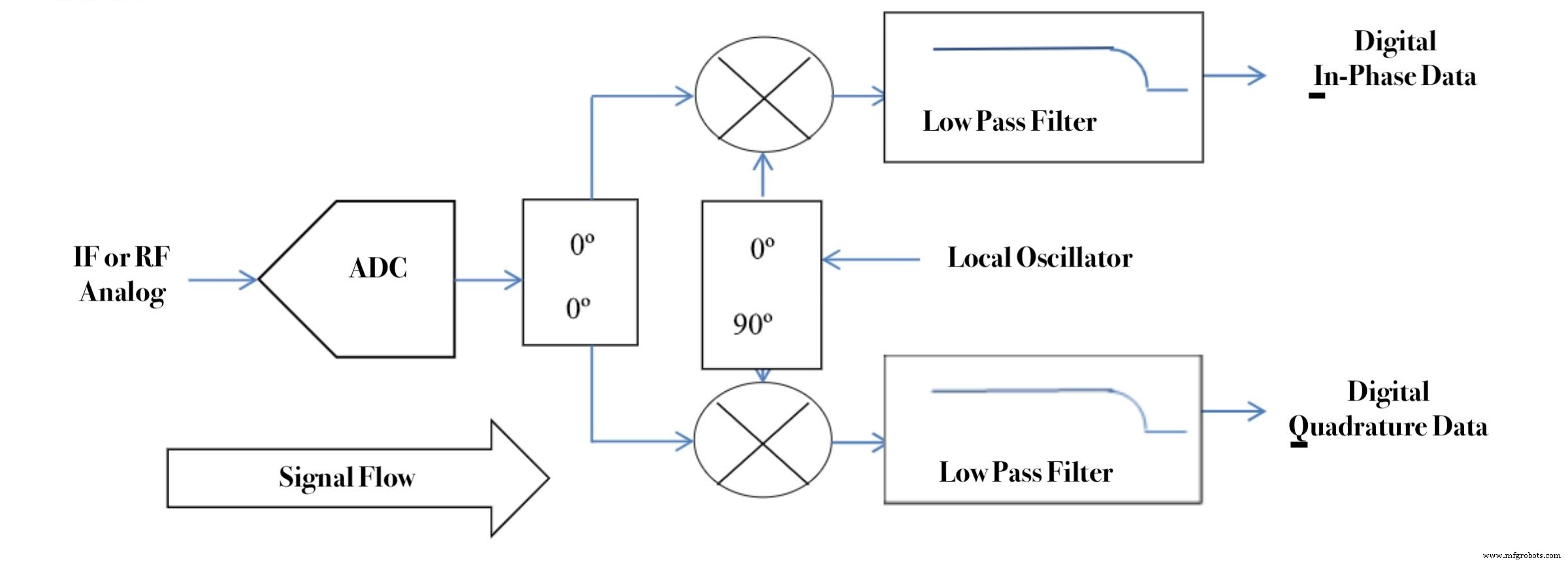

A Figura 1 daquele artigo inicial mostra a opção de conversão direta de RF digital para analógico e de RF direta de analógico para digital. (Observe que os conversores digital para analógico {DACs} e os conversores analógico para digital {ADCs} são chamados em conjunto de "conversores de dados".)

Figura 1 (a). Modulador

Figura 1 (b). Demodulador

Nesse artigo, uma coisa que seu autor questionou foi:quais são os requisitos de qualidade para o DAC e ADC na Figura 1 para um bom desempenho do link de comunicação? Não parecia haver muito publicado sobre esta questão.

Isso o levou a se perguntar, se ele fosse simular um conversor de dados em um link de comunicação, como ele deveria ser modelado?

Para simulações de taxa de erro de bit (BER), o número de erros de bit encontrados é dividido pelo número total de bits para calcular o BER. Para resultados estatisticamente significativos, deve haver várias centenas a mil erros contados. Mesmo para um BER bastante alto de 10-4; para contar 500 erros leva 5 milhões de bits. Para que a simulação seja executada em um tempo razoavelmente curto, um modelo bastante simples, que capture adequadamente todas as características relevantes do conversor de dados, deve ser encontrado.

Este artigo descreve as informações que ele encontrou. Foi útil dividir a discussão em algumas sobre ADCs e DACs. Nota adicionada na versão .02; Os conversores de dados do tipo Sigma-Delta não são considerados neste artigo.

Modelos para conversores analógico-digital (ADCs)

As referências [4] a [18] abaixo discutem análises, modelos, simulação, testes e especificações para ADCs. Em particular [13], [14], [16] e [17] apresentam modelos que modelam alguns aspectos do desempenho do ADC. Como engenheiro, seu autor questionou se um modelo mais simples e fácil de entender seria possível.

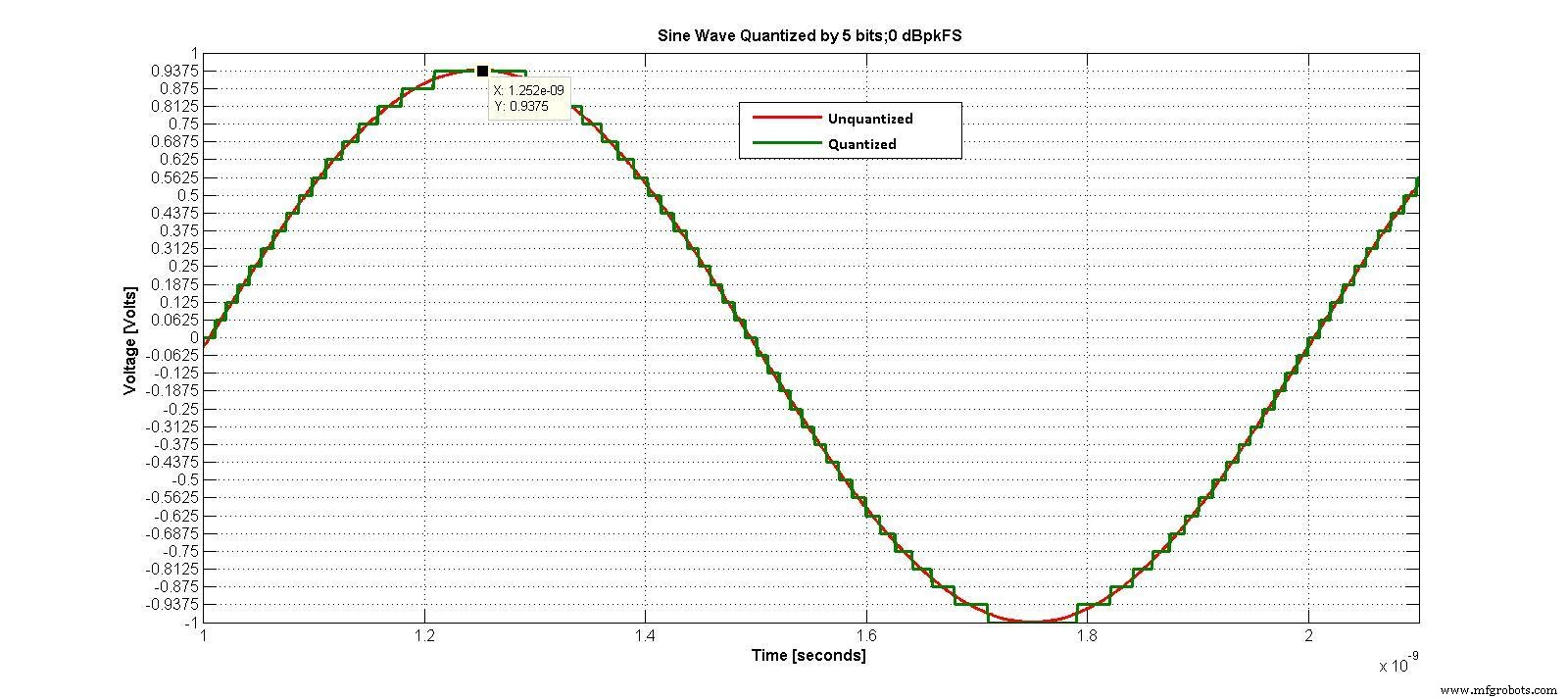

A Figura 2 mostra a quantização de um ADC de 5 bits. Existem 2 5 =32 níveis. Como a entrada pode ser positiva e negativa, isso é chamado de entrada bipolar ADC. Um aspecto disso que seu autor questionou foi a diferença entre dB em relação à escala total (FS) entre o pico e o sinal médio.

Figura 2.

A tensão de pico do sinal na Figura 2 varia entre +0,9375 Volt (FS +) e -1 Volt (FS-); que é ± 1 Volt para uma boa aproximação.

Os engenheiros de RF estão acostumados a lidar com os valores rms do sinal. O valor rms da onda senoidal é 0,707 Volts, - 3 dB em relação ao FS. Uma vez que isso confundiu seu autor no passado, ele optou por definir as unidades dBpeakFS (dB do pico de tensão do sinal em relação à escala completa) e dBrmsFS (dB do valor rms do sinal em relação à escala completa).

Outro problema diz respeito à largura de banda da saída ADC que preocupa alguém. Para as primeiras aplicações de áudio de ADCs, geralmente, as pessoas estavam preocupadas com a largura de banda total do Nyquist.

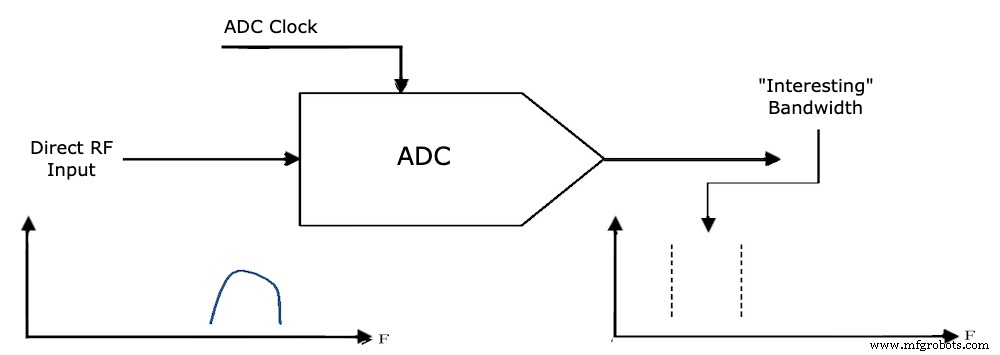

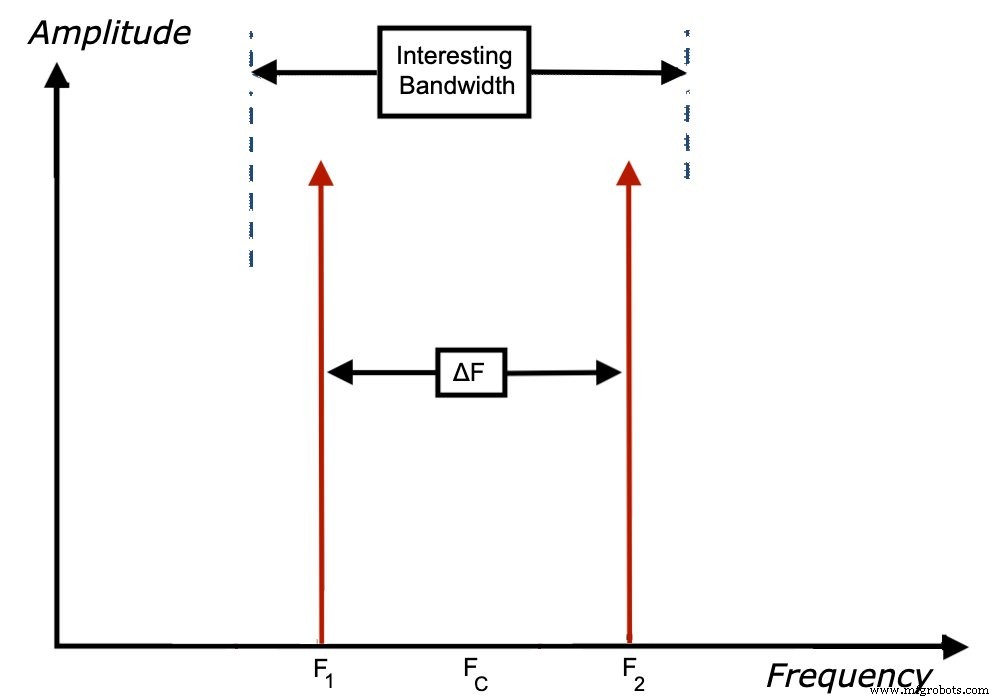

No entanto, para amostragem direta de RF, como mostrado na Figura 1 (b), apenas a parte da banda de Nyquist ocupada pelo sinal, mais um pouco para as bandas de guarda, é preocupante. Isso levou seu autor a definir a “largura de banda interessante”, conforme mostrado na Figura 3.

“Largura de banda interessante” é a largura de banda que é processada pelo processamento de sinal digital (DSP). Geralmente é a largura de banda desejada do sinal ou um pouco mais larga.

Figura 3.

Observe, na Figura 3, que embora o sinal e as larguras de banda “interessantes” sejam mostradas as mesmas, as frequências centrais dos dois não são. Isso pode ser devido à amostragem passa-banda descrita em nosso primeiro artigo, onde o relógio ADC atua como o oscilador local de um mixer. A frequência do relógio ADC será denotada por fS. A frequência de Nyquist =F Nyquist =f S / 2 .

Escolha de um sinal de entrada para implementar um modelo

Para caracterizar o ADC para criar um bom modelo, é necessário definir um sinal de entrada útil. A maioria das especificações ADC são criadas com uma única entrada de onda senoidal. No entanto, como ele tem largura de banda de 0 Hz e nenhuma variação de envelope, não parecia um sinal muito bom. Uma entrada de 2 tons, mostrada na Figura 4, tem mais de 0 Hz de largura de banda e tem variação de amplitude. É fácil de gerar na bancada de teste usando duas fontes de sinal de alta qualidade e a combinação de potência correta. Além disso, a maioria das planilhas de dados contém algumas informações sobre o desempenho do dispositivo com uma entrada de 2 tons.

Figura 4.

Um sinal de teste de dois tons também foi proposto em [4] e [12]. Outros sinais de teste que foram propostos incluem uma entrada gaussiana com um formato de espectro arbitrário [17] e sinais AM ou FM [5]. Normalmente, eles requerem geradores de sinal menos comuns e não são geralmente mostrados nas planilhas de dados como entradas para testes.

No próximo artigo, discutiremos um modelo ADC usando um número efetivo de bits (ENOB).

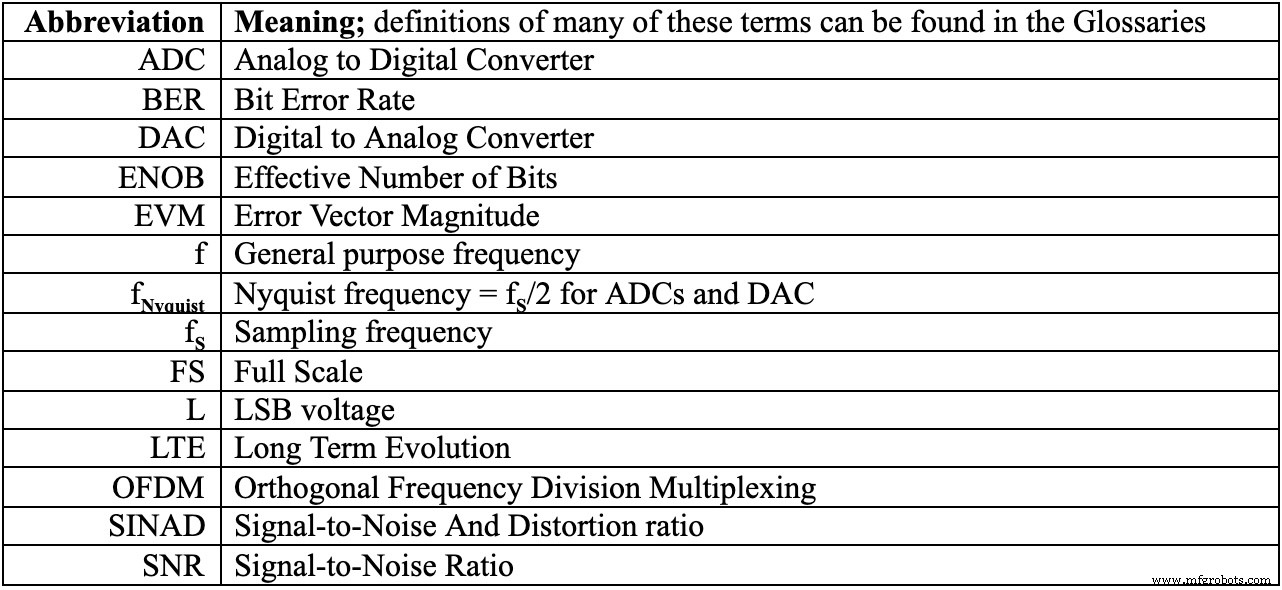

Para o restante desta série, consulte a seguinte tabela de abreviações, glossários e referências.

Abreviações usadas

Glossários

Munson, Justin; "Compreendendo o teste e avaliação de DAC de alta velocidade"; Analog Devices Application Note AN-928; 2013

Arrants, Alex; Brannon, Brad; &Reeder, Rob; "Understanding High Speed ADC Testing and Evaluation ''; Analog Devices Application Note AN-835; 2010

Baker, Bonnie; "Um Glossário de Especificações Analógico-Digital e Características de Desempenho"; Relatório de aplicação SBAA147B da Texas Instruments; 2011

Malobert, Franco; Conversores de dados; Springer Publishing; Capítulos 2:“Especificações do conversor de dados”; e 9:“Teste de conversores D / A e A / D”

Myderrizi, I; Zeki, A, "Current-Steering Digital-to-Analog Converters:Functional Specific, Design Basics, and Behavioral Modeling," Antennas and Propagation Magazine, IEEE, vol.52, no.4, pp.197.208, ago. 2010; Seção 3. "Especificações funcionais para caracterização de desempenho de um DAC"

Referências

Informações gerais

[1] Brodsky, Wesley; “A combinação e separação de I e Q devem ser feitas digitalmente ou analógicamente?”; White Paper da comunicação sem fio WesBrodsky:WBWC.01; 2014

[2] Maloberti, Franco; Conversores de dados; Springer Publishing; 2007

[3] VanTrees, Harry L; Teoria de detecção, estimativa e modulação, Parte III, Processamento de sinal de radar / sonar e sinais gaussianos no ruído; John Wiley and Sons; 1971. Apêndice:"Representação complexa de sinais, sistemas e processos de passagem de banda"

Análise, modelos, simulação, testes e especificações de ADC

[4] Seokjin Kim; Elkis, R .; Peckerar, Martin, "Teste de Verificação de Dispositivo de Conversores Analógico-Digital de Alta Velocidade em Sistemas de Comunicação por Satélite," Instrumentation and Measurement, IEEE Transactions on, vol.58, no.2, pp.270.280, Fev. 2009

[5] Vedral, J .; Fexa, P .; Svatos, J., "Using of AM and FM signal for ADC testing," Instrumentation and Measurement Technology Conference (I2MTC), 2010 IEEE, vol., No., Pp.508.511, 3-6 de maio de 2010

[6] Kester, Walt; "Os aspectos bons, ruins e feios do ruído de entrada do ADC - O ruído é bom, é ruído?"; Tutorial de dispositivos analógicos MT-004; 2008

[7] Arrants, Alex; Brannon, Brad; Reeder, Rob; "Compreendendo o teste e avaliação de ADC de alta velocidade"; Analog Devices Application Note AN-835; 2010

[8] Kester, Walt; "Entenda SINAD, ENOB, SNR, THD, THD + N e SFDR para que você não se perca no piso de ruído"; Tutorial de dispositivos analógicos MT-003; 2008

[9] Shinagawa, M .; Akazawa, Yukio; Wakimoto, Tsutomu, "Jitter analysis of high-speed sampling systems," Solid-State Circuits, IEEE Journal of, vol.25, no.1, pp.220.224, fev 1990

[10] Hummels, D.M .; Irons, F.H .; Cook, R .; Papantonopoulos, I, "Characterization of ADCs using a non-iterative procedure," Circuits and Systems, 1994. ISCAS '94., 1994 IEEE International Symposium on, vol.2, no., Pp.5,8 vol.2, 30 Maio-2 junho 1994

[11] de Mateo Garcia, J.C .; Armada, AG., "Effects of bandpass sigma-delta modulation on OFDM signs," Consumer Electronics, IEEE Transactions on, vol.45, no.2, pp.318.326, maio de 1999

[12] Abuelma'atti, Muhammad Taher, "Effect of Nonmonotonicity on the Intermodulation Performance of A / D Converters", Communications, IEEE Transactions on, vol.33, no.8, pp.839.843, agosto de 1985

[13] Traverso, P.A; Mirri, D .; Pasini, G .; Filicori, F., "Um modelo de dispositivo S / H-ADC dinâmico não linear baseado em uma série de Volterra modificada:procedimento de identificação e implementação de ferramenta CAD comercial," Instrumentação e Medição, IEEE Transactions on, vol.52, no.4, pp. 1129,1135, agosto de 2003

[14] Fraz, H .; Bjorsell, N .; Kenney, J.S .; Sperlich, R., "Prediction of Harmonic Distortion in ADCs using dynamic Integral Non-Linearity model", Behavioral Modeling and Simulation Workshop, 2009. BMAS 2009. IEEE, pp.102,107, 17-18 de setembro de 2009

[15] Kester, Walt; "Figura de ruído ADC - uma especificação frequentemente mal compreendida e mal interpretada"; Tutorial de dispositivos analógicos MT-006; 2014

[16] Brannon, Brad; MacLeod, Tom; "Como o ADIsimADC modela um ADC"; Analog Devices Application Note AN-737; 2009

[17] Dardari, D., "Joint clip and quantization effects characterization in OFDM receivers," Circuits and Systems I:Regular Papers, IEEE Transactions on, vol.53, no.8, pp.1741,1748, ago. 2006

[18] Lavrador, Pedro Miguel; de Carvalho, N.B .; Pedro, Jose Carlos, "Evaluation of signal-to-noise e distorção ratio degradation in nonlinear systems," Microwave Theory and Techniques, IEEE Transactions on, vol.52, no.3, pp.813.822, March 2004

[18A] Gray, Robert M .; “Espectros de ruído de quantização”; Teoria da Informação, IEEE Transactions on; Vol. 36, No. 6; Novembro de 1990; páginas 1220 a 1244.

Análise, modelos, simulação, testes e especificações DAC

[19] Wikner, J.J .; Nianxiang Tan, "Modeling of CMOS digital-to-analog converters for telecommunication," Circuits and Systems II:Analog and Digital Signal Processing, IEEE Transactions on, vol.46, no.5, pp.489.499, May 1999

[20] Angrisani, L .; D'Arco, M., "Modeling Timing Jitter Effects in Digital-to-Analog Converters," Instrumentation and Measurement, IEEE Transactions on, vol.58, no.2, pp.330.336, fev. 2009

[21] D'Apuzzo, M .; D'Arco, M .; Liccardo, A; Vadursi, M., "Modeling DAC Output Waveforms," Instrumentation and Measurement, IEEE Transactions on, vol.59, no.11, pp.2854,2862, Nov. 2010

[22] Myderrizi, I; Zeki, A, "Current-Steering Digital-to-Analog Converters:Functional Specifications, Design Basics, and Behavioral Modeling," Antennas and Propagation Magazine, IEEE, vol.52, no.4, pp.197.208, ago. 2010

[23] Sang Min Lee; Taleie, S.M .; Saripalli, G.R .; Dongwon Seo, "Clock-Phase-Noise-Induced TX Leakage Estimation of a Baseband Wireless Transmitter DAC," Circuits and Systems II:Express Briefs, IEEE Transactions on, vol.59, no.5, pp.277.281, maio de 2012

[24] Naoues, M .; Morche, D .; Dehos, C .; Barrak, R .; Ghazel, A, "Nova técnica de modelagem comportamental DAC para especificação de sistema WirelessHD", Eletrônica, Circuitos e Sistemas, 2009. ICECS 2009. 16ª Conferência Internacional IEEE em, vol., No., Pp.543.546, 13-16 de dezembro de 2009

[25] Kitaek Bae; Changyong Shin; Powers, E.J., "Performance Analysis of OFDM Systems with Selected Mapping in the Presence of Nonlinearity," Wireless Communications, IEEE Transactions on, vol.12, no.5, pp.2314,2322, maio de 2013

[26] Ling, W.A, "Shaping Quantization Noise and Clipping Distortion in Direct-Detection Discrete Multitone," Lightwave Technology, Journal of, vol.32, no.9, pp.1750,1758, 01 de maio de 2014

[27] Engel, G .; Fague, D.E .; Toledano, A, "Conversores RF digital-analógico permitem síntese direta de sinais de comunicação," Communications Magazine, IEEE, vol.50, no.10, pp.108.116, outubro de 2012

[28] Pearson, Chris; "Fundamentos de conversores de digital para analógico de alta velocidade"; Relatório de aplicação SLAA523A da Texas Instruments; 2012

[29] Munson, Justin; "Compreendendo o teste e avaliação de DAC de alta velocidade"; Analog Devices Application Note AN-928; 2013

Tecnologia da Internet das Coisas

- Como definir a estratégia de dados para um mundo com várias nuvens

- Estacionamento inteligente:como municípios e empreendedores devem se preparar para o lançamento de um aplicativo para toda a cidade

- Como você se prepara para IA usando IoT

- Como as empresas podem aproveitar a IoT para coleta e análise de dados em larga escala

- Seu sistema está pronto para a IoT?

- Como um sistema de monitoramento de ambiente baseado em IoT é benéfico para o setor de saúde?

- Como a IoT capacita o sistema de rastreamento de veículos?

- Por que você deve adotar um sistema de monitoramento de nível sem fio para grandes tanques de armazenamento?

- Entrada externa para valores programados

- Como planejar e investir em um novo sistema CAD/CAM