Níveis de tensão do sinal lógico

Tensões de entrada para portas lógicas

Os circuitos de porta lógica são projetados para entrada e saída de apenas dois tipos de sinais:"alto" (1) e "baixo" (0), conforme representado por uma tensão variável:tensão de alimentação total para um estado "alto" e tensão zero para um estado “baixo”. Em um mundo perfeito, todos os sinais de circuito lógico existiriam nesses limites extremos de tensão e nunca se desviariam deles (ou seja, menos do que a tensão total para um "alto" ou mais do que zero para um "baixo").

No entanto, na realidade, os níveis de tensão do sinal lógico raramente atingem esses limites perfeitos devido a quedas de tensão parasitas nos circuitos do transistor, e por isso devemos entender as limitações do nível do sinal dos circuitos de porta conforme eles tentam interpretar as tensões do sinal em algum lugar entre tensão de alimentação total e zero.

Tolerância de tensão de entradas de porta TTL

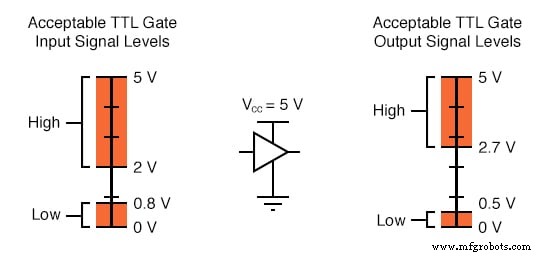

As portas TTL operam com uma tensão de alimentação nominal de 5 volts, +/- 0,25 volts. Idealmente, um sinal TTL “alto” seria exatamente de 5,00 volts e um sinal TTL “baixo” de 0,00 volts exatamente.

No entanto, os circuitos de porta TTL reais não podem produzir esses níveis de tensão perfeitos e são projetados para aceitar sinais "altos" e "baixos" que se desviam substancialmente desses valores ideais.

As tensões de sinal de entrada “aceitáveis” variam de 0 volts a 0,8 volts para um estado lógico “baixo” e de 2 volts a 5 volts para um estado lógico “alto”.

As tensões de sinal de saída "aceitáveis" (níveis de tensão garantidos pelo fabricante da porta em uma faixa especificada de condições de carga) variam de 0 volts a 0,5 volts para um estado lógico "baixo" e 2,7 volts a 5 volts para um estado lógico "alto" :

Se um sinal de tensão variando entre 0,8 volts e 2 volts fosse enviado para a entrada de uma porta TTL, não haveria resposta certa da porta. Tal sinal seria considerado incerto , e nenhum fabricante de porta lógica garantiria como seu circuito de porta interpretaria tal sinal.

Margem de ruído TTL

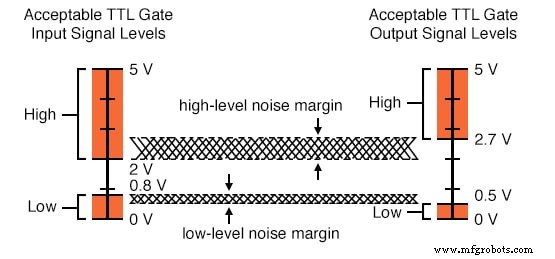

Como você pode ver, as faixas toleráveis para níveis de sinal de saída são mais estreitas do que para níveis de sinal de entrada, para garantir que qualquer porta TTL que produza um sinal digital na entrada de outra porta TTL transmita tensões aceitáveis para a porta de recepção. A diferença entre os intervalos de saída e entrada toleráveis é chamada de margem de ruído do portão.

Para portas TTL, a margem de ruído de baixo nível é a diferença entre 0,8 volts e 0,5 volts (0,3 volts), enquanto a margem de ruído de alto nível é a diferença entre 2,7 volts e 2 volts (0,7 volts). Simplificando, a margem de ruído é a quantidade de pico de tensão espúria ou "ruído" que pode ser sobreposta a um sinal de tensão de saída de porta fraca antes que a porta de recepção possa interpretá-lo incorretamente:

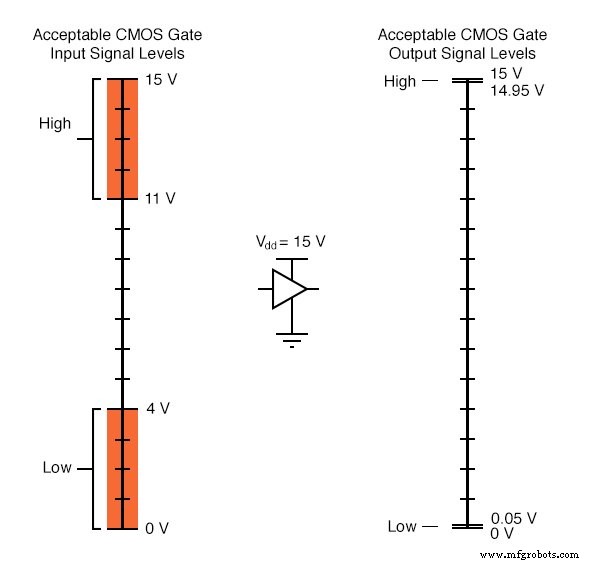

Tolerância de tensão de entradas de porta CMOS

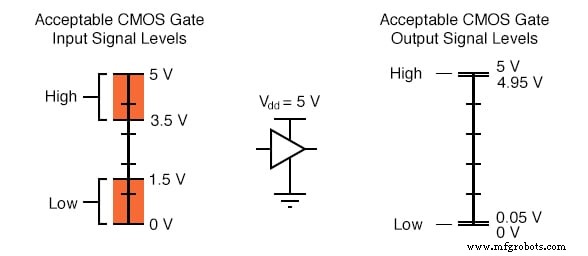

Os circuitos de porta CMOS têm especificações de sinal de entrada e saída que são bastante diferentes do TTL. Para uma porta CMOS operando em uma tensão de fonte de alimentação de 5 volts, as tensões de sinal de entrada aceitáveis variam de 0 volts a 1,5 volts para um estado lógico “baixo” e 3,5 volts a 5 volts para um estado lógico “alto”.

As tensões de sinal de saída "aceitáveis" (níveis de tensão garantidos pelo fabricante da porta em uma faixa especificada de condições de carga) variam de 0 volts a 0,05 volts para um estado lógico "baixo" e 4,95 volts a 5 volts para um estado lógico "alto" :

Margem de ruído CMOS

Deve ser óbvio a partir dessas figuras que os circuitos de porta CMOS têm margens de ruído muito maiores do que TTL:1,45 volts para margens CMOS de nível baixo e alto nível, contra um máximo de 0,7 volts para TTL. Em outras palavras, os circuitos CMOS podem tolerar mais de duas vezes a quantidade de tensão de “ruído” sobreposta em suas linhas de entrada antes que ocorram erros de interpretação de sinal.

Margens de ruído em tensões operacionais mais altas

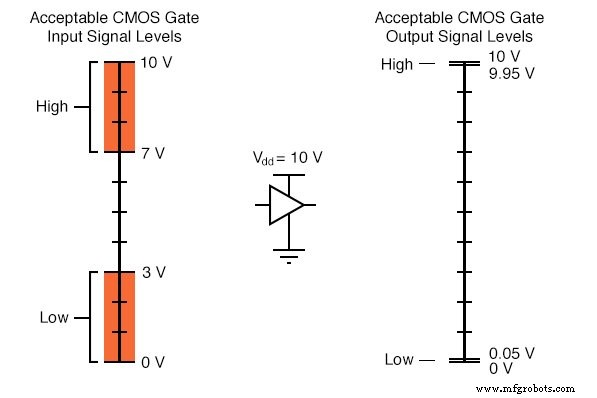

As margens de ruído do CMOS aumentam ainda mais com tensões operacionais mais altas. Ao contrário do TTL, que é restrito a uma tensão de fonte de alimentação de 5 volts, o CMOS pode ser alimentado por tensões de até 15 volts (alguns circuitos CMOS de até 18 volts).

Aqui são mostrados os estados aceitáveis de "alto" e "baixo", tanto para entrada quanto para saída, dos circuitos integrados CMOS operando em 10 volts e 15 volts, respectivamente:

As margens para sinais aceitáveis de “alto” e “baixo” podem ser maiores do que o mostrado nas ilustrações anteriores. O que é mostrado representa o desempenho do sinal de entrada de "pior caso", com base nas especificações do fabricante. Na prática, pode ser descoberto que um circuito de porta tolerará sinais “altos” de tensão consideravelmente menor e sinais “baixos” de tensão consideravelmente maior do que os especificados aqui.

Por outro lado, as margens de saída extremamente pequenas mostradas - garantindo estados de saída para sinais “alto” e “baixo” dentro de 0,05 volts dos “trilhos” da fonte de alimentação - são otimistas. Esses níveis de tensão de saída “sólidos” serão verdadeiros apenas para condições de carga mínima. Se a porta está fornecendo ou absorvendo corrente substancial para uma carga, a tensão de saída não será capaz de manter esses níveis ideais, devido à resistência do canal interno dos MOSFETs de saída final da porta.

Limites de tensão

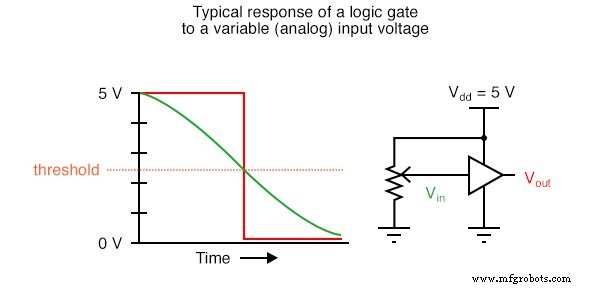

Dentro da faixa "incerta" para qualquer entrada de porta, haverá algum ponto de demarcação dividindo a faixa de sinal de entrada "baixa" real da porta de sua faixa de sinal de entrada "alta" real. Ou seja, em algum lugar entre o nível de tensão de sinal “alto” mais baixo e o nível de tensão de sinal “baixo” mais alto garantido pelo fabricante da porta, há um limite de tensão na qual a porta irá na verdade mude sua interpretação de um sinal de “baixo” ou “alto” ou vice-versa. Para a maioria dos circuitos de porta, esta tensão não especificada é um único ponto:

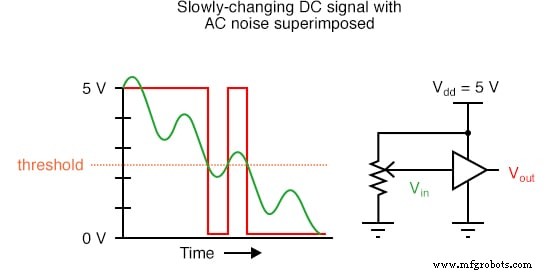

Entradas com ruído AC

Na presença de tensão de "ruído" CA sobreposta no sinal de entrada CC, um único ponto de limite no qual a porta altera sua interpretação do nível lógico resultará em uma saída errática:

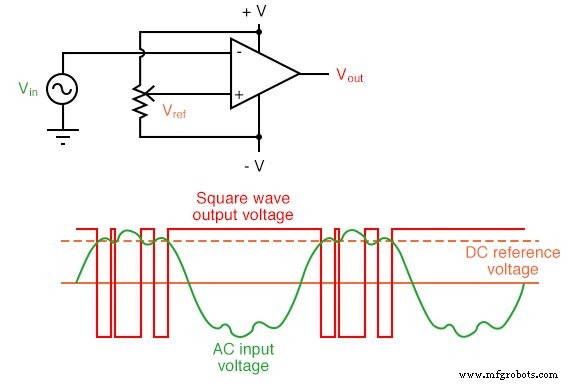

Se este cenário lhe parecer familiar, é porque você se lembra de um problema semelhante com circuitos de amplificadores operacionais de comparador de tensão (analógico). Com um único ponto de limite no qual uma entrada faz com que a saída alterne entre os estados "alto" e "baixo", a presença de ruído significativo causará mudanças erráticas na saída:

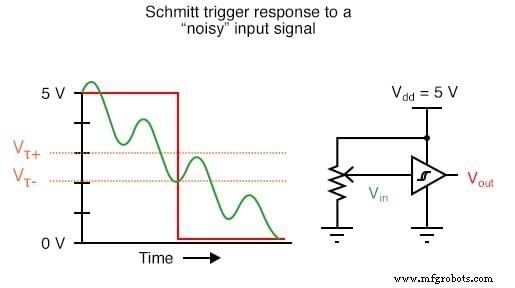

Schmittt Trigger

A solução para este problema é um pouco positiva feedback introduzido no circuito do amplificador. Com um amplificador operacional, isso é feito conectando a saída de volta à entrada não inversora (+) por meio de um resistor.

Em um circuito de porta, isso envolve redesenhar o circuito de porta interno, estabelecendo o feedback dentro do pacote de porta em vez de por meio de conexões externas. Um portão assim projetado é chamado de gatilho Schmitt . Os gatilhos Schmitt interpretam tensões de entrada variáveis de acordo com dois tensões de limiar:um andamento positivo limiar (VT +), e um andamento negativo limite (VT-):

Histerese em Schmitt Trigger Gates

As portas de disparo Schmitt são distinguidas em diagramas esquemáticos pelo pequeno símbolo de “histerese” desenhado dentro delas, uma reminiscência da curva B-H para um material ferromagnético. A histerese gerada pelo feedback positivo dentro dos circuitos do portão adiciona um nível adicional de imunidade a ruído ao desempenho do portão.

As portas de disparo Schmitt são frequentemente usadas em aplicações onde se espera ruído na (s) linha (s) de sinal de entrada e / ou onde uma saída irregular seria muito prejudicial ao desempenho do sistema.

Usando tecnologias TTL e CMOS no mesmo sistema

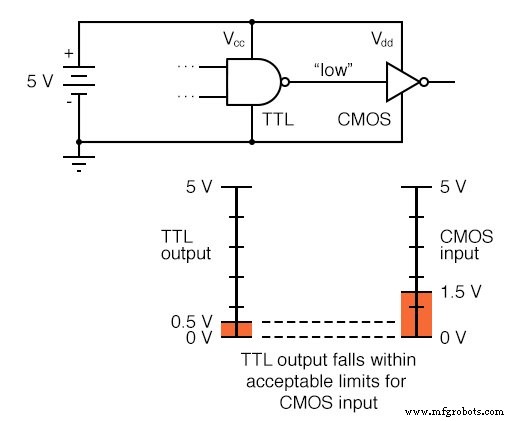

Os diferentes requisitos de nível de tensão da tecnologia TTL e CMOS apresentam problemas quando os dois tipos de portas são usados no mesmo sistema. Embora operar portas CMOS na mesma tensão de alimentação de 5,00 volts exigida pelas portas TTL não seja problema, os níveis de tensão de saída TTL não serão compatíveis com os requisitos de tensão de entrada CMOS.

Amostra de circuito de combinação TTL e CMOS

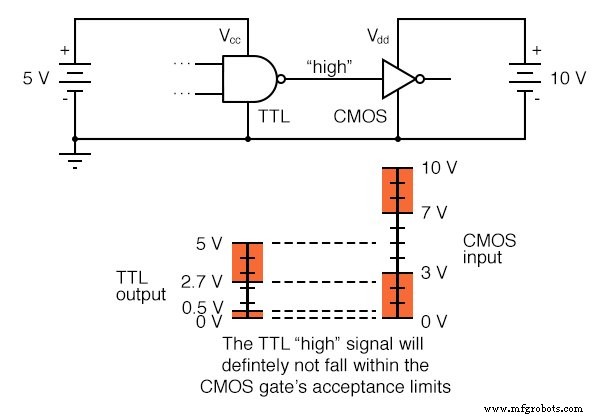

Considere, por exemplo, uma porta TTL NAND que produz um sinal na entrada de uma porta do inversor CMOS. Ambas as portas são alimentadas pela mesma fonte de 5,00 volts (V cc ) Se a saída da porta TTL for um sinal "baixo" (garantido entre 0 volts e 0,5 volts), será interpretado corretamente pela entrada da porta CMOS como um sinal "baixo" (esperando uma tensão entre 0 volts e 1,5 volts):

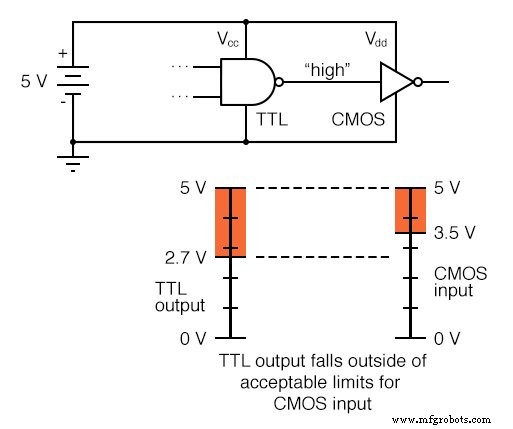

No entanto, se a saída da porta TTL for um sinal "alto" (garantido entre 5 volts e 2,7 volts), ele pode não ser interpretado corretamente pela entrada da porta CMOS como um "alto" (esperando uma tensão entre 5 volts e 3,5 volts):

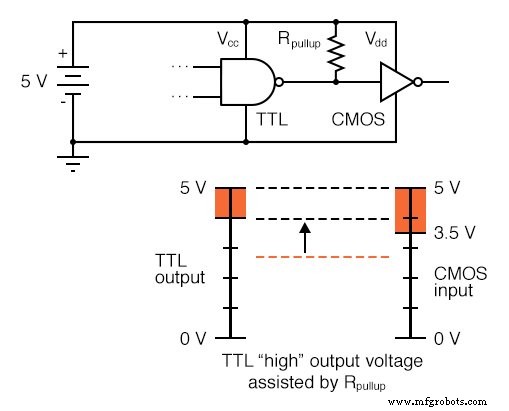

Dada essa incompatibilidade, é inteiramente possível para a porta TTL emitir um sinal "alto" válido (válido, isto é, de acordo com os padrões para TTL) que se encontra dentro da faixa "incerta" para a entrada CMOS, e pode ser ( falsamente) interpretado como um “baixo” pela porta de recepção. Uma "correção" fácil para este problema é aumentar o nível de tensão do sinal "alto" da porta TTL por meio de um resistor pullup:

Porém, algo mais do que isso é necessário para fazer a interface de uma saída TTL com uma entrada CMOS, se a porta CMOS receptora for alimentada por uma tensão de alimentação maior:

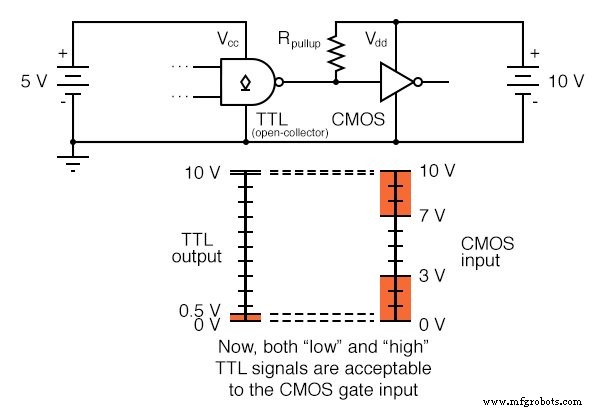

Usando uma porta TTL de coletor aberto com uma porta CMOS

Não haverá nenhum problema com a porta CMOS interpretando a saída "baixa" da porta TTL, é claro, mas um sinal "alto" da porta TTL é outra questão completamente. A faixa de tensão de saída garantida de 2,7 volts a 5 volts da saída da porta TTL está longe da faixa aceitável da porta CMOS de 7 volts a 10 volts para um sinal "alto".

Se usarmos um coletor aberto Porta TTL em vez de porta de saída de totem, porém, um resistor pullup para V de 10 volts dd o trilho de alimentação aumentará a tensão de saída "alta" da porta TTL para a tensão de alimentação total que fornece a porta CMOS. Uma vez que uma porta de coletor aberto pode apenas absorver a corrente, não a corrente da fonte, o nível de tensão de estado "alto" é inteiramente determinado pela fonte de alimentação à qual o resistor pullup está conectado, resolvendo assim perfeitamente o problema de incompatibilidade:

Problemas de uso de saída CMOS para uma entrada TTL

Devido às excelentes características de tensão de saída das portas CMOS, normalmente não há problema para conectar uma saída CMOS a uma entrada TTL. O único problema significativo é a carga de corrente apresentada pelas entradas TTL, uma vez que a saída CMOS deve absorver a corrente para cada uma das entradas TTL enquanto estiver no estado “baixo”.

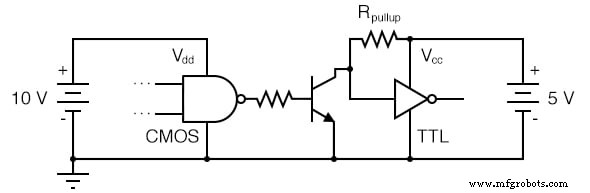

Quando a porta CMOS em questão é alimentada por uma fonte de tensão superior a 5 volts (V cc ), no entanto, isso resultará em um problema. O estado de saída "alto" da porta CMOS, sendo maior do que 5 volts, excederá os limites de entrada aceitáveis da porta TTL para um sinal "alto".

Usando Circuito Inversor de Coletor Aberto

Uma solução para este problema é criar um circuito inversor de "coletor aberto" usando um transistor NPN discreto e usá-lo para conectar as duas portas:

O “R pullup O resistor é opcional, uma vez que as entradas TTL assumem automaticamente um estado “alto” quando deixadas flutuando, que é o que acontecerá quando a saída da porta CMOS estiver “baixa” e o transistor for desligado. Claro, uma consequência muito importante da implementação desta solução é a inversão lógica criada pelo transistor:quando a porta CMOS emite um sinal “baixo”, a porta TTL vê uma entrada “alta”; e quando a porta CMOS emite um sinal “alto”, o transistor satura e a porta TTL vê uma entrada “baixa”. Enquanto essa inversão for considerada no esquema lógico do sistema, tudo ficará bem.

PLANILHA RELACIONADA:

-

Planilha de sinais de lógica digital

Tecnologia industrial