Registradores de deslocamento:Serial-in, Serial-out

O deslocamento de entrada e saída serial registra os dados de atraso por um relógio para cada estágio.

Eles irão armazenar um pouco de dados para cada registro. Um registro de deslocamento de entrada e saída serial pode ter um a 64 bits de comprimento, mais se os registros ou pacotes estiverem em cascata.

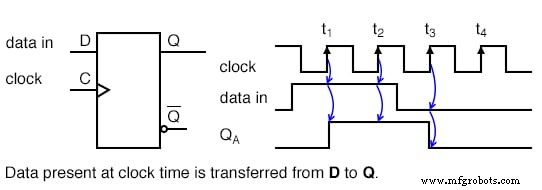

Abaixo está um registro de deslocamento de estágio único recebendo dados que não estão sincronizados com o relógio do registro.

Os “dados em” no D pino do tipo D FF (Flip-Flop) não muda os níveis quando o relógio muda de baixo para alto.

Podemos querer sincronizar os dados para um relógio de todo o sistema em uma placa de circuito para melhorar a confiabilidade de um circuito lógico digital.

O ponto óbvio (em comparação com a figura abaixo) ilustrado acima é que qualquer "dado em" está presente no D pino de um tipo D FF é transferido de D para a saída Q na hora do relógio.

Uma vez que nosso registrador de deslocamento de exemplo usa elementos de armazenamento sensíveis à borda positiva, a saída Q segue o D entrada quando o relógio muda de baixo para alto, conforme mostrado pelas setas para cima no diagrama acima.

Não há dúvida de qual nível lógico está presente no tempo do clock, porque os dados são estáveis bem antes e depois da transição do clock.

Isso raramente é o caso em registradores de deslocamento de vários estágios. Mas, este foi um exemplo fácil para começar. Estamos preocupados apenas com a transição positiva, de baixa a alta, do clock.

A borda descendente pode ser ignorada. É muito fácil ver Q siga D na hora do relógio acima.

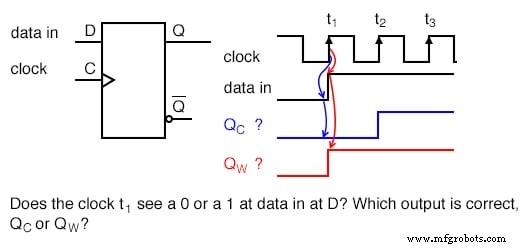

Compare isso com o diagrama abaixo, onde os “dados em” parecem mudar com a transição positiva do clock.

Uma vez que “data in” parece mudar no tempo t 1 acima, o que o tipo D FF vê na hora do relógio?

A resposta curta e supersimplificada é que ele vê os dados que estavam presentes em D antes do relógio.

Isso é o que é transferido para Q na hora do relógio t 1 . A forma de onda correta é Q C . Em t 1 Q vai para zero se ainda não for zero.

O D o registro não vê um até o tempo t 2 , momento em que Q fica alto.

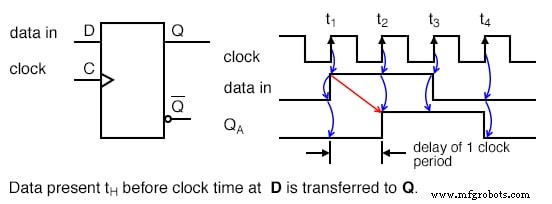

Uma vez que os dados, acima, apresentam em D é cronometrado para Q na hora do relógio e Q não pode mudar até a próxima hora, o D FF atrasa os dados em um período de clock, desde que os dados já estejam sincronizados com o clock. O Q A a forma de onda é igual a “entrada de dados” com um atraso de período de um clock.

Uma visão mais detalhada sobre o que a entrada do tipo D O Flip-Flop vê a hora do relógio a seguir.

Consulte a figura abaixo. Uma vez que “dados em” parecem mudar no horário (acima), precisamos de mais informações para determinar o que o D FF vê.

Se os “dados em” forem de outro estágio de registro de deslocamento, outro mesmo tipo D FF, podemos tirar algumas conclusões com base na folha de dados em formação.

Os fabricantes de lógica digital disponibilizam informações sobre suas peças em planilhas de dados, antes disponíveis apenas em uma coleção chamada de livro de dados .

Livros de dados ainda estão disponíveis; entretanto, o site do fabricante é a fonte moderna.

Os seguintes dados foram extraídos da folha de dados CD4006b para operação em 5V DC , que serve como um exemplo para ilustrar o tempo. [*]

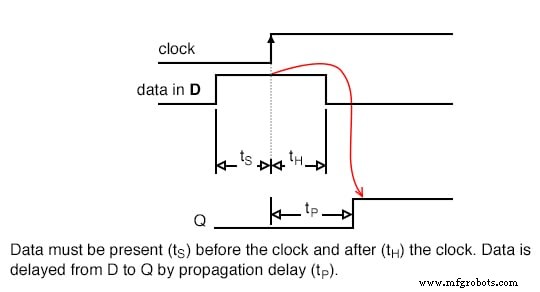

- t S =100ns

- t H =60ns

- t P =200-400 ns typ / max

t S é o tempo de configuração , os dados de hora devem estar presentes antes da hora do relógio. Nesse caso, os dados devem estar presentes em D 100ns antes do relógio.

Além disso, os dados devem ser mantidos por tempo de espera t H =60ns após a hora do relógio. Essas duas condições devem ser atendidas para dados confiáveis do relógio de D para Q do flip-flop.

Não há problema em cumprir o tempo de configuração de 60 ns como os dados em D esteve lá durante todo o período de relógio anterior se vier de outro estágio de registro de deslocamento.

Por exemplo, em uma frequência de clock de 1 Mhz, o período de clock é 1000 µs, bastante tempo.

Os dados estarão realmente presentes por 1000 µs antes do relógio, que é muito maior do que o mínimo necessário t S de 60 ns.

O tempo de espera t H =60ns é encontrado porque D conectado a Q de outro estágio não pode mudar mais rápido do que o atraso de propagação do estágio anterior t P =200ns.

O tempo de espera é atingido enquanto o atraso de propagação do D anterior FF é maior que o tempo de espera.

Dados em D conduzido por outro estágio Q não mudará mais rápido do que 200ns para o CD4006b.

Para resumir, envie Q segue a entrada D quase na hora do relógio se os flip-flops estiverem em cascata em um registrador de deslocamento de vários estágios.

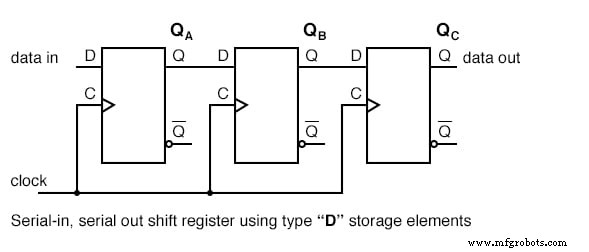

Três tipos D Os flip-flops são colocados em cascata de Q para D e os relógios paralelos para formar um registrador de deslocamento de três estágios acima.

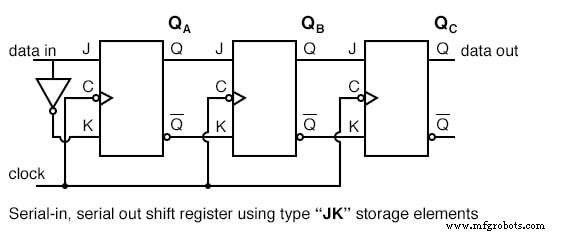

Digite JK Flip-flops cascatearam Q para J, Q 'para K com relógios em paralelo para produzir uma forma alternativa do registrador de deslocamento acima.

Um registro de deslocamento serial-in / serial-out tem uma entrada de relógio, uma entrada de dados e uma saída de dados do último estágio.

Em geral, as outras saídas de estágio não estão disponíveis. Caso contrário, seria um registro de deslocamento de entrada serial e saída paralela.

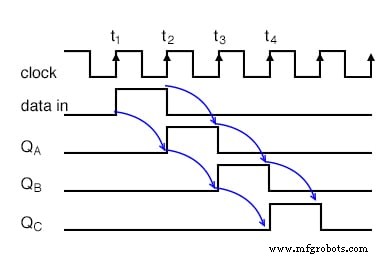

As formas de onda abaixo são aplicáveis a qualquer uma das duas versões anteriores do registro de deslocamento de entrada e saída serial.

Os três pares de setas mostram que um registrador de deslocamento de três estágios armazena temporariamente 3 bits de dados e os atrasa em três períodos de clock da entrada à saída.

Na hora do relógio t 1 um “dados em” de 0 é cronometrado de D para Q de todos os três estágios. Em particular, D do estágio A vê uma lógica 0 , que é cronometrado para Q A onde permanece até o tempo t 2 .

No horário t 2 um “dados em” de 1 é cronometrado de D para Q A . Nos estágios B e C , um 0 , alimentado a partir de estágios anteriores é cronometrado para Q B e Q C .

No tempo t 3 um “dados em” de 0 é cronometrado de D para Q A . Q A vai para baixo e permanece baixo para os relógios restantes devido a “entrada de dados” sendo 0 . Q B vai alto em t 3 devido a um 1 da etapa anterior. Q C ainda está baixo após t 3 devido a um ponto baixo do estágio anterior.

Q C finalmente vai alto no relógio t 4 devido à alta alimentação para D do estágio anterior Q B . Todos os estágios anteriores têm 0 s mudou para eles. E, após o próximo pulso de relógio em t 5 , toda lógica 1 s terá sido deslocado, substituído por 0 s

Dispositivos de entrada / saída serial

Veremos mais de perto as seguintes peças disponíveis como circuitos integrados, cortesia da Texas Instruments.

Para obter as folhas de dados completas do dispositivo, siga os links.

- CD4006b registro de deslocamento de entrada / saída serial de 18 bits

- CD4031b registro de deslocamento de entrada / saída serial de 64 bits

- CD4517b dual 64 bits serial-in / serial-out shift register

Os seguintes registros de deslocamento serial-in / serial-out são 4000 série CMOS (Complementary Metal Oxide Semiconductor) peças da família.

Como tal, eles aceitarão um V DD , fonte de alimentação positiva de 3 volts a 15 volts. The V SS pino está aterrado.

A frequência máxima do relógio de turno, que varia com V DD , é alguns megahertz.

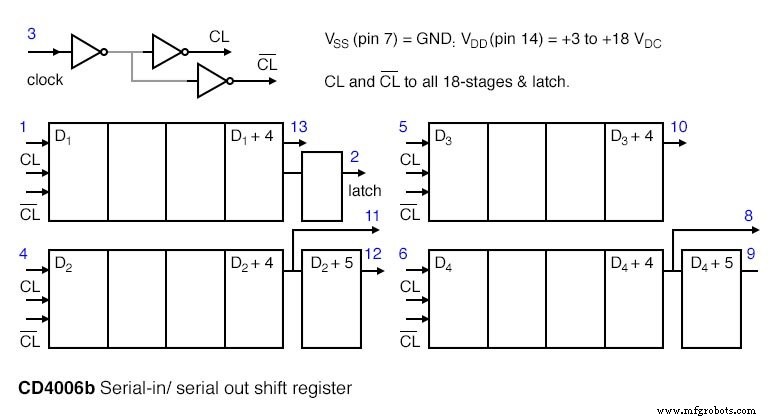

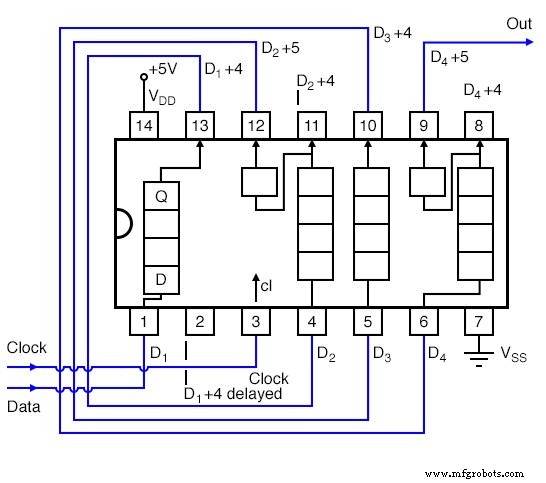

O CD4006b de 18 bits consiste em dois estágios de 4 bits e mais dois estágios de 5 bits com um tap de saída de 4 bits.

Assim, os estágios de 5 bits podem ser usados como registradores de deslocamento de 4 bits.

Para obter um registrador de deslocamento de 18 bits completo, a saída de um registrador de deslocamento deve ser cascateada para a entrada de outro e assim por diante até que todos os estágios criem um único registrador de deslocamento, conforme mostrado abaixo.

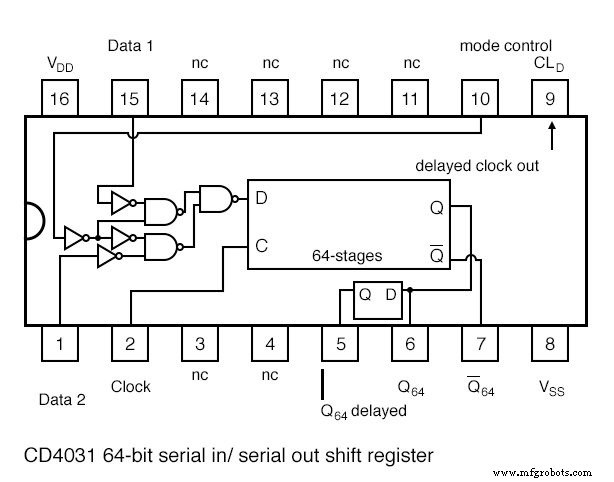

Um registro de deslocamento de entrada / saída serial CD4031 de 64 bits é mostrado abaixo.

Vários pinos não estão conectados (nc). Ambos Q e Q 'estão disponíveis a partir do 64º estágio, na verdade Q 64 e Q ’ 64 .

Também existe um Q 64 “Atrasado” de um meio estágio que é atrasado por meio ciclo de clock. Uma característica importante é um seletor de dados que está na entrada de dados para o registrador de deslocamento.

O “controle de modo” seleciona entre duas entradas:dados 1 e dados 2. Se “controle de modo” for alto, os dados serão selecionados de “dados 2” para entrada no registrador de deslocamento.

No caso de “controle de modo” ser lógico baixo, o “dado 1” é selecionado. Exemplos disso são mostrados nas duas figuras abaixo.

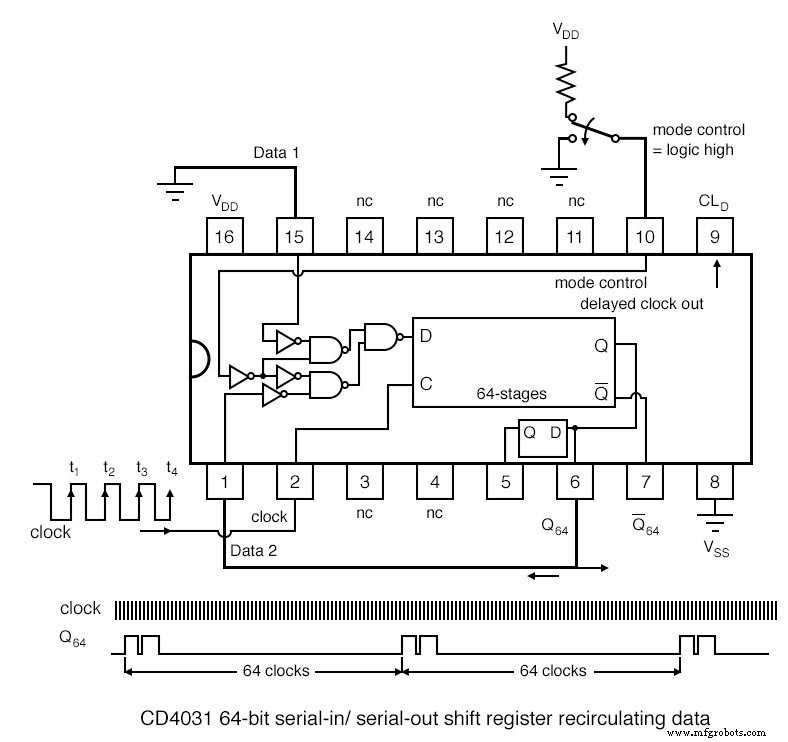

Os “dados 2” acima são conectados ao Q 64 saída do registrador de deslocamento. Com o “controle de modo” alto, o Q 64 a saída é roteada de volta para a entrada de dados do shifter D.

Os dados irão recircular da saída para a entrada. Os dados serão repetidos a cada 64 pulsos de clock, conforme mostrado acima.

A questão que surge é como esse padrão de dados entrou no registrador de deslocamento em primeiro lugar?

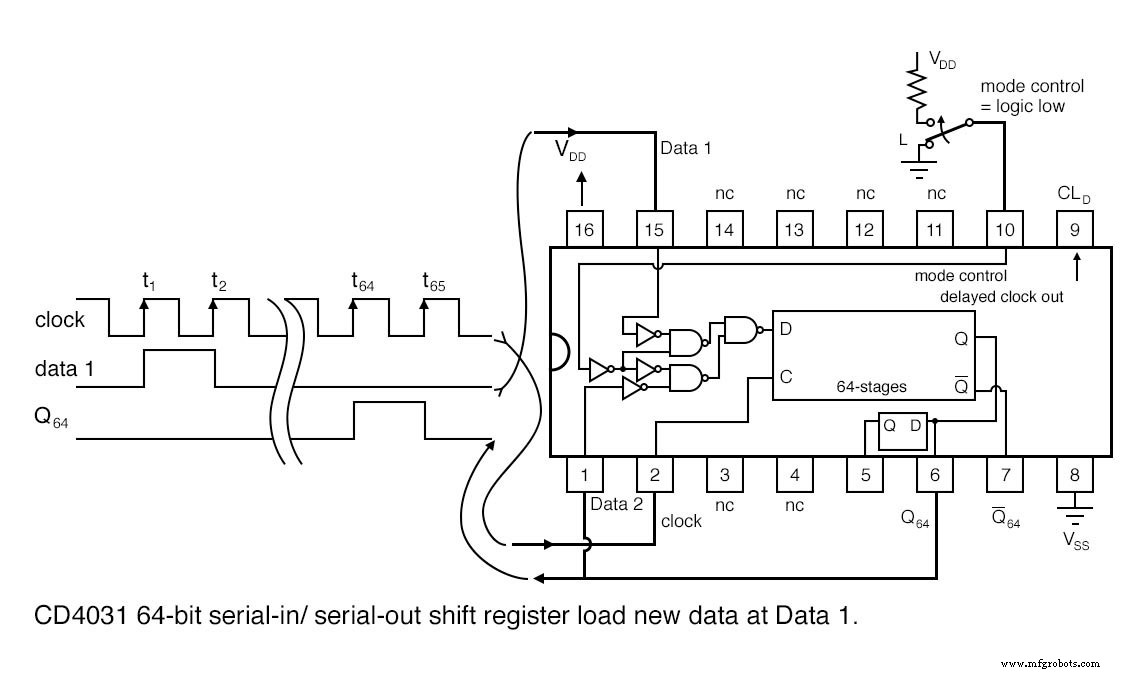

Com o “controle de modo” baixo, o CD4031 “dados 1” é selecionado para entrada no shifter.

A saída, Q 64 , não é recirculado porque a porta do seletor de dados inferior está desativada .

Por desabilitado, queremos dizer que a “seleção de modo” lógico baixo invertido duas vezes para um baixo na porta NAND inferior evita que ele passe qualquer sinal no pino inferior (dados 2) para a saída da porta.

Portanto, ele está desativado.

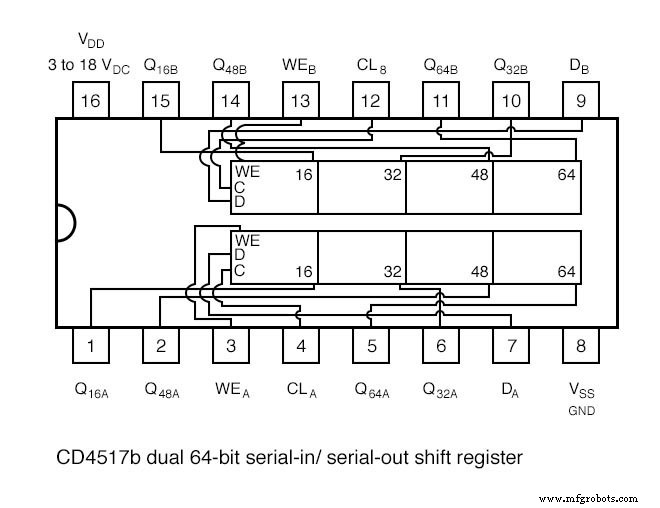

Um registro de deslocamento duplo de 64 bits CD4517b é mostrado acima. Observe as batidas nos estágios 16, 32 e 48.

Isso significa que os registradores de deslocamento desses comprimentos podem ser configurados a partir de um dos shifters de 64 bits.

Obviamente, os shifters de 64 bits podem ser colocados em cascata para produzir um registro de deslocamento de 80, 96, 112 ou 128 bits.

O relógio CL A e CL B precisa ser colocado em paralelo ao colocar os dois shifters em cascata. NÓS B e NÓS B são aterrados para operações normais de deslocamento.

As entradas de dados para os registradores de deslocamento A e B são D A e D B respectivamente.

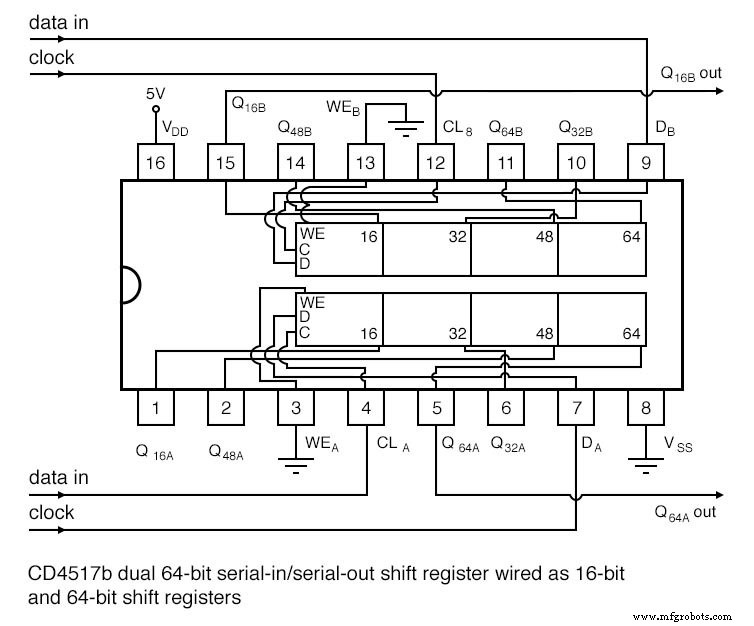

Suponha que exijamos um registrador de deslocamento de 16 bits.

Isso pode ser configurado com o CD4517b? Que tal um registrador de 64 deslocamentos da mesma peça?

Acima, mostramos um CD4517b conectado como um registrador de deslocamento de 16 bits para a seção B.

O relógio para a seção B é CL B . Os dados são sincronizados em CL B . E os dados atrasados por 16-clocks são retirados de Q 16B . NÓS B , a permissão de gravação está aterrada.

Acima, também mostramos o mesmo CD4517b conectado como um registrador de deslocamento de 64 bits para a seção independente A.

O relógio para a seção A é CL A . Os dados entram em CL A . Os dados atrasados por pulsos de 64 clock são coletados de Q 64A . NÓS A , a permissão de gravação para a seção A é aterrada.

PLANILHAS RELACIONADAS:

- Planilha de registros de turnos

Tecnologia industrial