O chip do processador em memória acelera os cálculos AI

A Imec e a GlobalFoundries demonstraram um chip de processador em memória que pode alcançar eficiência energética de até 2900 TOPS / W, aproximadamente duas ordens de magnitude acima dos atuais chips de processador em memória comerciais. O chip usa uma ideia estabelecida, computação analógica, implementada em SRAM na tecnologia de processo de silício sobre isolador totalmente empobrecido (FD-SOI) de 22 nm da GlobalFoundries. A computação in-memory analógica da Imec (AiMC) estará disponível para clientes da GlobalFoundries como um recurso que pode ser implementado na plataforma 22FDX da empresa.

O chip de teste AnIA da Imec, visto aqui montado no PCB usado para medição e caracterização, pode atingir até 2900 TOPS / W (Imagem:Imec)

Computação analógica

Computação analógica, ou processador em memória, é uma técnica estabelecida que já é usada em chips aceleradores de IA comerciais das startups Mythic, Syntiant, Gyrfalcon e outras.

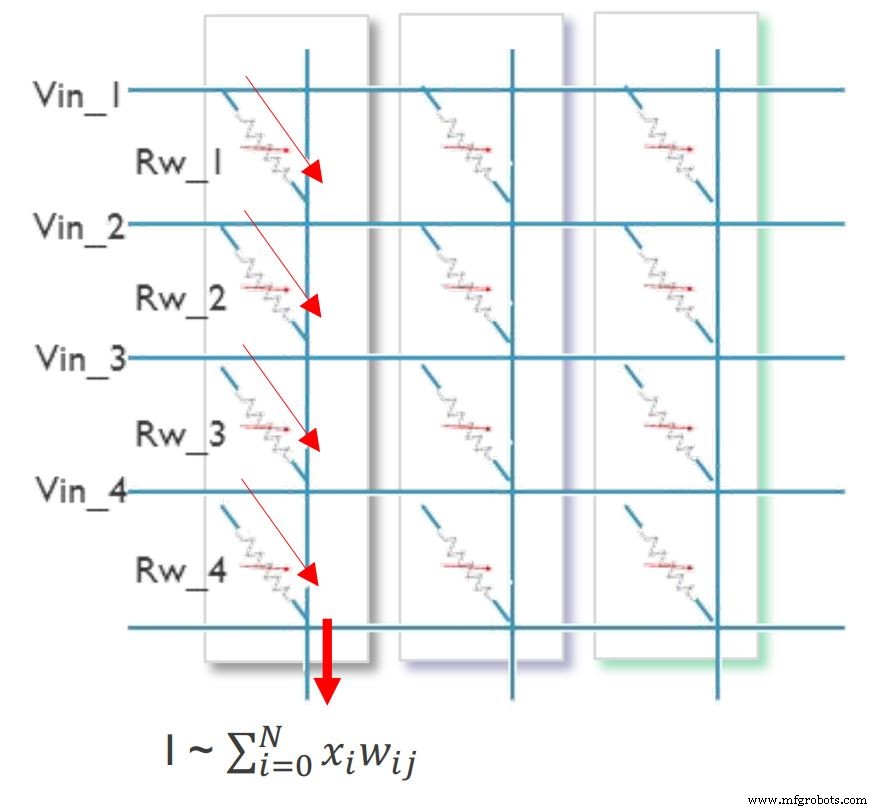

Como um modelo de rede neural pode ter dezenas ou centenas de milhões de pesos, o envio de dados para frente e para trás entre a memória e o processador é ineficiente. A computação analógica usa uma matriz de memória para armazenar os pesos e também realizar operações de multiplicação-acumulação (MAC), portanto, não há necessidade de transferência de memória para processador. Cada elemento de memristor (talvez uma célula ReRAM) tem sua condutância programada para um nível analógico que é proporcional ao peso necessário.

Aplicar uma tensão proporcional à ativação da entrada (via conversão digital para analógico - à esquerda do diagrama abaixo) significa que a corrente através de cada elemento é proporcional ao produto da ativação e do peso. A corrente através de cada linha de bits vertical (linhas verticais no diagrama abaixo) é a soma desses produtos de peso de ativação, que podem ser alimentados por meio de um conversor analógico-digital. Essa soma dos produtos de peso de ativação é crítica para o cálculo de algoritmos de rede neural.

A computação analógica usa uma matriz de células de memristor para calcular a multiplicação do vetor da matriz sem ter que enviar dados entre a memória e o processador (Imagem:Imec)

“Na prática, muitas opções são possíveis além do ReRAM - podemos usar MRAM, Flash, DRAM ... o objetivo deste programa é entender qual é o melhor para a aplicação e otimizar as opções para cada domínio de aplicação,” explicou Diederik Verkest, programa diretor de aprendizado de máquina do Imec.

Chip de teste

A Imec construiu um chip de teste, denominado acelerador de inferência analógica (AnIA), baseado no processo FD-SOI de 22 nm da GlobalFoundries. A matriz de 512k de células SRAM da AnIA mais a infraestrutura digital, incluindo 1024 DACs e 512 ADCs, ocupa 4 mm

2

. Pode realizar cerca de meio milhão

Ioannis Papistas (Imagem:Imec)

cálculos por ciclo de operação com base em ativações de entrada de 6 bits (bit de sinal positivo), pesos ternários (-1, 0, +1) e saídas de 6 bits.

“Somos capazes de produzir a saída da multiplicação do vetor da matriz em diferentes tensões de alimentação, 0,8 e 0,6 V”, disse Ioannis Papistas do grupo de aprendizado de máquina da Imec. “Operar com tensões de alimentação mais baixas sem afetar a precisão da operação pode reduzir significativamente o consumo de energia da operação, o que é especialmente importante para inferência em sistemas com restrição de energia. Esta é uma característica importante do nosso design, habilitada pelo processo 22FDX, que permite inferência competitiva no limite. ”

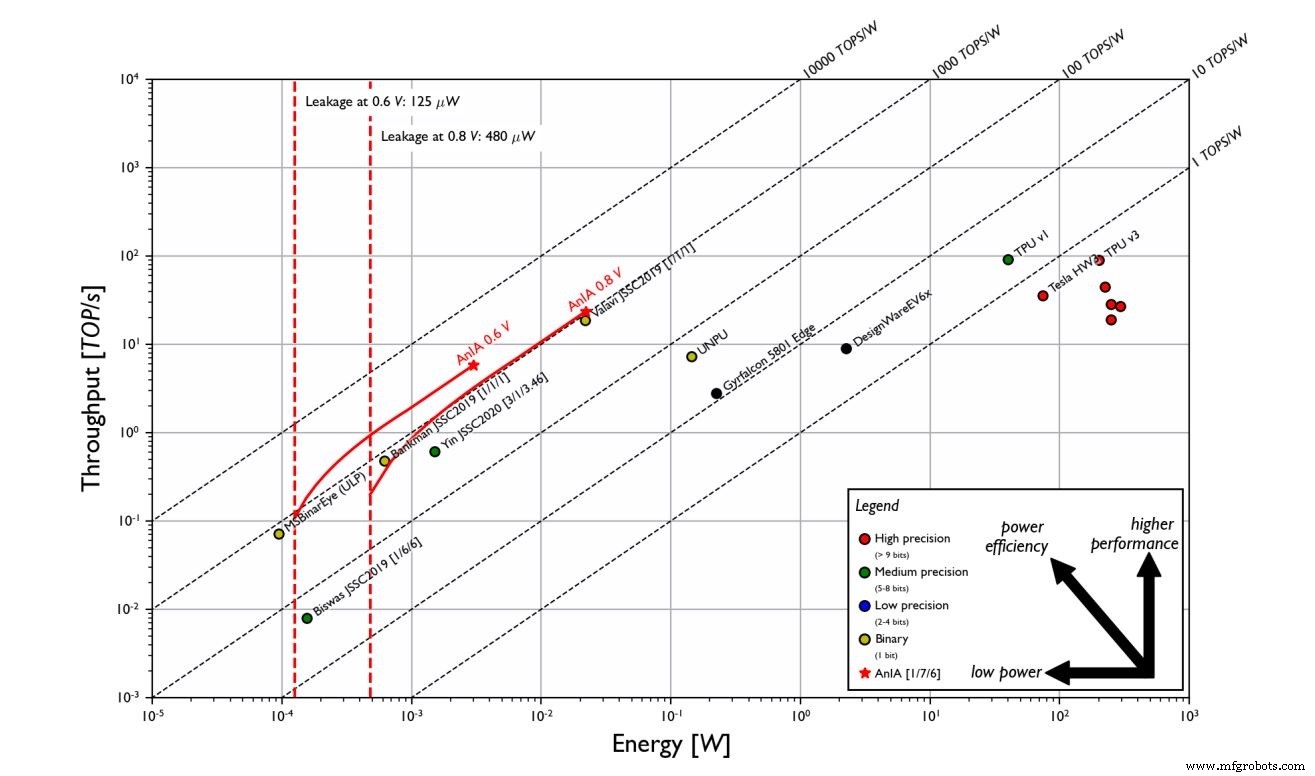

Imec mostrou resultados de precisão para inferência de reconhecimento de objeto no conjunto de dados CIFAR 10 que caiu apenas um ponto percentual em comparação com uma linha de base quantizada de forma semelhante. Com uma tensão de alimentação de 0,8 V, a eficiência energética da AnIA está entre 1050 e 1500 TOPS / W a 23,5 TOPS. Para a tensão de alimentação de 0,6 V, o AnIA atingiu 5,8 TOPS em torno de 1800-2900 TOPS / W.

Eficiência energética para vários aceleradores de IA em comparação com o chip de teste AnIA da Imec (clique para ampliar) (Imagem:Imec)

Inovação convencional

“A inovação [apresentada pelo Imec] vai se tornar popular”, disse Hiren Majmudar, VP e GM da unidade de negócios de computação da GlobalFoundries. “Estamos vendo parceiros, clientes da GlobalFoundries que estão no estágio de pós-produção com silício validado ... esperamos que o silício baseado em computação analógica alcance a produção no final deste ano ou no início do próximo ano. Em termos de implantação no mercado de massa, prevemos que a computação analógica comece a entrar no mercado de massa certamente não depois de 2022. Mas isso poderia acontecer antes disso. ”

Diederik Verkest (Imagem:Imec)

A GlobalFoundries está trabalhando para incluir a tecnologia AiMC da Imec como um recurso que pode ser implementado na plataforma 22 FDX para habilitar aceleradores de IA com baixo consumo de energia. O processo FD-SOI é projetado para baixo consumo de energia, com a capacidade de operar até 0,5 V com 1 pico amp por mícron para vazamento ultrabaixo em standby. O 22FDX com o novo recurso AiMC está em desenvolvimento na linha de produção de 300 mm da GlobalFoundries na Fab 1 em Dresden, Alemanha.

Já para o Imec, o programa de aprendizado de máquina continuará. A ambição do grupo é chegar a 10.000 TOPS / W (10 TOPS abaixo de 100mW) para sensores inteligentes sempre ligados e vestíveis de consumo, disse Verkest.

“Em nosso programa de ML, nossas próximas etapas são reduzir o tamanho dessas células de computação e começar a olhar para dispositivos de memória emergentes como uma implementação de próxima geração para esse princípio”, disse ele.

>> Este artigo foi publicado originalmente em nosso site irmão, EE Times.

Integrado

- Introdução aos circuitos integrados analógicos

- Circuitos Computacionais

- Projetando com Bluetooth Mesh:Chip ou módulo?

- A arquitetura do chip AI visa o processamento do gráfico

- Módulo Tiny Bluetooth 5.0 integra antena de chip

- Os pesquisadores criam uma pequena etiqueta de identificação de autenticação

- Processador de radar de imagem automotiva de 30 fps estreia

- Chip de radar de baixa potência usa redes neurais com pico

- A placa do sensor inteligente acelera o desenvolvimento de IA de borda

- Velocidades de UAV duráveis para produção