Adicionando histerese de limite para bloqueio de subtensão / sobretensão suave

Os divisores resistivos atenuam as altas tensões a um nível que os circuitos de baixa tensão podem acomodar sem serem sobrecarregados ou danificados. Em circuitos de controle de caminho de energia, os divisores resistivos ajudam a definir os limites de subtensão e sobretensão da fonte de alimentação. Esses circuitos de qualificação de tensão de alimentação são encontrados em sistemas automotivos, instrumentos portáteis alimentados por bateria e placas de processamento de dados e comunicação.

O bloqueio de subtensão (UVLO) evita que o sistema eletrônico a jusante opere com tensões de alimentação anormalmente baixas, o que pode causar mau funcionamento do sistema. Por exemplo, os sistemas digitais podem se comportar de maneira errática ou mesmo congelar quando a tensão de alimentação está abaixo da especificação. Quando a fonte de alimentação é uma bateria recarregável, o bloqueio por subtensão evita danos à bateria devido à descarga profunda. O bloqueio de sobretensão (OVLO) protege o sistema de tensões de alimentação altamente prejudiciais. Uma vez que os limites de subtensão e sobretensão dependem da faixa operacional válida do sistema, divisores resistivos são usados para configurar limites personalizados com o mesmo circuito de controle. A histerese de limite é necessária para obter uma função de bloqueio suave e sem vibração, mesmo na presença de ruído de alimentação ou resistência. Depois de discutir um circuito UVLO / OVLO simples, este artigo apresentará alguns métodos simples para adicionar histerese de limite, que é necessária quando o valor padrão é insuficiente.

Circuito de bloqueio de subtensão e sobretensão

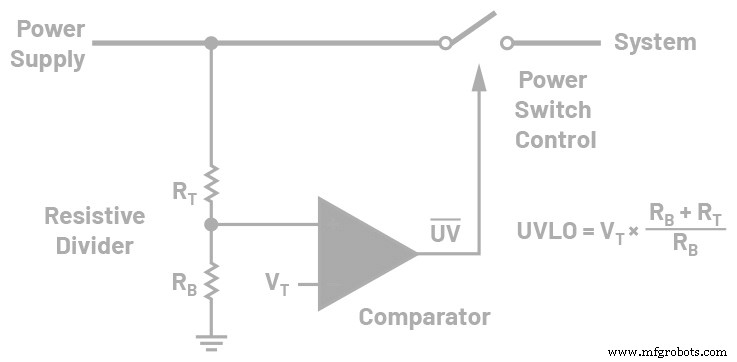

A Figura 1 mostra um circuito de bloqueio de subtensão (sem histerese por enquanto). Tem um comparador com uma tensão de referência positiva (V T ) em sua entrada negativa. O comparador controla uma chave liga / desliga que abre ou fecha o caminho entre a entrada da fonte de alimentação e o sistema eletrônico downstream. A entrada positiva do comparador se conecta a um divisor resistivo da entrada. Se a alimentação for ligada e começar a aumentar a partir de 0 V, a saída do comparador é inicialmente baixa, mantendo o interruptor de energia desligado. A saída do comparador desarma quando sua entrada positiva atinge V T . Neste momento, a corrente no resistor inferior é V T / R B . A mesma corrente flui em R T se o comparador não tiver corrente de polarização de entrada. Portanto, a tensão de alimentação quando o comparador desarma é V T + R T × V T / R B =V T × (R B + R T ) / R B . Este é o limite de fornecimento UVLO definido pelo divisor resistivo. Por exemplo, um V T de 1 V e R T =10 × R B produz um limite de UVLO de 11 V. Abaixo desse limite, a saída do comparador é baixa, abrindo a chave liga / desliga; acima desse limite de UVLO, a chave é fechada e a alimentação flui para ligar o sistema. O limite pode ser facilmente ajustado mudando a proporção de R B e R T . O valor absoluto do resistor é definido pela quantidade de corrente de polarização orçada para o divisor (mais sobre isso mais tarde). Para configurar um limite OVLO, basta trocar as duas entradas do comparador (por exemplo, consulte o comparador inferior na Figura 2) de modo que uma entrada alta force a saída do comparador para baixo e abra a chave.

Figura 1. Bloqueio de subtensão da fonte de alimentação usando um divisor resistivo, comparador e interruptor de alimentação. (Fonte:Dispositivos analógicos)

Embora não seja o foco deste artigo, o switch pode ser implementado com um MOSFET de potência de canal N ou P-channel. A discussão anterior assume uma chave MOSFET de canal N que abre (alta resistência) quando a tensão de sua porta é baixa (por exemplo, 0 V). Para fechar completamente (baixa resistência) um MOSFET de canal N, a tensão do gate deve ser mais alta do que a alimentação pelo menos a tensão limite do MOSFET, exigindo uma bomba de carga. Os controladores de proteção como LTC4365, LTC4367 e LTC4368 integram comparadores e bombas de carga para acionar MOSFETs de canal N enquanto ainda consome baixa corrente quiescente. Os MOSFETs do canal P não requerem uma bomba de carga, mas a polaridade da tensão da porta é invertida; isto é, uma baixa tensão fecha enquanto uma alta tensão abre uma chave MOSFET de canal P.

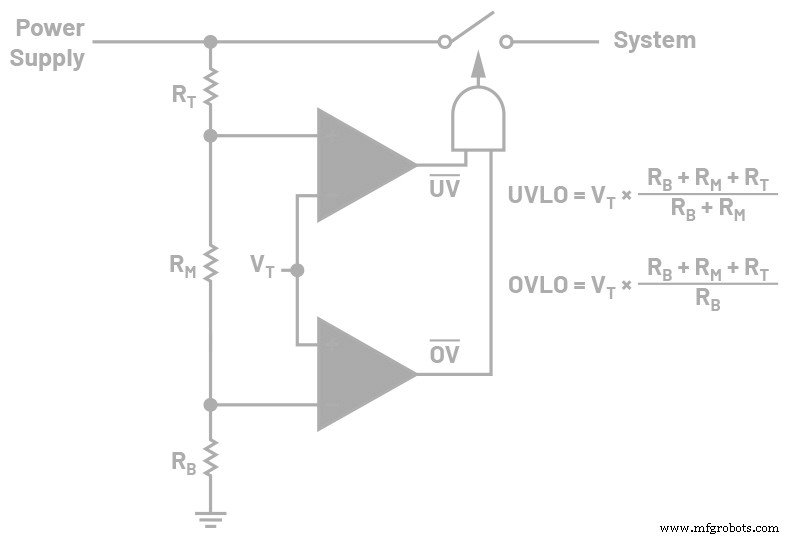

Voltando aos divisores resistivos:uma sequência de 3 resistores configura os limites de bloqueio de subtensão e sobretensão (Figura 2), salvando a corrente de polarização de um divisor em comparação com o uso de duas sequências de 2 resistores separadas. O limite de UVLO é V T × (R B + R M + R T ) / (R B + R M ) enquanto o limite OVLO é V T × (R B + R M + R T ) / R B . Uma porta AND combina a saída dos dois comparadores antes de enviá-la para a chave liga / desliga. Portanto, a chave liga / desliga fecha para alimentar o sistema quando a tensão de entrada está entre os limites de subtensão e sobretensão; caso contrário, a chave está aberta, desconectando a alimentação do sistema. Se o consumo de corrente do divisor não for uma preocupação, os divisores de subtensão e sobretensão separados fornecem mais flexibilidade no ajuste de cada limite independentemente do outro.

Figura 2. Travamento de subtensão e sobretensão usando um único divisor resistivo. (Fonte:Dispositivos analógicos)

Bloqueio de subtensão e sobretensão com histerese

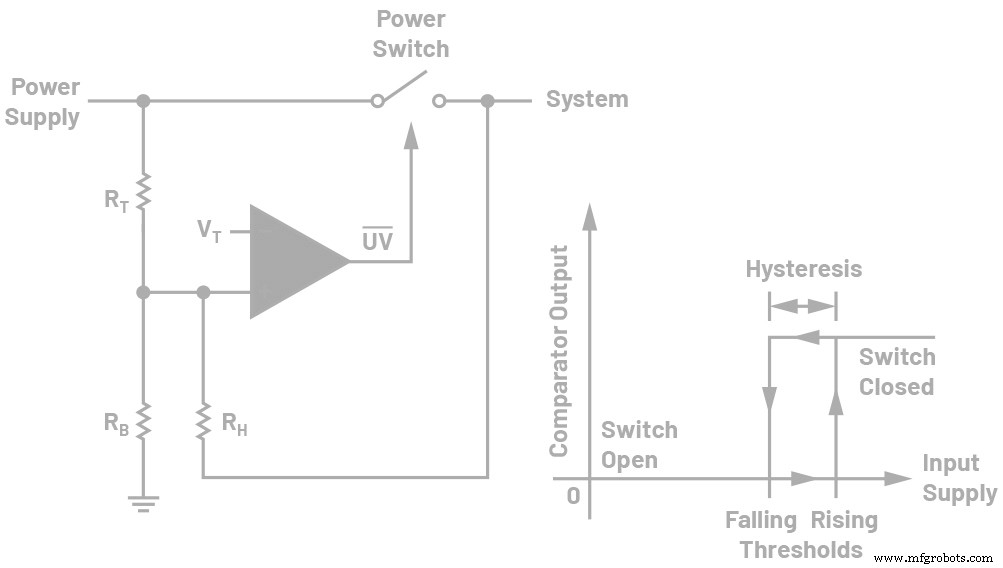

Na Figura 1, se a fonte de alimentação aumentar lentamente e tiver ruído ou se a fonte tiver resistência inerente (como em uma bateria) que faz com que a tensão caia com a corrente de carga, a saída do comparador mudará para alto e baixo repetidamente como a entrada cruza seu limite UVLO. Isso ocorre porque a entrada positiva do comparador fica repetidamente acima e abaixo de V T limite devido ao ruído de entrada ou queda devido à corrente de carga através da resistência da alimentação. Para circuitos alimentados por bateria, essa pode ser uma oscilação sem fim. O uso de um comparador com histerese elimina essa vibração, tornando a transição do switch mais suave. Conforme ilustrado na Figura 3, um comparador histérico apresenta diferentes limiares para uma subida (por exemplo, V T + 100 mV) vs. uma entrada em queda (por exemplo, V T - 100 mV). A histerese no nível do comparador é aumentada por R B e R T a 200 mV × (R B + R T ) / R B ao nível da oferta. Se o ruído ou a queda na entrada de alimentação estiver abaixo dessa histerese, a vibração é eliminada. Existem maneiras de adicionar ou aumentar a histerese se a fornecida pelo comparador estiver ausente ou insuficiente. Todos esses métodos usam feedback positivo na derivação do divisor - por exemplo, uma entrada crescente do comparador pula mais alto quando o comparador desarma. Para simplificar, as seguintes equações não assumem histerese intrínseca no comparador.

Figura 3. Adicionando histerese do limite de bloqueio de subtensão com um resistor da derivação do divisor para a saída da chave de alimentação. (Fonte:Dispositivos analógicos)

Resistor do divisor para a saída (Figura 3):

Adicione um resistor (R H ) da torneira divisória (a entrada positiva do comparador) para a saída do interruptor de alimentação. Quando o fornecimento começa a aumentar de 0 V, a entrada positiva do comparador está abaixo de V T e a saída do comparador é baixa, mantendo o interruptor de energia desligado. Suponha que a saída da chave esteja em 0 V devido à carga do sistema. Conseqüentemente, R H está em paralelo com R B para cálculo de limite de entrada. O limite de subtensão de entrada crescente é V T × ((R B || R H ) + R T ) / (R B || R H ), onde R B || R H =R B × R H / (R B + R H ) A chave liga acima desse limite, conectando a fonte ao sistema. Para calcular o limite de subtensão de entrada decrescente, R H está em paralelo com R T uma vez que a chave está fechada, dando o limite de subtensão de entrada em queda como:V T × (R B + (R T || R H )) / R B , onde R T || R H =R T × R H / (R T + R H ) Se o próprio comparador tiver alguma histerese, substitua V T com o limiar do comparador de subida ou descida nas equações anteriores. Lembre-se do exemplo da Figura 1, com V T =1 V e R T =10 × R B , onde os limites de aumento e queda são 11 V na ausência de histerese do comparador ou R H . Adicionando um R H =100 × R B , como na Figura 3, fornece um limite de entrada crescente de 11,1 V e um limite de queda de 10,09 V; ou seja, uma histerese de 1,01 V. Este método não funciona para OVLO porque uma entrada crescente desliga o interruptor de alimentação, causando R H para puxar a entrada do comparador para baixo (o que liga a chave novamente) em vez de aumentar.

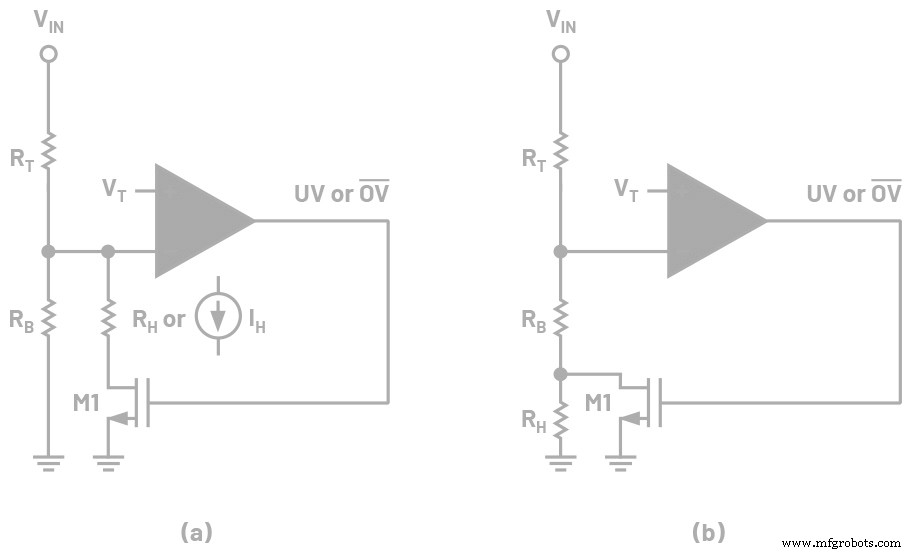

Troca em um resistor (Figura 4):

Outro método de adicionar histerese é alternar em um resistor que altera o valor efetivo do resistor inferior. O resistor comutado pode estar em paralelo (Figura 4a) ou em série (Figura 4b). Considere a Figura 4a:quando V IN é baixo - digamos, 0 V - a saída do comparador (nó UV ou OV) é alta, ligando o MOSFET M1 do canal N e conectando R H em paralelo com R B . Suponha que a resistência de M1 seja insignificante em comparação com R H ou está incluído em R H Valor de. O limite de entrada crescente é o mesmo que na Figura 3:V T × ((R B || R H ) + R T ) / (R B || R H ) Uma vez que V IN está acima deste limite, a saída do comparador é baixa, desligando M1 e desconectando R H do divisor. Portanto, o limite de entrada decrescente é o mesmo que na Figura 1:V T × (R B + R T ) / R B . Continuando nosso exemplo com V T =1 V, R T =10 × R B e R H =100 × R B , o limite de entrada crescente é de 11,1 V e o limite de queda é de 11 V; isto é, R H produz uma histerese de 100 mV. Este e os métodos a seguir podem ser usados para bloqueio de subtensão ou sobretensão, pois sua finalidade depende de como a saída do comparador liga a chave liga / desliga (não mostrado).

Figura 4. Adicionando subtensão ou histerese de limite de bloqueio de sobretensão com um (a) resistor de derivação ou corrente comutada e (b) um resistor em série. (Fonte:Dispositivos analógicos)

A configuração da Figura 4b fornece o limite de entrada crescente como V T × (R B + R T ) / R B e o limite de entrada decrescente como V T × (R B + R H + R T ) / (R B + R H ) R H =R B / 10 na Figura 4, fornecendo 11 V como o limite de entrada crescente e 10,091 V como o limite decrescente - ou seja, 909 mV de histerese. Isso mostra que a configuração da Figura 4b precisa de um R H muito menor para produzir uma histerese muito maior.

Troca de corrente (Figura 4a):

O resistor R H da Figura 4a pode ser substituído por uma fonte atual I H . Este método é usado nos controladores priorizados LTC4417 e LTC4418. Quando V IN é baixo, a saída alta do comparador permite I H . No limite de entrada crescente, a entrada negativa do comparador está em V T . Portanto, a corrente em R T sou eu H + V T / R B , produzindo o limite crescente como V T + (I H + V T / R B ) × R T =V T × (R B + R T ) / R B + I H × R T . Uma vez que V IN está acima desse limite, I H é desligado pela baixa saída do comparador. Portanto, o limite de queda é o mesmo que na Figura 1:V T × (R B + R T ) / R B , e a histerese do limite de entrada é I H × R T .

Tendência do divisor resistivo atual Conclusão

As equações anteriores assumiram que a corrente de polarização de entrada da entrada do comparador é zero, enquanto os exemplos consideraram apenas as relações do resistor em vez de valores absolutos. As entradas do comparador têm ambas as tensões de deslocamento de entrada (V OS ), imprecisão de referência (que pode ser prejudicada com V OS ), e polarização de entrada ou corrente de fuga (I LK ) A suposição de vazamento zero funciona se a corrente de polarização do divisor, V T / R B no ponto de disparo da Figura 1, é muito maior do que o vazamento de entrada. Por exemplo, um divisor de corrente que é 100 vezes a corrente de fuga de entrada mantém o erro de limite de entrada causado por fuga abaixo de 1%. Outro método é comparar o erro de limite induzido por vazamento com aquele da tensão de deslocamento. As nãoidealidades do comparador mudam a equação do limite de subtensão de entrada da Figura 1 para ser:(V T ± V SO ) × (R B + R T ) / R B ± I LK × R T (semelhante à equação da corrente histérica anterior), que pode ser reescrita como (V T ± V SO ± I LK × R B × R T / (R B + R T )) × (R B + R T ) / R B . O vazamento de entrada aparece como um erro na tensão de limiar do comparador e este erro pode ser minimizado em relação à tensão de deslocamento, ou seja, I LK × (R B || R T )

Como exemplo, o controlador de proteção de subtensão e sobretensão LTC4367 tem vazamento máximo de ± 10 nA para os pinos UV e OV, enquanto a tensão de deslocamento de limite de 500 mV do comparador de pino UV / OV é ± 7,5 mV (± 1,5% de 500 mV). Orçar um erro de limite causado por vazamento de ± 3 mV (± 0,6% de 500 mV, ou menos da metade do desvio de 7,5 mV) dá R B || R T <3 mV / 10 nA =300 kΩ. Para configurar um limite de subtensão de entrada de 11 V com um limite de comparador de 0,5 V, é necessário R T =R B × 10,5 V / 0,5 V =21 × R B . Portanto, R B || R T =21 × R B / 22 <300 kΩ, dando R B <315,7 kΩ. O valor padrão de 1% mais próximo para R B é 309 kΩ, produzindo R T para ser 6,49 MΩ. A corrente de polarização do divisor no ponto de desarme é 0,5 V / 309 kΩ =1,62 µA, que é 162 vezes a corrente de fuga de 10 nA. Este tipo de análise é importante ao minimizar a corrente do divisor sem aumentar o erro de limite devido à corrente de fuga de entrada do comparador.

Os divisores resistivos permitem o fácil ajuste dos limites de subtensão da fonte de alimentação e de bloqueio de sobretensão com o mesmo circuito de controle baseado em comparador. O ruído ou a resistência do fornecimento requer histerese de limite para evitar a vibração de ligar e desligar à medida que o fornecimento cruza o limite. Alguns métodos diferentes para implementar a histerese de bloqueio de subtensão e sobretensão foram mostrados. O princípio essencial é ter algum feedback positivo na torneira divisória quando o comparador desarma. Ao adicionar ou aumentar a histerese dos ICs do controlador de proteção, alguns métodos dependem da disponibilidade da saída do comparador ou de um sinal semelhante nos pinos de saída do IC. Ao escolher os valores do resistor, deve-se tomar cuidado para que o vazamento de entrada do comparador não se torne uma fonte dominante de erro de limite. Um conjunto abrangente de equações relacionadas, incluindo as deste artigo, foi implementado em uma planilha que está disponível para download.

Pinkesh Sachdev é engenheiro sênior de aplicativos para gerenciamento de sistemas de energia na Analog Devices. Ele recebeu seu B.Tech. diploma do Instituto Indiano de Tecnologia, Mumbai, Índia, e seu M.S. formado pela Stanford University, ambos em engenharia elétrica. Ele pode ser contatado em pinkesh.sachdev@analog.com.

Pinkesh Sachdev é engenheiro sênior de aplicativos para gerenciamento de sistemas de energia na Analog Devices. Ele recebeu seu B.Tech. diploma do Instituto Indiano de Tecnologia, Mumbai, Índia, e seu M.S. formado pela Stanford University, ambos em engenharia elétrica. Ele pode ser contatado em pinkesh.sachdev@analog.com.

Conteúdos Relacionados:

Para obter mais informações sobre o Embedded, assine o boletim informativo semanal da Embedded por e-mail.

Integrado

- Histerese

- C# para loop

- Arm permite instruções personalizadas para núcleos Cortex-M

- Co-simulação para designs baseados em Zynq

- Infineon apresenta TPM 2.0 para Indústria 4.0

- Cervoz:Solução T405 M.2 NVMe para armazenamento industrial

- Syslogic:computador ferroviário para manutenção preditiva

- Automação:Garra menor sem marcas para superfícies lisas, brilhantes ou perfuradas

- Quatro dicas para adicionar serviços LTL à sua corretora

- Sobretensão e subtensão:tudo o que você precisa saber