Chave de inovação de material para 7nm e além

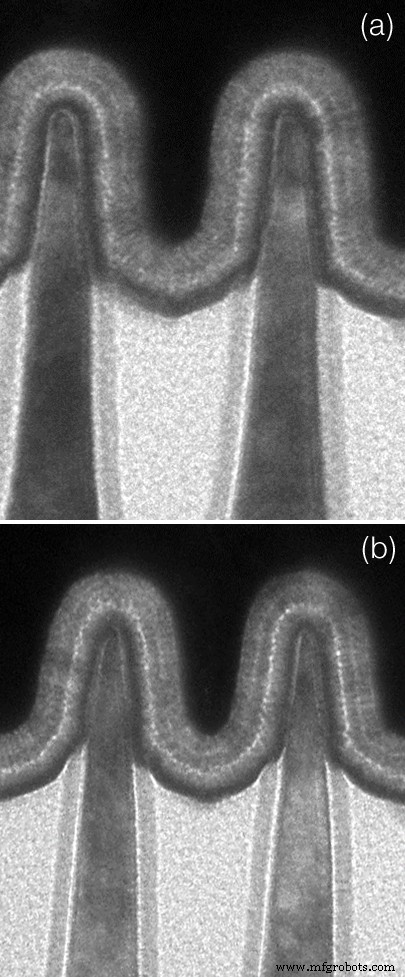

Si simétrico Perfis FinFET (a) e SiGe FinFET (b) a 10 nm feitos pela IBM Research no NanoTech Complex da SUNY Polytechnic em Albany, NY. Isso ilustra que o SiGe Fin pode fornecer propriedades elétricas superiores do que o Si Fin.

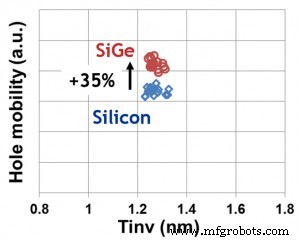

Os chips baseados em FinFET * de nó de 14 nm de hoje usam canais apenas de silício (o silício não é estável além desta escala). A tecnologia FinFET baseada em SiGe, alternativamente, demonstrou melhoria de desempenho com regras básicas de tecnologia de 10 nm (padrões da indústria), fornecendo soluções elegantes para uma opção de tecnologia CMOS viável. Uma dessas elegantes soluções SiGe FinFET é a permissão para dispositivos de baixo consumo e alto desempenho no mesmo chip - sem perder desempenho ou variabilidade em um tipo de dispositivo em relação ao outro.

A tecnologia SiGe FinFET também oferece confiabilidade elétrica superior em relação ao Si FinFET. E isso leva à estabilidade de desempenho de nível de chip melhorada do que Si FinFET ao longo da vida útil do chip. Isso significa que o fluxo de integração de processo idêntico é adequado para designs de supercomputador e também para designs móveis.

O SiGe amplia os limites do dimensionamento do chip, alterando a maneira como a corrente passa pelo canal de um transistor. Acontece que ao adicionar átomos de germânio maiores a um cristal feito de átomos de silício menores, o cristal desenvolve uma incompatibilidade de rede, gerando tensão no canal do transistor. Essa deformação torna possível mover mais corrente através do canal em tensões mais baixas. Portanto, usando o SiGe como um material de canal, podemos traçar um roteiro para dimensões menores, mantendo um equilíbrio entre potência e desempenho.

SiGe para os nós à frente:Resolvendo os desafios de produzir chips de 10nm e 7nm

A retenção de tensões em todo o fluxo de integração, junto com o controle de defeitos, são dois dos principais desafios técnicos para a produção de SiGe FinFET em nós de 10 nm e abaixo. Os canais de transistor podem perder tensão durante os processos de recozimento térmico que ativam dopantes e estabilizam a integridade do transistor; ou durante os processos de recesso de fonte / drenagem que formam a junção uniforme do topo da Aleta até a parte inferior da Aleta; ou mesmo a padronização de aletas em designs específicos que requerem aletas de comprimento curto.

O controle de defeitos também é crítico na produção em massa de uma tecnologia CMOS. Com a incompatibilidade de rede entre um canal de SiGe e seu substrato de wafer de silício, é um desafio manter o nível de defeito de manufatura necessário em todo o wafer. Mas com nosso gerenciamento avançado de crescimento epitaxial (cristal), integração inovadora de processo do módulo Fin e engenharia de fonte / drenagem, desenvolvemos soluções para garantir a tensão no canal em todo o fluxo de integração, ao mesmo tempo mantendo baixa defetividade em nosso teste de 10 nm e 7 nm nós.

Com este estudo abrangente de viabilidade da tecnologia SiGe FinFET de acordo com as regras básicas da tecnologia de 10 nm, estamos agora trabalhando com projetistas e fabricantes de chips para produzir em massa a tecnologia SiGe FinFET. Prevejo que nossa tecnologia SiGe FinFET substituirá o silício FinFET na próxima geração de nós de tecnologia CMOS para uso em computação, abrangendo supercomputadores a dispositivos móveis. Eles também podem ser usados em aplicativos “more than Moore” em nuvem e computação cognitiva, onde baixo fornecimento de energia e baixo consumo de energia são altamente desejáveis, como aplicativos em nuvem e computação cognitiva.

Leitura adicional

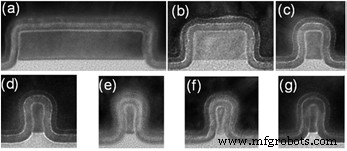

Seções transversais de Aleta e empilhamento de porta para largura de Aleta variando de 87nm (a) a 3nm (g) para maior conteúdo de Ge para Aleta de SiGe.

No simpósio IEEE deste ano sobre tecnologia VLSI (integração em escala muito grande), nossas equipes apresentaram uma série de novos dispositivos, materiais e inovações de integração centradas no uso de SiGe com regras básicas de 10 nm e também como um caminho a seguir para resolver o dimensionamento e os desafios de desempenho do nó de teste de 7 nm que fabricamos no ano passado.

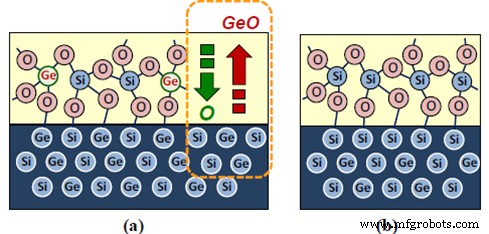

Nossas apresentações cobriram recursos técnicos críticos e inovação de processo fundamental para o controle de defeitos; inovações em gate stack e camada interfacial adequadas para SiGe FIN; bem como técnicas de contato avançadas na plataforma SiGe FinFET, relatadas no artigo de pesquisa T2.2 na conferência VLSI. O artigo de pesquisa T4.3 apresentou o inventivo processo seletivo de eliminação de óxido de germânio para construir uma camada interfacial robusta para o canal de SiGe.

Mobilidade clara benefício de SiGe Fin sobre Si Fin, levando a ganho de desempenho de nível de chip.

Nossa pesquisa liderada pelo Dr. Pouya Hashemi, que se concentra na extensibilidade da tecnologia SiGe FinFET para nós de alto desempenho futuros, também foi apresentada no VLSI. No artigo de pesquisa T9.3, relatamos a viabilidade de alcançar um desempenho mais alto com maior conteúdo de Ge e largura de Fin menor e maior dimensionamento da pilha de portas. Os participantes do VLSI Symposium podem encontrar esses artigos técnicos no site do VLSI. Você também pode ingressar no Grupo do Linkedin para obter mais informações.

T2.2: Tecnologia FINFET com Canal de SiGe de Alta Mobilidade para 10 nm e além

T4.3: GeO seletivo x -Scavenging from Interfacial Layer on Si 1-x Ge x Canal para alta mobilidade Si / Si 1-x Ge x Aplicativo CMOS

T9.3: Substituição High-K / Metal-Gate High-Ge-Content Strained SiGe FinFETs com High Hole Mobility e Excelente SS e confiabilidade em EOT agressivo de ~ 7Å e dimensões reduzidas a larguras de Fin de Sub-4nm

T7.2: Contatos de siliceto de liner de Ti e NiPt / Ti para tecnologias avançadas

Esquema de o processo de eliminação de GeOx seletivo inventivo (a) e a camada interfacial livre de GeOx (b) com canal de SiGe.

* -FinFET refere-se a uma arquitetura de transistor que aumenta o canal do transistor para que se pareça com aletas)

Dechao Guo é um membro da equipe de pesquisa, inventor mestre e gerente de Design e Integração de Dispositivos Avançados na IBM Research.

Nanomateriais

- Para a nuvem infinita e além

- IBM na SPIE:Sete avanços para além dos chips 7nm

- IoT além do PoC:uma mudança na mentalidade

- Tecnologia Digital Twin:Além da Rocket Science

- Visão da máquina é a chave para a indústria 4.0 e IoT

- Missouri Technology Corporation para lançar iniciativa estadual de empreendedorismo e inovação

- Como a IoT e a automação industrial estão impulsionando a inovação

- A colaboração é fundamental para as empresas de manufatura e tecnologia avançada (AMT) da Europa

- AMRC impulsiona inovação em tecnologia e economia circular

- ABB Robotics:inovação tecnológica e pesquisa e desenvolvimento de robótica