Transistores de efeito de campo Nanoflake SnSe multicamadas com contatos óhmicos de baixa resistência

Resumo

Relatamos cristais simples de monosseleneto de estanho tipo p (SnSe), cultivados em ampolas de quartzo duplamente seladas usando uma técnica de Bridgman modificada a 920 ° C. As medições de difração de pó de raios-X (XRD) e espectroscopia de energia dispersiva de raios-X (EDX) confirmam claramente que o SnSe crescido consiste em SnSe de cristal único. O transporte elétrico de nanoflocos de SnSe multicamadas, que foram preparados por esfoliação a partir de cristais únicos, foi conduzido usando estruturas de transistor de efeito de campo (FET) back-gated com contatos de Au e Ti em SiO 2 / Si substratos, revelando que os nanoflocos de SnSe de múltiplas camadas exibem características semicondutoras do tipo p devido às lacunas de Sn nas superfícies dos nanoflocos de SnSe. Além disso, um forte efeito de triagem de portadores foi observado em FETs de nanofloco de SnSe de 70 a 90 nm de espessura. Além disso, o efeito dos contatos de metal para FETs baseados em nanofloco de SnSe multicamadas também é discutido com dois metais diferentes, como contatos de Ti / Au e Au.

Histórico

Os calcogenetos metálicos transientes oferecem uma gama de bandgaps óticos, que os tornam adequados para uso em várias aplicações óticas e optoeletrônicas [1]. Filmes finos desses materiais, incluindo PbTe, PbSe e Bi 2 Se 3 [2], têm atraído atenção considerável devido ao seu uso prospectivo em dispositivos optoeletrônicos infravermelhos, detectores de radiação, células solares, dispositivos de memória e dispositivos de registro holográfico [3,4,5,6,7,8]. Mono e disselenetos de estanho (SnSe e SnSe 2 ) têm estado no centro das pesquisas, devido aos seus altos coeficientes de absorção, o que é vantajoso para aplicações optoeletrônicas. Além disso, esses materiais são promissores para uso em aplicações termelétricas [9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24]. Monosseleneto de estanho (SnSe) é um semicondutor do tipo p com um bandgap para transições indiretas permitidas perto de ~ 0,9 eV e para transições diretas permitidas perto de ~ 1,2 eV, enquanto o disseleneto de estanho (SnSe 2 ) é um semicondutor do tipo n [6]. A estrutura cristalina do SnSe é ortorrômbica e seus parâmetros de célula unitária são a =11,496 Å, b =4,151 Å, e c =4,444 Å; esta estrutura ortorrômbica se transforma em uma estrutura tetragonal em alta temperatura que, no entanto, é inferior ao ponto de fusão de SnSe 2 [25].

Recentemente, dispositivos elétricos de calcogeneto e dichalcogeneto binários baseados em Sn, incluindo transistores de efeito de campo (FETs) com uma porta traseira comum de grande área, foram extensivamente investigados. Em particular, muito progresso foi feito na caracterização de FETs baseados em dichalcogeneto Sn [26, 27]. Em 2016, Pei et al . relatou SnSe de poucas camadas 2 FET, demonstrando uma alta proporção liga / desliga de ~ 10 4 com uma camada de cobertura superior de um eletrólito de polímero [27]. Guo et al. também relatou um SnSe de alta mobilidade e poucas camadas 2 FET com espessura de ~ 8,6 nm [28]. A partir de trabalhos anteriores, foi confirmado que filmes SnSe finos e de baixa concentração de portadores geram alta mobilidade e relação atual on / off de SnSe 2 FETs. Apesar desses esforços na utilização de SnSe 2 , no entanto, a caracterização elétrica de SnSe FETs, preparados por esfoliação de monocristais, não foi relatada. Uma caracterização detalhada do transporte elétrico em SnSe de poucas e múltiplas camadas 2 flocos devem ser realizados para avaliar as propriedades de transporte elétrico de calcogenetos de estanho, como nanoflocos de SnSe, porque se espera que cristais de SnSe únicos exibam uma alta mobilidade de portador de ~ 7835 cm 2 / V s [29].

Neste trabalho, caracterizamos SnSe monocristalino cultivado usando um método de Bridgman modificado. O transporte elétrico em FETs de nanofloco de SnSe multicamadas preparados por esfoliação a partir de cristais únicos em massa foi caracterizado pela primeira vez usando estruturas FET back-gated em SiO 2 Substratos / Si. Além disso, o efeito dos contatos de metal em FETs baseados em nanofloco de SnSe multicamadas também foi estudado para dois tipos diferentes de contatos (Ti / Au e Au) porque a função de trabalho do metal de contato determina a condução de portadores de orifícios através da barreira Schottky no interface nanoflake metal-SnSe.

Métodos

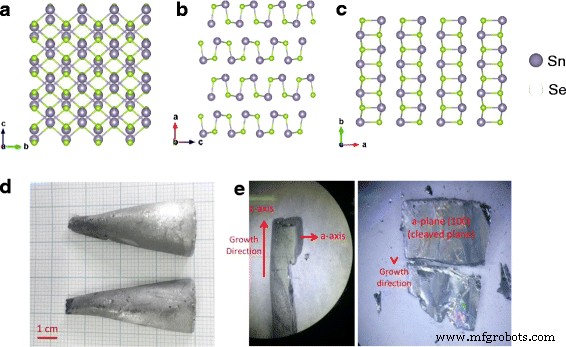

SnSe tem uma estrutura cristalina ortorrômbica em camadas em temperatura ambiente [24]. A Figura 1a-c mostra as vistas em perspectiva da estrutura de cristal SnSe ao longo do a , b , e c direções axiais. Como mostrado na Fig. 1c, placas de SnSe com camada de dois átomos são ranhuradas, enquanto a clivagem fácil nos cristais ocorre ao longo do plano (100) (Fig. 1b). Cristais de SnSe únicos foram cultivados usando o método de Bridgman modificado, conforme descrito anteriormente [24, 30]. Quantidades estequiométricas de Sn (99,999% de injeção, Alfa Aesar) e Se (99,999% em pó, Alfa Aesar) foram primeiro derretidas em um lingote (~ 20 g) em uma ampola de quartzo duplamente selada. As matérias-primas foram aquecidas lentamente a 500 ° C e repousadas por 10 h, então mantidas a 920 ° C por mais 10 h antes de desligar o forno. O lingote obtido foi moído em pó e colocado em um tubo de quartzo em forma de cone, evacuado e selado à chama. Este tubo de quartzo em forma de cone carregado foi colocado em um tubo de quartzo maior. O tubo externo foi preenchido com Ar gasoso para evitar explosão e oxidação, e então selado à chama. A ampola de quartzo carregada foi colocada na posição em que o gradiente de temperatura era maior no forno de tubo vertical. O forno de tubo vertical foi lentamente aquecido a 970 ° C por 20 h, mantido por 10 h e, em seguida, resfriado a 830 ° C a uma taxa de 0,5 ° C / h. O forno foi mantido a 830 ° C por 24 horas adicionais e então resfriado a 500 ° C a uma taxa de 100 ° C / h antes de desligar o forno.

a - c Estrutura cristalina dos cristais SnSe ao longo de a -, b -, e c - direções axiais. d Fotografia de um SnSe monocristalino crescido. e Fotografias de cristais de SnSe clivados ao longo do a plano do eixo (100). Vistas superiores do plano clivado (100) do cristal único SnSe ( imagem à direita em d )

Resultados e discussão

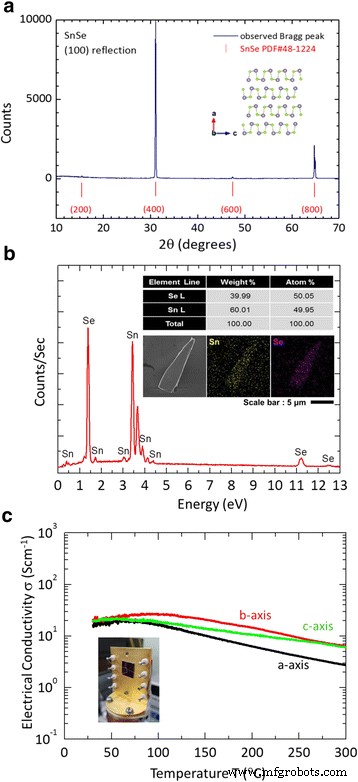

Um cristal SnSe em forma de cone (diâmetro, 30 mm; comprimento, 70 mm) foi obtido e é mostrado na Fig. 1d-e. O cristal obtido foi dividido em duas partes devido a uma rachadura que ocorreu durante a extração do cristal da ampola de quartzo (Fig. 1d). A qualidade dos cristais de SnSe crescidos foi verificada usando um difratômetro de raios-X de pó (XRD, New D8-Advance, Bruker-AXS, Alemanha) com Cu Kα ( λ =1,5406 Å). A Figura 2a mostra o padrão de XRD do arquivo de difração de potência (PDF) 48-1224 para SnSe ortorrômbico, junto com o padrão para o cristalográfico a eixo, que é perpendicular ao plano clivado (100) do cristal SnSe. Como mostrado na Fig. 2a, o padrão de XRD de SnSe cristalino único sugere fortemente um cristal ortorrômbico de fase única com um grupo espacial Pnma [31], indicando uma forte orientação preferencial com (h00) reflexões, o que está de acordo com um relatório anterior [32]. Além disso, os picos predominantes foram (400) e (800), em 2 θ = 31,081 ° e 64,818 °, respectivamente, conforme mostrado na Fig. 2a [33]. Conforme mostrado na Fig. 2b, a espectroscopia de energia dispersiva de raios-X (EDX) revelou a razão atômica Sn:Se de 1:1, confirmando a razão estequiométrica de Sn e Se (inserção da Fig. 2b). Inserções da Fig. 2b também mostram uma imagem de microscopia eletrônica de varredura (SEM) e mapeamento EDX de um nanoflake FET de SnSe com uma espessura de dispositivo de 90 nm. Este resultado está de acordo com relatórios anteriores [24, 33]. Além disso, a condutividade elétrica de SnSe monocristalino (inserção da Fig. 2b) foi medida para temperaturas variando de 30‒300 K, usando o método de sonda de quatro pontos convencional. A Figura 2c mostra a condutividade elétrica dependente da temperatura de cristais únicos de SnSe ao longo de três direções cristalográficas diferentes, indicando comportamentos dependentes da temperatura semelhantes e comportamentos de anisotropia devido a diferentes mobilidades de orifícios em SnSe ao longo das diferentes direções axiais. Conforme mostrado na Fig. 2c, a condutividade elétrica ao longo do b - e c -eixo a 300 K foi determinado como sendo ~ 6,00 S cm −1 , que é aproximadamente 2,2 vezes maior do que o a -eixo (~ 2,7 S cm −1 ) Este resultado está de acordo com resultados anteriores para SnSe monocristalino [24]. Na Fig. 2c, a condutividade elétrica dependente da temperatura de SnSe monocristalino é mostrada para a faixa de semicondutor (30–100 K) e para a faixa metálica (> 100–300 K). Acima de 100 K, os cristais de SnSe crescidos exibiram comportamento de transporte metálico, consistente com observações anteriores [24].

a Padrão de XRD de cristais únicos de SnSe, mostrando uma difração clara (h00). b Espectro de EDX dos cristais únicos de SnSe . Inserido mostra a informação detalhada da razão atômica de Sn e Se. Inserções exibem uma imagem SEM e mapeamento EDX de um nanoflake FET SnSe com uma espessura de dispositivo de 90 nm. c Condutividade elétrica dependente da temperatura dos cristais únicos de SnSe, para temperaturas que variam de 30–300 K, medida usando o método de sonda de quatro pontos

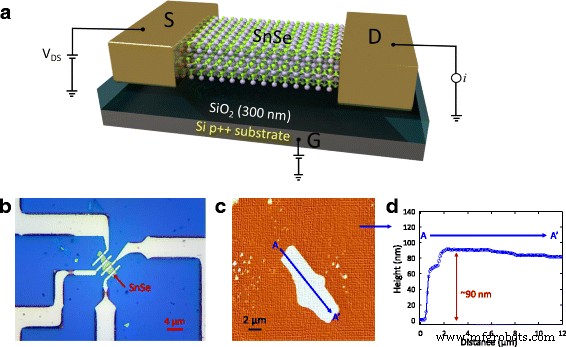

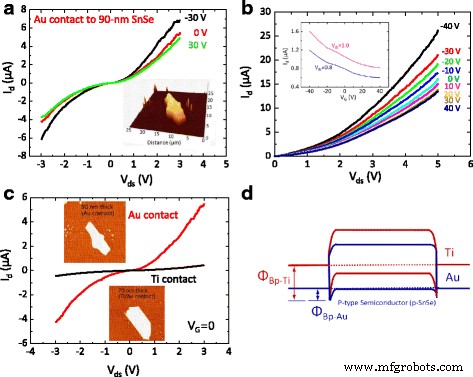

Os dispositivos SnSe FET foram fabricados da seguinte forma. Primeiro, os nanoflocos de SnSe foram esfoliados mecanicamente em um SiO 2 de 300 nm de espessura / p ++ Substrato de Si de cristais de SnSe simples, facilmente clivado no plano (100) usando o método de fita adesiva bem conhecido (Fig. 1e) [26, 27, 34]. As medições de transporte elétrico em FETs de nanoflocos SnSe individuais conforme preparados foram realizadas em temperatura ambiente na configuração de FETs com back-gated. A Figura 3a mostra esquematicamente os dispositivos FET baseados em nanoflake de SnSe com uma porta traseira de grande área. Neste estudo, dois nanoflocos de SnSe (nanoflocos de SnSe de 70 e 90 nm de espessura) foram preparados no SiO 2 Substrato / Si. Os SnSe FETs foram fabricados usando o método de litografia de feixe de elétrons padrão seguido por dois tipos de metalização, ou seja, Au (espessura, 100 nm) e Ti / Au (espessuras, 10/100 nm) foram considerados como contatos ôhmicos em nanoflocos SnSe. Antes do processo de metalização, o ataque de óxido tamponado (BOE) foi realizado para remover o polímero e os resíduos de óxido nas superfícies dos nanoflocos. A Figura 3b mostra uma imagem óptica de um nanoflake FET SnSe com uma espessura de dispositivo de 90 nm. As espessuras dos nanoflocos SnSe foram medidos usando um microscópio de força atômica (AFM) em temperatura ambiente (Fig. 3c-d). Como mostrado na Fig. 3b e inserção da Fig. 2b, o SnSe FET fabricado de 90 nm de espessura tinha o comprimento do canal ( L ) de 5 μm e largura ( W ) de 4,71 μm, enquanto para o SnSe FET de 70 nm de espessura L era 5 μm e W foi de 6 μm. Toda a corrente-tensão ( I - V ) características foram medidas usando um analisador de parâmetro de semicondutor (HP 4155C, Agilent Technologies, EUA) em uma estação de sonda eletricamente blindada em temperatura ambiente. A Figura 4a mostra a corrente de dreno ( I d ) em função da tensão da porta ( V g ), para o nanofloco SnSe de 90 nm de espessura, para as tensões de fonte-dreno ( V ds ) de −30, 0 e 30 V, à temperatura ambiente, indicando um claro comportamento do semicondutor do tipo p, que é atribuído principalmente às vacâncias de Sn, conforme relatado anteriormente [15, 16, 22, 24, 35,36,37 , 38,39]. O resultado na Fig. 4a implica que AU metálico com sua função de alto trabalho deve formar contatos ôhmicos fracos em nanoflocos SnSe, indicando uma barreira Schottky inferior para a banda de condução de nanoflocos SnSe. Uma discussão mais detalhada, para funções de trabalho de diferentes metais, será fornecida posteriormente. A Figura 4b mostra I d vs. V ds para diferentes V g , variando de −40-40 V, em etapas de 10 V. Da Fig. 4b, a mobilidade do orifício ( μ p ) é determinado ter aproximadamente 2,7 cm 2 / V s, obtido de μ p = t m [ L ⁄ ( WC boi V ds)], onde t m é a trans-condutância (= dI d / dV g =2,89 × 10 - 8 A / V ), L é o comprimento (~ 5,1 μm), W é a largura (~ 4,75 μm), V ds é a tensão da fonte de drenagem (~ 1 V) do SnSe FET, e C boi (= ε r ε 0 / d =11,5 nF / cm 2 ) com ε r (a constante dielétrica) de 3,9 e d (a espessura da camada de óxido) de 300 nm é a capacitância por unidade de área do nanoflake SnSe com back-gated FET. A mobilidade do orifício avaliada dos FETs de nanofloco de SnSe esfoliados mecanicamente é muito menor do que a de filmes finos de SnSe epitaxial (~ 60 cm 2 / V s) preparado por deposição de laser pulsado em substratos de MgO usando alvos ricos em Se [40]. No entanto, o valor obtido aqui é ~ 1,8 vezes maior do que o obtido para nanoplacas de SnSe de cristal único (~ 1,5 cm 2 / V s) [33]. Tal mobilidade de orifício relativamente baixa pode ser atribuída a um forte espalhamento de fônon devido às vacâncias de Sn na superfície SnSe [18, 36, 41, 42] e uma barreira Schottky relativamente alta na interface de nanofloco Au metal-SnSe.

a Esquema de um nanoflake FET de SnSe esfoliado mecanicamente em um SiO 2 / p ++ Substrato de Si. b Imagem óptica de um nanoflake FET fabricado de SnSe que foi usado para medições de transporte elétrico. c Imagem AFM de um nanofloco SnSe em um SiO 2 Substrato / Si. d Perfil de altura AFM de um nanofloco SnSe, para estimar a espessura e fabricar dispositivos FET

a Escoar a corrente ( I d ) em função da tensão de dreno-fonte aplicada ( V ds ), para as tensões de porta ( V g ) de −30, 0 e 30 V, para um FET de nanofloco SnSe de 90 nm de espessura, à temperatura ambiente. b eu d vs. V ds para V g variando de −40–40 V em etapas de 10 V, para o nanoflake SnSe de 90 nm de espessura FET. A inserção mostra eu d vs. V g para V ds de 0,8 e 1,0 V, medido à temperatura ambiente. c eu d vs. V ds sem polarizar V g (=0) para contatos de Au e Ti em um nanoflake FET de SnSe. A inserção mostra uma imagem digitalizada AFM de nanoflocos de SnSe. d Esquemas dos diagramas de banda de energia de dois metais, Au e Ti, em semicondutores SnSe do tipo p

Além disso, observamos um fraco ajuste da condutância da porta na região de depleção do I d vs. V ds curva (Fig. 4c) e uma relação liga / desliga de baixa corrente (~ 2 em V ds de 1 V, inserções da Fig. 4c) no nanoflake p-SnSe FET com contatos de metal Au. Um comportamento semelhante foi relatado para outros materiais semicondutores bidimensionais (2D) com uma espessura semelhante, incluindo SnS FETs (espessura, ~ 50-80 nm) [43], nanoplacas de SnSe de ~ 15,8 nm de espessura [33], ~ 80 -nm-thick MoS 2 [44] e SnSe 2 de ~ 84 nm de espessura [26]. Esses comportamentos podem ser explicados pelo efeito do comprimento de blindagem de portador finito devido à existência de uma camada superficial condutiva em dispositivos FET com espessuras maiores que o comprimento de blindagem \ (\ left (\ sqrt {\ varepsilon {K} _B T} {e } ^ 2 p \ right) \), onde ε , K B e p são a constante dielétrica do semicondutor, a constante de Boltzmann e a densidade do portador do furo, respectivamente, [43].

Os contatos de metal determinam de maneira importante as características dos dispositivos 2D FET [45]. Para determinar o efeito das funções de trabalho do metal em SnSe, consideramos Au (função de trabalho, ~ 5,1 eV) e Ti (função de trabalho, ~ 4,3 eV) como contatos de metal em nanoflocos de SnSe. A Figura 4c mostra o I típico d vs. V ds curvas sem modulação de porta ( V g =0) para FETs de nanofloco SnSe com contatos Au e Ti, indicando uma resistência geral mais alta para Ti (~ 15,4 MΩ) em comparação com aquela para Au (~ 0,56 MΩ). Assim, a barreira Schottky na interface metal-SnSe é maior para Ti (Fig. 4c). Este comportamento é sempre observado em todos os SnSe FET com contatos Ti. Conforme mostrado na Fig. 4d, a altura da barreira Schottky para orifícios aumenta à medida que a função de trabalho do metal diminui. Assim, metais como Pd, Au e Pt, com grandes funções de trabalho, podem ser adequados como contatos ôhmicos em FETs de nanofloco p-SnSe porque, para esses metais, a altura da barreira Schottky para injeção de orifícios será menor. A resistência de contato deve ser medida para metais adicionais, para determinar sua adequação como contatos de metal em nanofoco de SnSe. Este problema está sendo resolvido usando o método de comprimento de transferência.

Conclusões

Em resumo, nanoflocos SnSe de múltiplas camadas foram cultivados, esfoliados e caracterizados para canais SnSe FET com uma estrutura FET back-gated em SiO 2 Substratos / Si. Medições de transporte elétrico demonstraram que nanoflocos de SnSe multicamadas com contatos de metal Au exibem características de semicondutor do tipo p com uma barreira Schottky relativamente baixa e baixa resistência de contato em FETs de nanofloco de SnSe esfoliado. Além disso, enfatizamos que este estudo é o primeiro a relatar FETs baseados em nanofoco de SnSe esfoliados mecanicamente e estamos confiantes de que nossos FETs de nanofloco SnSe são muito promissores para dispositivos elétricos 2D, bem como para aplicações de coleta de energia, incluindo geração futura de termoeletricidade .

Nanomateriais

- Transistores, efeito de campo de junção (JFET)

- Transistores, efeito de campo de porta isolada (IGFET ou MOSFET)

- Transistores de efeito de campo de junção

- Transistores de efeito de campo de porta isolada (MOSFET)

- Introdução aos transistores de efeito de campo de junção (JFET)

- Introdução aos transistores de efeito de campo de porta isolada

- Espaçadores de ar para chips de 10 nm

- Um salto nanométrico para trilhões de transistores

- Aprendizagem não supervisionada com neurônios artificiais

- Efeito do tratamento de recozimento in situ na mobilidade e morfologia de transistores de efeito de campo orgânico baseados em TIPS-Pentaceno