Registradores de deslocamento:Conversão de entrada paralela, saída de série (PISO)

Os registradores de deslocamento de entrada / saída paralela fazem tudo o que os registradores de deslocamento de entrada / saída serial anteriores fazem mais os dados de entrada para todos os estágios simultaneamente.

O registrador de deslocamento de entrada / saída em paralelo armazena dados, os desloca relógio por relógio e os atrasa pelo número de estágios vezes o período do relógio.

Além disso, a entrada paralela / saída serial realmente significa que podemos carregar dados em paralelo em todos os estágios antes que qualquer mudança comece.

Esta é uma maneira de converter dados de um paralelo formato para um serial formato. Por formato paralelo, queremos dizer que os bits de dados estão presentes simultaneamente em fios individuais, um para cada bit de dados conforme mostrado abaixo.

Por formato serial, queremos dizer que os bits de dados são apresentados sequencialmente no tempo em um único fio ou circuito, como no caso da “saída de dados” no diagrama de blocos abaixo.

Abaixo, examinamos de perto os detalhes internos de um registrador de deslocamento de entrada / saída serial de 3 estágios.

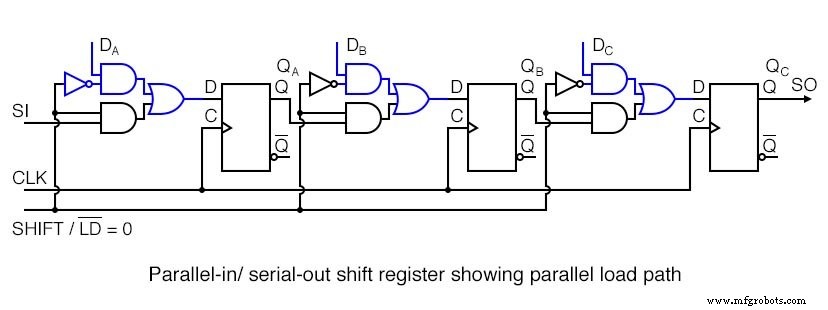

Um estágio consiste em um tipo D Flip-Flop para armazenamento e um seletor AND-OR para determinar se os dados serão carregados em paralelo ou se os dados armazenados serão deslocados para a direita.

Em geral, esses elementos serão replicados pelo número de etapas necessárias. Mostramos três estágios devido a limitações de espaço.

Quatro, oito ou dezesseis bits são normais para peças reais.

Acima, mostramos o caminho de carga paralelo quando SHIFT / LD 'é lógico baixo. As portas NAND superiores atendendo a D A D B D C estão ativados, passando dados para as entradas D do tipo D Flip-flops Q A Q B D C respectivamente.

Na próxima transição positiva do clock, os dados serão cronometrados de D a Q dos três FFs. Três bits de dados serão carregados em Q A Q B D C ao mesmo tempo.

O tipo de carga paralela que acabamos de descrever, em que os dados são carregados em um pulso de clock é conhecido como carga síncrona porque o carregamento de dados é sincronizado com o relógio.

Isso precisa ser diferenciado de carga assíncrona onde o carregamento é controlado pelos pinos predefinidos e transparentes dos flip-flops que não requerem o relógio.

Apenas um desses métodos de carga é usado em um dispositivo individual, sendo a carga síncrona mais comum em dispositivos mais novos.

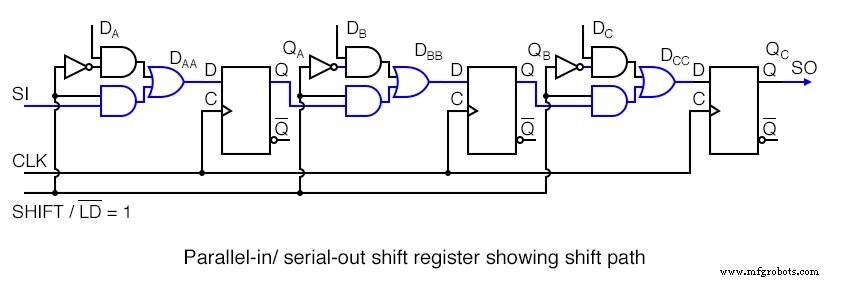

O caminho de mudança é mostrado acima quando SHIFT / LD 'é lógico alto. As portas AND inferiores dos pares que alimentam a porta OR são habilitadas, dando-nos uma conexão de registro de deslocamento de SI para D A , Q A para D B , Q B para D C , Q C para então. Os pulsos do relógio farão com que os dados sejam deslocados para a direita para SO em pulsos sucessivos.

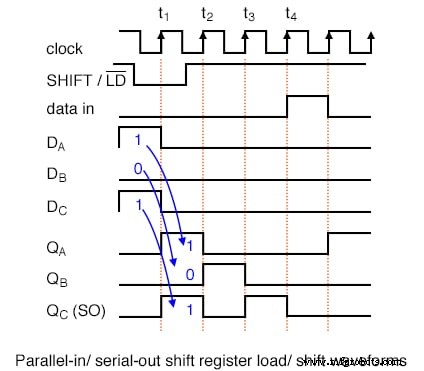

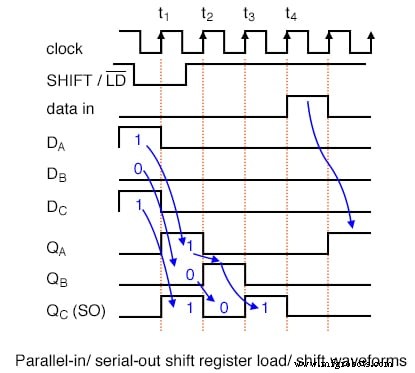

As formas de onda abaixo mostram o carregamento paralelo de três bits de dados e o deslocamento serial desses dados. Dados paralelos em D A D B D C é convertido em dados seriais no SO.

O que descrevemos anteriormente com palavras para carregamento e deslocamento paralelo agora está definido como formas de onda acima.

Como exemplo, apresentamos 101 às entradas paralelas D AA D BB D CC . Em seguida, o SHIFT / LD 'fica baixo, permitindo o carregamento de dados em oposição à mudança de dados.

Ele precisa estar baixo um pouco antes e depois do pulso do relógio devido aos requisitos de configuração e retenção. É consideravelmente mais largo do que deveria ser.

Porém, com a lógica síncrona é conveniente torná-la ampla. Poderíamos ter tornado o baixo SHIFT / LD 'ativo com quase dois clocks de largura, baixo quase um clock antes de t 1 e volte bem antes de t 3 .

O fator importante é que ele precisa estar baixo em todo o tempo t 1 para habilitar o carregamento paralelo dos dados pelo relógio.

Observe que em t 1 os dados 101 em D A D B D C é cronometrado de D a Q dos flip-flops como mostrado em Q A Q B Q C no tempo t 1 .

Este é o carregamento paralelo dos dados síncronos com o relógio.

Agora que os dados estão carregados, podemos deslocá-los, desde que SHIFT / LD ’esteja alto para permitir a mudança, que é anterior a t 2 .

Em t 2 os dados 0 em Q C é deslocado para fora do SO, que é o mesmo que o Q C forma de onda. Ele é deslocado para outro circuito integrado ou perdido se não houver nada conectado ao SO.

Os dados em Q B , um 0 é deslocado para Q C . O 1 em Q A é deslocado para Q B . Com “dados em” um 0 , Q A torna-se 0 . Após t 2 , Q A Q B Q C = 010 .

Após t 3 , Q A Q B Q C = 001 . Este 1 , que estava originalmente presente em Q A após t 1 , agora está presente em SO e Q C .

O último bit de dados é deslocado para um circuito integrado externo, se houver. Após t 4 todos os dados da carga paralela foram perdidos.

No relógio t 5 mostramos a mudança de um dado 1 presente no SI, entrada serial.

P:Por que fornecer pinos SI e SO em um registro de deslocamento?

R:Essas conexões nos permitem colocar estágios de registro de deslocamento em cascata para fornecer deslocadores maiores do que os disponíveis em um único pacote de IC (Circuito Integrado). Eles também permitem conexões seriais de e para outros ICs, como microprocessadores.

Vamos dar uma olhada mais de perto nos registradores de deslocamento de entrada / saída serial disponíveis como circuitos integrados, cortesia da Texas Instruments.

Para obter as folhas de dados completas do dispositivo, siga estes links.

Dispositivos de entrada paralela / saída serial

- SN74ALS166 entrada paralela / saída serial registrador de deslocamento de 8 bits, carga síncrona

- SN74ALS165 paralelo de entrada / saída serial de registro de deslocamento de 8 bits, carga assíncrona

- CD4014B com entrada paralela / saída serial registrador de deslocamento de 8 bits, carga síncrona

- SN74LS647 paralelo de entrada / saída serial registrador de deslocamento de 16 bits, carga síncrona

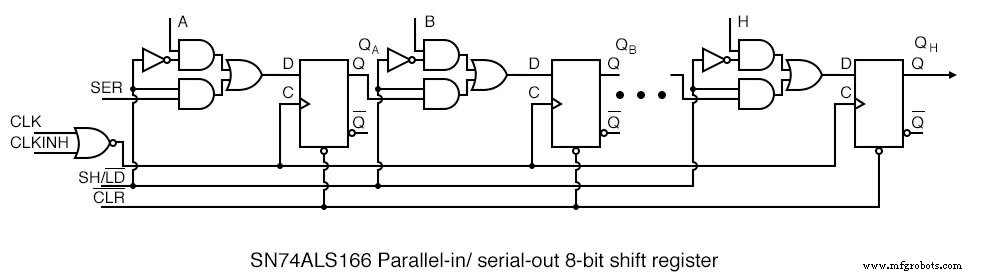

O SN74ALS166 mostrado acima é a correspondência mais próxima de uma peça real aos números anteriores do shifter de entrada paralela / saída em série.

Notemos as pequenas alterações em nossa figura acima. Em primeiro lugar, existem 8 estágios. Mostramos apenas três.

Todos os 8 estágios são mostrados na folha de dados disponível no link acima. O fabricante rotula as entradas de dados A, B, C e assim por diante para H.

O controle SHIFT / LOAD é denominado SH / LD ’. É uma abreviatura de nossa terminologia anterior, mas funciona da mesma forma:carga paralela se for baixa, deslocamento se for alta.

A entrada de deslocamento (entrada de dados seriais) é SER no ALS166 em vez de SI. O relógio CLK é controlado por um sinal de inibição, CLKINH.

Se CLKINH estiver alto, o relógio é inibido ou desabilitado. Caso contrário, esta “parte real” é a mesma que examinamos em detalhes.

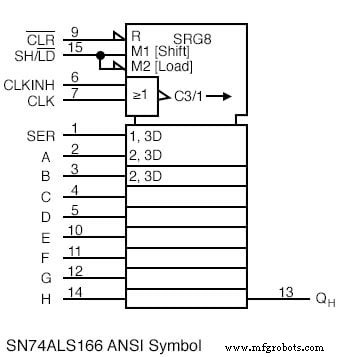

Acima está o símbolo ANSI (American National Standards Institute) para o SN74ALS166 conforme fornecido na folha de dados.

Uma vez que sabemos como a peça funciona, é conveniente ocultar os detalhes dentro de um símbolo. Existem muitas formas gerais de símbolos.

A vantagem do símbolo ANSI é que os rótulos fornecem dicas sobre como a peça funciona.

O grande bloco entalhado na parte superior do ‘74ASL166 é a seção de controle do símbolo ANSI. Há uma reinicialização indicada por R .

Existem três sinais de controle: M1 (Shift), M2 (Carga) e C3 / 1 (seta) (relógio inibido). O relógio tem duas funções.

Primeiro, C3 para deslocar dados paralelos sempre que um prefixo de 3 aparecer. Em segundo lugar, sempre que M1 é afirmado, conforme indicado pelo 1 de C3 / 1 (seta) , os dados são deslocados conforme indicado pela seta apontando para a direita.

A barra (/) é um separador entre essas duas funções. Os estágios de 8 turnos, conforme indicado pelo título SRG8 , são identificados pelas entradas externas A, B, C, para H .

O 2, 3D interno indica que os dados, D , é controlado por M2 [Carregar] e C3 relógio. Neste caso, podemos concluir que os dados paralelos são carregados de forma síncrona com o relógio C3 .

O estágio superior em A é um bloco mais largo do que os outros para acomodar a entrada SER .

A legenda 1, 3D implica que SER é controlado por M1 [Shift] e C3 relógio. Assim, esperamos registrar dados em SER ao deslocar em oposição ao carregamento paralelo.

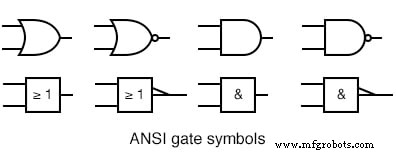

A porta básica ANSI / IEEE símbolos retangulares são fornecidos acima para comparação com os símbolos de forma mais familiares para que possamos decifrar o significado da simbologia associada ao CLKIN H e CLK pinos no símbolo ANSI SN74ALS166 anterior.

O CLK e CLKINH alimentam um OU portão no símbolo SN74ALS166 ANSI. OU é indicado por => no símbolo de inserção retangular.

O triângulo longo na saída indica um relógio. Se houvesse uma bolha com a seta, isso indicaria uma mudança na transição negativa do clock (de alto para baixo).

Como não há bolha com a seta do clock, o registro muda na transição positiva (transição de baixo para alto).

A seta longa, após a legenda C3 / 1 apontar para a direita indica deslocamento para a direita, que é o símbolo para baixo.

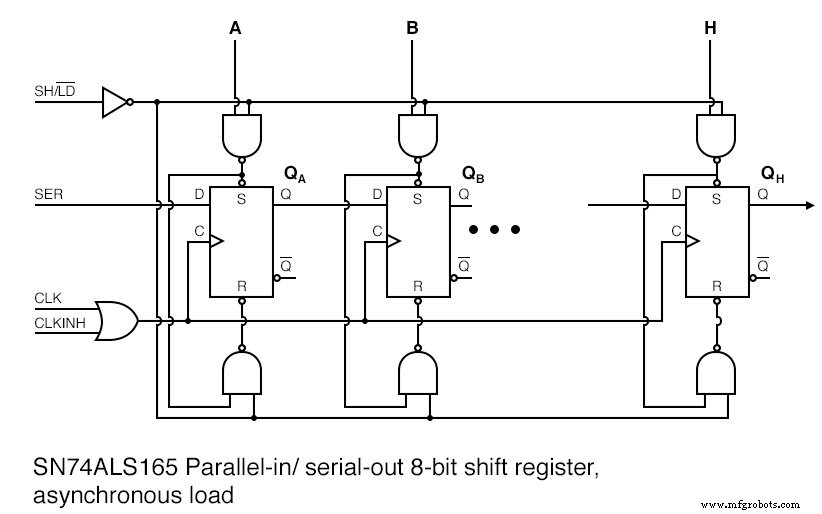

Parte da lógica interna do SN74ALS165 paralelo-in / serial-out, registro de deslocamento de carga assíncrona é reproduzida da folha de dados acima.

Consulte o link no início desta seção para o diagrama completo. Não examinamos o carregamento assíncrono de dados até este ponto.

Em primeiro lugar, o carregamento é realizado pela aplicação de sinais apropriados ao Conjunto (predefinido) e Redefinir (limpar) entradas dos flip-flops.

O NAND superior portões alimentam o Conjunto pinos dos FFs e também em cascata para o NAND inferior portão alimentando o Reiniciar pinos dos FFs.

O menor NAND gate inverte o sinal indo de Set fixar em Redefinir alfinete.

Primeiro, SH / LD ’ deve ser puxado para baixo para ativar o NAND superior e inferior portões.

Se SH / LD ’ estavam em um alto lógico em vez disso, o inversor alimenta uma lógica baixa para todos os NAND portões forçariam um alto para fora, liberando o "ativo mínimo" Definir e Redefinir pinos de todos os FFs.

Não haveria possibilidade de carregar os FFs.

Com SH / LD ’ mantido baixo , podemos alimentar, por exemplo, um dados 1 para a entrada paralela A , que se inverte para zero no NAND superior saída da porta, definindo FF Q A para um 1 .

O 0 no Set pino é alimentado para o NAND inferior portão onde é invertido para um 1 , liberando o Reset pino de Q A .

Assim, um dado A =1 define Q A =1 . Como nada disso exigia o relógio, o carregamento é assíncrono em relação ao relógio.

Usamos um registrador de deslocamento de carregamento assíncrono se não podemos esperar por um relógio para carregar dados em paralelo, ou se for inconveniente gerar um único pulso de relógio.

A única diferença na alimentação de dados 0 para a entrada paralela A é que ele se inverte para um 1 fora do portão superior liberando Set .

Este 1 em Set é invertido para um 0 no portão inferior, puxando Reiniciar para um baixo , que redefine Q A =0 .

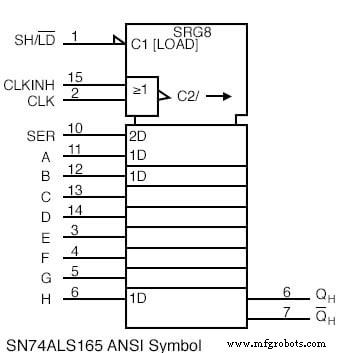

O símbolo ANSI para o SN74ALS166 acima tem dois controles internos C1 [LOAD] e C2 relógio do OU função de ( CLKINH, CLK )

SRG8 diz shifter de 8 estágios. A seta depois de C2 indica o deslocamento para a direita ou para baixo. SER entrada é uma função do relógio, conforme indicado pelo rótulo interno 2D .

As entradas de dados paralelas A, B, C para H são uma função de C1 [CARGA], indicado pelo rótulo interno 1D .

C1 é afirmado quando sh / LD ’=0 devido ao inversor de meia seta na entrada.

Compare isso com o controle das entradas de dados paralelas pelo relógio do ANSI SN75ALS166 síncrono anterior. Observe as diferenças nas etiquetas de dados ANSI.

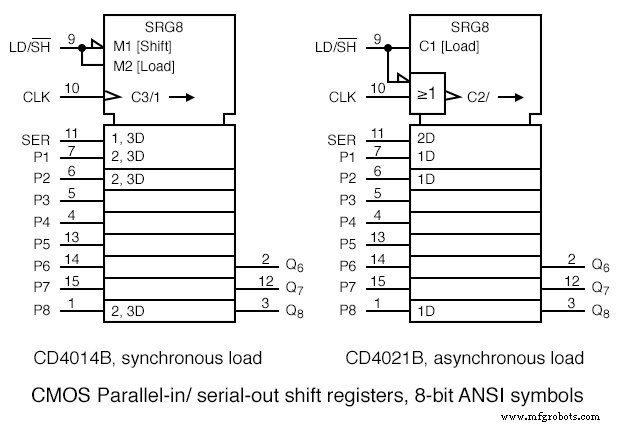

No CD4014B acima, M1 é afirmado quando LD / SH ’=0 . M2 é afirmado quando LD / SH ’=1 .

Relógio C3 / 1 é usado para dados de carregamento paralelo em 2, 3D quando M2 está ativo conforme indicado por 2,3 rótulos de prefixo.

Pins P3 para P7 são entendidos como tendo o smae interno 2,3 etiquetas de prefixo como P2 e P8 . Em SER , o 1,3D prefixo implica que M1 e relógio C3 são necessários para inserir dados seriais.

O deslocamento para a direita ocorre quando M1 ativo é indicado por 1 na seta C3 / 1 .

O CD4021B é uma parte semelhante, exceto para carregamento paralelo assíncrono de dados, conforme implícito pela falta de qualquer 2 prefixo no rótulo de dados 1D para os pinos P1, P2, a P8.

Claro, prefixo 2 no rótulo 2D na entrada SER diz que os dados são cronometrados neste pino. O OU a inserção do portão mostra que o relógio é controlado por LD / SH ’ .

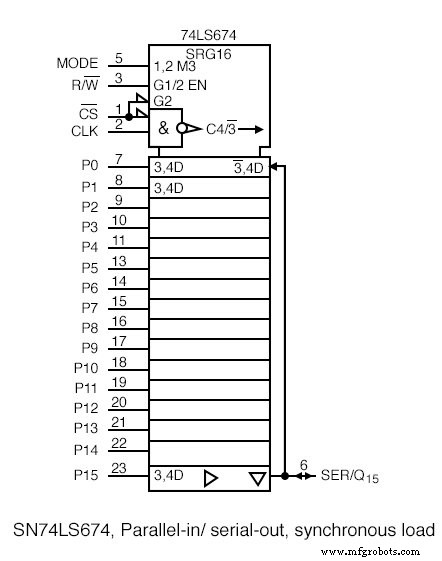

O rótulo interno SN74LS674 acima SRG 16 indica registrador de deslocamento de 16 bits.

O MODO a entrada para a seção de controle na parte superior do símbolo é identificada como 1,2 M3 . M3 interno é uma função de entrada MODE e G1 e G2 conforme indicado pelo 1,2 precedendo M3 .

O rótulo de base G indica um E função de qualquer G entradas. Insira R / W ’ é identificado internamente como G1 / 2 EN .

Este é um habilitar EN (controlado por G1 E G2 ) para dispositivos tristate usados em outras partes do símbolo.

Observamos que CS ’ no (pino 1) é interno G2 . Chip select CS ’ também é AND ed com a entrada CLK para fornecer o relógio interno C4 .

A bolha dentro da seta do relógio indica que a atividade está na transição negativa (transição alta para baixa).

A barra (/) é um separador que implica duas funções para o relógio. Antes da barra, C4 indica o controle de qualquer coisa com um prefixo de 4 .

Após a barra, o 3 ’(seta) indica mudança. O 3 ’ de C4 / 3 ’ implica em deslocamento quando M3 é desabilitado ( MODE =0 ) A seta longa indica deslocamento para a direita (para baixo).

Descendo abaixo da seção de controle para a seção de dados, temos entradas externas P0-P15 , pinos (7-11, 13-23).

O prefixo 3,4 do rótulo interno 3,4D indica que M3 e o relógio C4 controlar o carregamento de dados paralelos.

O D significa Dados. Presume-se que esse rótulo se aplique a todas as entradas paralelas, embora não seja explicitamente escrito.

Localize o rótulo 3 ’, 4D à direita do P0 (pin7) estágio. O complementado- 3 indica que M3 =MODE =0 entradas (turnos) SER / Q 15 (pin5) na hora do relógio, ( 4 de 3 ’, 4D) correspondendo ao relógio C4 .

Em outras palavras, com MODE =0 , transferimos os dados para Q 0 da entrada serial (pino 6). Todos os outros estágios mudam para a direita (para baixo) no horário do relógio.

Movendo-se para a parte inferior do símbolo, o triângulo apontando para a direita indica um buffer entre Q e o pino de saída.

O triângulo apontando para baixo indica um dispositivo tri-state. Afirmamos anteriormente que o triestato é controlado ativando EN , que na verdade é G1 E G2 da seção de controle.

Se R / W =0 , o tri-state é desabilitado e podemos mudar os dados para Q 0 via SER (pino 6), um detalhe que omitimos acima. Na verdade, precisamos de MODE =0, R / W ’=0, CS’ =0

A lógica interna do SN74LS674 e uma tabela resumindo o funcionamento dos sinais de controle estão disponíveis no link da lista bullet, topo da seção.

Se R / W ’=1 , o tristate está ativado, Q 15 desloca SER / Q 15 (pino 6) e recircula para o Q 0 estágio através do fio direito para 3 ', 4D .

Presumimos que CS 'estava baixo, dando-nos o relógio C4 / 3' e G2 para EN capaz o tri-state.

Aplicações práticas

Uma aplicação de um registro de deslocamento de entrada paralela / saída serial é ler os dados em um microprocessador.

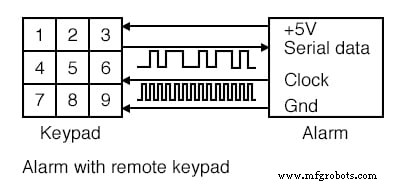

O alarme acima é controlado por um teclado remoto. A caixa de alarme fornece + 5 V e aterramento para o teclado remoto para alimentá-lo.

O alarme lê o teclado remoto a cada poucas dezenas de milissegundos, enviando relógios de deslocamento para o teclado, que retorna dados seriais que mostram o status das teclas por meio de um registrador de deslocamento de entrada / saída serial.

Assim, lemos nove interruptores principais com quatro fios. Quantos fios seriam necessários se tivéssemos que executar um circuito para cada uma das nove chaves?

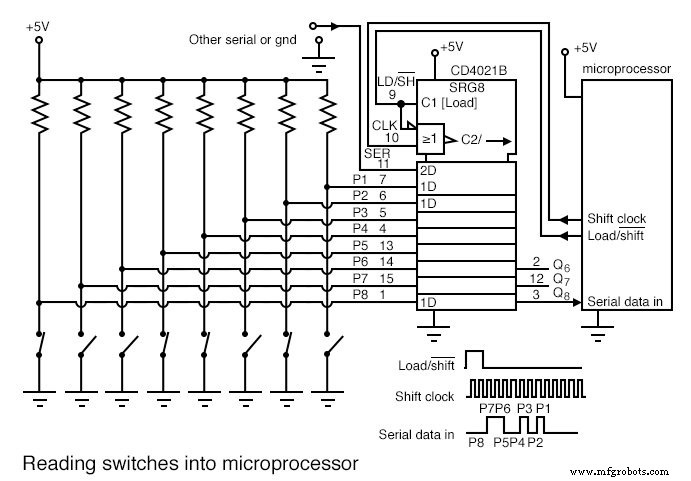

Uma aplicação prática de um shift register de entrada paralela / saída serial é ler muitos fechamentos de chave em um microprocessador em apenas alguns pinos.

Alguns microprocessadores low end possuem apenas 6 pinos de E / S (entrada / saída) disponíveis em um pacote de 8 pinos.

Ou podemos ter usado a maioria dos pinos em um pacote de 84 pinos. Podemos querer reduzir o número de fios que passam por uma placa de circuito, máquina, veículo ou prédio.

Isso aumentará a confiabilidade do nosso sistema. Foi relatado que os fabricantes que reduziram o número de fios em um automóvel produzem um produto mais confiável.

Em qualquer caso, apenas três pinos de microprocessador são necessários para ler dados de 8 bits dos switches na figura acima.

Escolhemos um dispositivo de carregamento assíncrono, o CD4021B, porque é mais fácil controlar o carregamento de dados sem ter que gerar um único clock de carregamento paralelo.

As entradas de dados paralelas do registrador de deslocamento são aumentadas para + 5 V com um resistor em cada entrada.

Se todos os interruptores estiverem abertos, todos 1 s serão carregados no registrador de deslocamento quando o microprocessador mover o LD / SH ’ alinhe de baixo para cima, depois volte para baixo em antecipação à mudança.

Qualquer fechamento de interruptor aplicará lógica 0 s às entradas paralelas correspondentes. O padrão de dados em P1-P7 será carregado em paralelo pelo LD / SH ’=1 gerado pelo software do microprocessador.

O microprocessador gera pulsos de deslocamento e lê um bit de dados para cada um dos 8 bits.

Este processo pode ser executado totalmente com software, ou microprocessadores maiores podem ter uma ou mais interfaces seriais para fazer a tarefa mais rapidamente com hardware.

Com LD / SH ’=0 , o microprocessador gera um 0 para 1 transição na linha do relógio de turno , em seguida, lê um bit de dados em Dados seriais em linha. Isso é repetido para todos os 8 bits.

O SER a linha do registrador de deslocamento pode ser conduzida por outro circuito CD4021B idêntico se mais contatos de comutação precisarem ser lidos.

Nesse caso, o microprocessador gera pulsos de 16 turnos. Mais provavelmente, ele será conduzido por algo compatível com esse formato de dados seriais, por exemplo, um conversor analógico para digital, um sensor de temperatura, um scanner de teclado, uma memória serial somente leitura.

Quanto aos fechos de interruptor, eles podem ser interruptores de limite no carro de uma máquina, um sensor de temperatura excessiva, um interruptor magnético de palheta, um interruptor de porta ou janela, um interruptor de pressão de ar ou água ou um interruptor óptico de estado sólido.

PLANILHAS RELACIONADAS:

- Planilha de registros de turnos

Tecnologia industrial