Influência do layout de PCB do desempenho de EMC do produto eletrônico

Terra em PCB

• Influência da Interferência de Código Comum no Sinal Interno da PCB

As linhas impressas internas da placa de circuito impresso (PCB) apresentam parâmetros parasitas relativos à placa de aterramento de referência e quando os sinais de função estão sendo transmitidos dentro da placa de circuito impresso, o mesmo nó equipotencial na mesma rede no circuito não é mais equipotencial. A corrente i dentro da placa começa no final da fonte, passa por uma série de portadoras e retorna para a fonte do sinal, formando um sinal. Além disso, i tende a fluir ao longo do caminho com baixa impedância, de modo que geralmente se mantém imutável com a estabilidade da impedância.

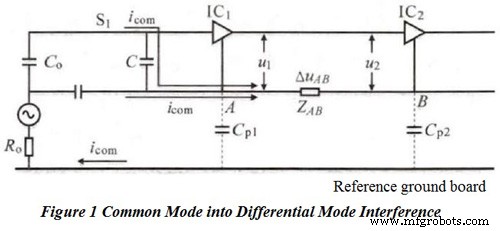

A Figura 1 indica o processo quando a interferência de modo comum é transformada em interferência de modo diferencial dentro do PCB. ed refere-se à corrente de modo diferencial dentro do fluxo de PCB enquanto icom refere-se à corrente de modo comum que começa fora do PCB e flui para o PCB através da placa de aterramento de referência ou começa a partir do interior do PCB e retorna para dentro do PCB através da placa de aterramento de referência. icom de alta frequência tem dois caminhos:o primeiro é do ponto A ao ponto B dentro do PCB começando pelo GND; o segundo é do ponto A ao ponto B começando na porta S1 para PCB dentro pela capacitância C. Impedância de terra ZAB leva à geração de ΔuAB , então quando o sinal normal é passado para IC2 , a deformação ocorrerá no sinal e a interferência de modo comum é transformada em interferência de modo diferencial, que produz influência no sinal normal com base na fórmula que é u2 =u1 -ΔuAB .

Portanto, assim que eucom entra no interior do PCB através da porta de E/S ou radiação espacial, a capacitância do filtro de modo diferencial nas linhas de sinal do PCB só pode pressionar o desvio de interferência para GND. O pré-requisito deste resultado é que GND é considerado como baixa impedância para refluxo de sinal e a corrente sempre flui na direção de baixa impedância.

• Chave de implementação do projeto EMC:impedância de aterramento na placa de circuito impresso

A razão para a geração de EMC por sinais de alta frequência reside no fato de que o nível de referência do sinal GND não consegue manter sua característica de baixa impedância. Com o aumento da impedância ZGND do nível de referência, a qualidade da transmissão do sinal também diminui. Para resolver o problema de interferência de alta frequência, métodos comuns são usados no projeto EMC, como filtro, terra e blindagem que estão intimamente conectados ao "terra".

O filtro pode ser considerado como capacitor para terra, com duas estruturas uma das quais é fazer o capacitor X conectado ao terra de referência do sinal e a outra é fazer o sinal conectado ao invólucro de metal pelo capacitor Y ou conexão de terra diferente dentro da PCB. A blindagem pode ser considerada como o resultado da expansão do PCB para o espaço. A finalidade do filtro ou blindagem é fazer com que a interferência de modo comum de alta frequência passe pelo bypass com baixa impedância, a fim de evitar o fluxo para o sinal de operação normal. Da mesma forma, todos esses métodos não funcionarão a menos que o solo tenha baixa impedância.

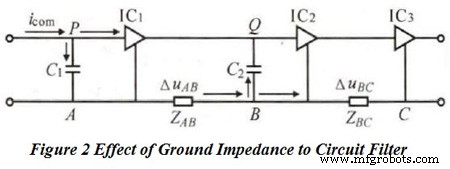

A Figura 2 indica o efeito da impedância de terra no filtro do circuito. icom flui de acordo com a sequência de IC1 →IC2 →IC1 e quando flui para o ponto P, icom fluirá em circuitos de ramificação de IC1 e C1 através do qual flui do ponto A para B. Se a impedância entre o ponto A e B, que é ZAB , é muito menor que a impedância entre o ponto P e IC1 . Neste momento, eucom flui do ponto P para A, IC1 filtro pode ser realizado. Quando eucom flui para o ponto B, ocorrerão circuitos de derivação que são B→C e B→Q. Se o layout do PCB não for bem controlado, a impedância entre o ponto B e C, que é ZBC , ZBC>>ZC2 +ZQ . ZQ refere-se à impedância entre o ponto Q e IC2 . icom flui para trás para IC2 porta de entrada através de C2 quando a capacitância que foi originalmente usada apenas para IC2 desempenha um papel na interferência de invasão de sinal.

Para fazer um nível de referência com baixa impedância, geralmente é projetado para ser uma superfície. De um modo geral, o condutor cuja relação comprimento-largura é inferior a 5 pode ser considerado como de baixa impedância no campo da engenharia. A impedância das linhas impressas não é determinada pelo seu grau de comprimento ou espessura. Nos princípios tradicionais de design de PCB, o aterramento de ponto único de circuito analógico é massivamente recomendado, de modo que o princípio de layout de PCB de aterramento de vários pontos de circuito digital e aterramento de mistura de circuito de módulo digital não é mais viável para lidar com problemas de EMC.

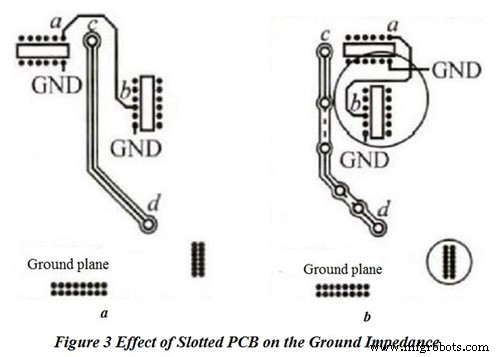

Como todos os fluxos de retorno de todos os sinais devem ser garantidos para apresentar um aterramento integrado com baixa impedância, placas de 4 camadas ou multicamadas com plano de aterramento integrado são capazes de atender ao requisito, enquanto placas únicas de baixo custo não são. Quando uma placa de camada dupla deve ser usada com base na limitação de custo, um plano de aterramento relativamente integrado deve ser projetado para sinais dentro da PCB. Na aplicação prática, a impedância de aterramento da placa de circuito impresso é influenciada tanto por sua forma quanto pelo fio de sinal através de furos, rachaduras e ranhuras. As Figuras 3a e 3b exibem, respectivamente, design de plano de terra de baixa impedância ruim e excelente.

Nesta figura, todos os componentes estão na parte frontal do PCB enquanto o plano de aterramento está na parte de trás. Os chips são conectados através de linhas impressas ab na frente e cd são linhas impressas na parte de trás. Sob a pressão da interferência de modo comum de alta frequência pelo exterior, o entalhe formado por cd levará ao aumento de ZGND de refluxo de linhas impressas. ZGND flutua no processo de transmissão do sinal, levando à baixa qualidade do sinal. Portanto, camadas de linhas impressas entre cd podem ser trocadas repetidamente através de furos no processo de design de layout de PCB para que ZGND será diminuído. Além disso, dois ICS com sinais sensíveis podem ser organizados juntos de modo a tornar o GND um plano de terra relativamente integrado localmente para garantir que o sinal não seja interferido no processo de transmissão do sinal. Preste atenção que os furos passantes não podem ser organizados com muita densidade, caso contrário, rachaduras no plano do solo também serão causadas, levando ao aumento de ZGND .

Projeto de empilhamento de PCBs

O design EMC é melhor para PCBs de 4 camadas. Do ponto de vista do EMS, tanto a blindagem metálica quanto a blindagem metálica de circuitos localmente sensíveis são capazes de resolver problemas de interferência. Do ponto de vista da EMI, às vezes as placas de 4 camadas não atendem ao requisito de limitação de emissão de radiação e o número de camadas deve ser aumentado, pois as placas de várias camadas podem fazer sinais com alta du /dt e di /dt garantem menor área de loop de sinal no processo de transmissão, proporcionando refluxo com baixa impedância para sinais de alta velocidade.

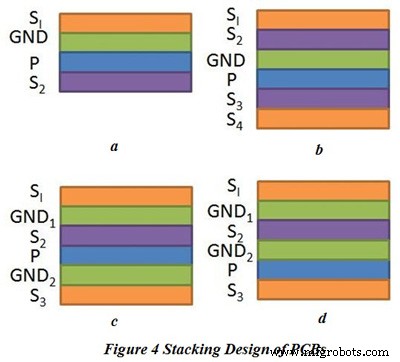

O princípio básico do projeto de empilhamento de PCB é organizar a camada de sinal de alta velocidade e o plano de potência adjacente ao plano de aterramento. A Figura 4 mostra o design de empilhamento de placas de 4 e 6 camadas. S1 na Figura 4a refere-se à camada de sinal de alta velocidade, enquanto a Figura 4b, 4c e 4d são três projetos de PCB de 6 camadas comuns.

Entre os 3 designs de PCB de 6 camadas, o design b é o pior e o S2 camada deve ser camada de sinal de alta velocidade. S2 camada no projeto c e d é a camada de sinal de alta velocidade. O design c é o melhor porque cada camada de sinal é adjacente ao plano de terra para garantir o caminho de retorno de sinal mais curto e S2 e as camadas P são protegidas por GND1 e GND2 . Comparado com o design c, S3 no projeto d está longe da camada GND e P só pode atingir o efeito de lado único em vez do efeito de lado duplo causado pelo projeto c.

Antena equivalente em PCBs

A função fundamental da antena é irradiar e receber ondas de rádio sem fio. No processo de radiação, a corrente de alta frequência pode ser transformada em onda eletromagnética; no processo de recepção, a onda eletromagnética é transformada em corrente de alta frequência. A radiação no campo EMC refere-se principalmente à radiação de campo distante. A formação da antena depende de duas condições básicas:fonte de sinal de RF e certo comprimento de condutores conectados à fonte de sinal de RF. No campo da engenharia, acredita-se que o efeito da antena surgirá quando o comprimento do condutor estiver de acordo com a fórmula que é l=λ/20. Quando l=(λ/4)n, o efeito da antena é o maior com n como número natural.

Quando o sinal está sendo transmitido dentro do PCB, o loop interno tem o mesmo efeito com a antena de loop. Quanto maior a área do loop, maior será o efeito da antena. O controle estrito do circuito do PCB pode efetivamente interromper a interferência do modo diferencial, o que é viável na prática. No entanto, o aumento do comprimento das linhas impressas causará um efeito óbvio de antena de haste, de modo que o comprimento dos sinais de interconexão deve ser reduzido o máximo possível no processo de layout da placa de circuito impresso.

Quando relativamente alto ZGND ocorre no caminho de retorno de sinais du/dt altos transmitidos dentro do PCB, fonte de driver de modo comum ucom acontecerá com icom passando por ZGND , juntamente com linhas impressas conectadas ou estábulos de E/S, que podem irradiar para fora.

Se os PCBs forem relativamente pequenos em tamanho, as linhas impressas internas não podem atingir o requisito de radiação da antena devido à limitação de comprimento. Sob esta condição, o cabo de E/S pode ser considerado como a expansão das linhas impressas, o requisito de radiação pode ser atendido. Mesmo que não exista uma conexão direta com E/S estável, o acoplamento de diafonia deve ser interrompido entre os cabos de E/S.

Crosstalk dentro do PCB e seus remédios

• Acoplamento entre linhas impressas de PCB e terra de referência

Como a EMC discute principalmente sinais de modo comum de alta frequência, os parâmetros de distribuição não podem ser evitados dentro e fora do PCB. O acoplamento capacitivo ocorre entre a PCB e o terra de referência cuja capacitância distribuída é composta pela capacitância de placa e capacitância natural dentro do menor espaço. A capacitância da placa é diretamente proporcional ao tamanho do PCB e indiretamente proporcional à distância entre o PCB e o terra. A capacitância natural dentro do menor espaço é diretamente proporcional ao diâmetro equivalente das linhas impressas dentro do PCB. Portanto, não importa onde o PCB seja colocado, mesmo longe do chão no infinito, a capacitância distribuída sempre existe entre as linhas impressas internas e o terra. Em um PCB, a capacitância distribuída de um plano GND relativamente integrado para a placa de aterramento de referência é de aproximadamente 10pF e a capacitância distribuída das linhas impressas internas para a placa de aterramento de referência está aproximadamente na faixa de 0,001pF a 0,1pF ou inferior. A capacitância distribuída das linhas impressas no centro do PCB é muito menor do que a das linhas impressas na borda do PCB.

• Acoplamento dentro do PCB

uma. Teoria do acoplamento dentro do PCB e sua influência no sinal

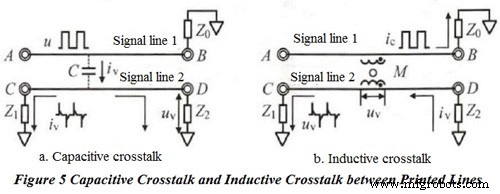

O acoplamento dentro do PCB consiste em acoplamento capacitivo e acoplamento indutivo cuja teoria é apresentada na Figura 5.

Nesta figura, tanto AB quanto CD são linhas impressas paralelas com um pequeno espaço entre duas linhas. Z0 refere-se à portadora da linha de sinal 1 enquanto Z1 e Z2 referem-se respectivamente às portadoras da linha de sinal 2. Na Figura 5a, quando a tensão de pico do sinal na linha impressa AB é u, o tempo de subida do sinal é Δt e a frequência angular é ω, a tensão de Z2 será uv =[Z1 Z2 /(Z1 +Z2 )]cΔu/Δt. Embora c tem um valor muito baixo, o valor de Δu/dt pode ser muito alto e seu produto não pode ser evitado. Na Figura 5b, quando a corrente de pico do sinal em AB é Ic , o tempo de subida do sinal é Δt e a frequência angular é ω, a indutância mútua m entre 2 linhas impressas passará por CD na qual a tensão induzida é uv =mωic . Embora o valor de m seja tão pequeno, a frequência do sinal pode ser aumentada. Portanto, seu produto não pode ser evitado.

Como resultado, tanto o acoplamento capacitivo quanto o acoplamento indutivo estão relacionados com o parâmetro distribuído de duas linhas impressas c ou m. Durante o layout do PCB, os valores de c e m podem ser reduzidos aumentando a distância entre as linhas paralelas. No circuito prático, o acoplamento capacitivo é responsável pela maior parte do circuito digital e quando o plano da PCB não é suave ou existe fenda ou rachadura, a diafonia indutiva terá mais influência do que a diafonia capacitiva. No entanto, quando a área do PCB é limitada, a diafonia não pode ser tratada apenas aumentando a distância entre linhas paralelas. Para manter os menores parâmetros distribuídos entre duas linhas paralelas adjacentes, o desenho do plano integrado deve ser disposto na área projetiva e é melhor ter camadas de solo na parte superior e inferior.

b. Influência do fio terra blindado para reduzir a diafonia

O grau de crosstalk é determinado por muitos elementos, como frequência do sinal, tempo de borda de subida do sinal, distância entre as linhas de sinal, porta de acionamento e recursos elétricos da porta de recepção e número de camadas de PCB. A diafonia pode ser diminuída definindo o plano de aterramento integrado sob as linhas impressas e o fio de aterramento blindado pode ser adicionado entre os sinais.

No processo de layout de PCB, dois aspectos podem ser benéficos para interromper a diafonia. Em primeiro lugar, o circuito interno sensível e o circuito externo devem ser interrompidos. Em segundo lugar, a diafonia entre o circuito interno ou o circuito de ruído e outros sinais devem ser interrompidos. No layout prático do PCB, o teste detalhado deve ser realizado na mesma camada ou entre diferentes camadas no PCB para detectar se existe ou não risco de crosstalk.

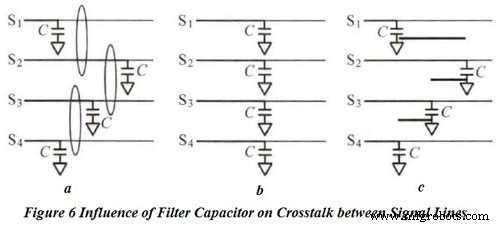

Durante o procedimento de layout de PCB, algumas linhas de sinal com o mesmo atributo devem seguir o roteamento de mesmo tempo e mesma direção com densidade. Se a limitação do espaço do PCB leva ao fato de que os componentes do filtro não podem ser colocados na mesma linha, a diafonia entre os sinais tende a ser despertada. Esta situação é indicada na Figura 6 abaixo.

c. Influência do fio terra blindado no efeito de borda

Quando linhas de sinal altamente sensíveis ou linhas de sinal com alto du/dt, di/dt são dispostas ao longo da borda da PCB, elas sofrerão mais risco de EMC do que aquelas dispostas no centro da PCB. É mais fácil para as linhas de sinal de borda receber interferência de alta frequência ou radiação externa por capacitância parasita maior.

Sob a limitação da área do PCB, é extremamente difícil fazer o layout do PCB de acordo com os princípios 20H no arquivo de design. "Pacote" pode ser usado para reduzir a interferência e a radiação externa. As linhas de pacotes não precisam atender a requisitos específicos, como espessura e forma. Normalmente, quando uma linha de sinal está muito próxima da borda do PCB para a placa de cobre, uma linha de aterramento na faixa de 7 a 10 mils pode ser adicionada como blindagem.

d. Interferência mútua entre circuitos digitais e analógicos

Quando um PCB mantém um circuito digital de alta velocidade e sinais analógicos de baixo nível, a diafonia geralmente é gerada para sinais analógicos por ruído digital sob um layout de PCB ruim. A interferência mútua entre circuitos digitais e analógicos é causada pelos seguintes motivos. Em primeiro lugar, o ruído de diafonia é causado pela capacitância parasita e indutância parasita. Em segundo lugar, o mau desacoplamento da ondulação de potência e da potência do chip digital levará ao ruído de potência. Em terceiro lugar, a impedância de aterramento e o local de aterramento do sistema causam ruído. O problema do ruído deve ser tratado na ordem de potência, sinal e terra.

Recursos úteis:

• A introdução mais abrangente de ferramentas automatizadas EMI e EMC

• Garantindo o sucesso inicial no projeto EMC de PCB

• Regras de projeto de particionamento de PCB para aprimoramento de EMC

• PCB Projeto para Circuito de Radiofrequência e Compatibilidade Eletromagnética

• Três Considerações de Projeto Garantindo EMC de PCB de Laptop

• Serviço de Fabricação de PCB Completo da PCBCart - Várias opções de valor agregado

• Serviço Avançado de Montagem de PCB da PCBCart - Comece a partir de 1 peça

Tecnologia industrial

- Noções básicas de layout de PCB

- Software de layout de PCB

- Considerações de layout de PCB

- Guia rápido para iniciantes sobre layout de PCB

- Considerações de projeto de impedância para PCB flexível

- Dicas de layout de alta velocidade

- Método de supressão de reflexão de sinal em layout de PCB de alta velocidade

- Garantindo o sucesso inicial no projeto de PCB EMC

- Controle de impedância de vias e sua influência na integridade do sinal no projeto de PCB

- Diretrizes imperdíveis de layout de PCB para engenheiros