Controle de impedância no projeto de PCB de circuito digital de alta velocidade

As tecnologias de controle de impedância são muito importantes no projeto de circuitos digitais de alta velocidade, nos quais métodos eficazes devem ser adotados para garantir o excelente desempenho de PCBs de alta velocidade.

Cálculo de impedância e controle de impedância de linhas de transmissão de circuito de alta velocidade em PCB

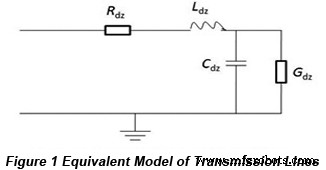

• Modelo Equivalente em Linhas de Transmissão

A Figura 1 mostra o efeito equivalente de linhas de transmissão em PCBs, que é uma estrutura que inclui capacitor tandem e múltiplo, resistor e indutor (modelo RLGC).

O valor típico da resistência tandem está na faixa de 0,25 a 0,55 ohms/pé e o valor da resistência de vários resistores geralmente permanece bastante alto. Com resistência parasita, capacitância e indutância adicionadas em linhas de transmissão PCB, a impedância geral nas linhas de transmissão é referida como impedância característica (Z0 ). O valor da impedância característica é relativamente pequeno na condição de que o diâmetro da linha seja grande, a linha esteja próxima da potência/terra ou a constante dielétrica seja alta. A Figura 3 mostra o modelo equivalente da linha de transmissão com comprimento dz, a partir do qual a impedância característica da linha de transmissão pode ser deduzida como fórmula: . Nesta fórmula, L se refere à indutância de cada unidade de comprimento na linha de transmissão, enquanto C se refere à capacitância de cada unidade de comprimento na linha de transmissão.

. Nesta fórmula, L se refere à indutância de cada unidade de comprimento na linha de transmissão, enquanto C se refere à capacitância de cada unidade de comprimento na linha de transmissão.

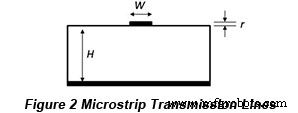

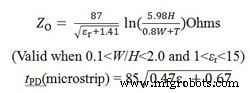

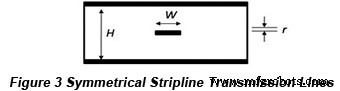

• Fórmula de cálculo de impedância e atraso de linhas de transmissão em PCB

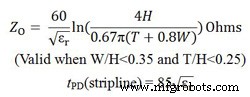

| Linhas de transmissão em PCB | Fórmula de cálculo de impedância e atraso |

|  |

|  |

Nas fórmulas acima, Z0 refere-se à impedância (Ohms), W refere-se à largura das linhas (polegadas), T refere-se à espessura das linhas (polegadas), H refere-se à distância ao solo (polegadas), refere-se à constante dielétrica relativa do substrato, e tPD refere-se ao tempo de atraso (ps/polegada).

• Regras de Layout de Controle de Impedância de Linhas de Transmissão

Com base na análise acima, o atraso unitário de impedância e sinal não é relativo à frequência dos sinais, mas está relacionado com a estrutura da placa, a constante dielétrica relativa do material da placa e os atributos físicos do roteamento. Esta conclusão é extremamente importante para entender o PCB de alta velocidade e para o projeto de PCB de alta velocidade. Além disso, a velocidade de transmissão da linha de transmissão de sinal na camada externa é muito mais rápida do que na camada interna, portanto, esses elementos devem ser levados em consideração para o arranjo do layout das linhas principais.

O controle de impedância é a premissa significativa para a implementação da transmissão de sinal. No entanto, de acordo com a estrutura da placa e a fórmula de cálculo de impedância das linhas de transmissão, a impedância depende apenas do material do PCB e da estrutura da camada do PCB com a largura da linha e os recursos de roteamento inalterados para a mesma linha. Portanto, a impedância de uma linha não mudará em diferentes camadas de PCB, o que não é permitido no projeto de circuitos de alta velocidade.

Um PCB de alta velocidade com alta densidade é projetado para este artigo e a maioria dos sinais a bordo possui requisitos de impedância. Por exemplo, a linha de sinal CPCI deve ter uma impedância de 65ohms, sinal diferencial de 100ohms e outros sinais de 50ohms cada. De acordo com o espaço de roteamento do PCB, um roteamento de pelo menos dez camadas deve ser usado e um plano de design do PCB de 16 camadas é determinado.

Uma vez que a espessura total da placa não pode ultrapassar os 2mm, existem algumas dificuldades em termos de empilhamento com alguns problemas considerados:

1). Cada camada de sinal possui planos de imagem adjacentes para proteger a impedância e a qualidade do sinal.

2). Cada plano de energia tem uma camada de terra completa próxima a eles para que o desempenho da energia possa ser bem garantido.

3). O empilhamento do tabuleiro requer equilíbrio, evitando-se o empenamento do tabuleiro.

A constante dielétrica do meio é definida como 4,3. Com base no projeto de empilhamento acima, a largura da linha e a distância entre as linhas devem ser definidas de acordo com o resultado do cálculo para garantir o requisito de impedância do sinal. A largura da linha é obtida como o seguinte resultado:

1). A largura da linha de sinal na camada de superfície é de 5 mils com sua impedância de 58,7 Ohms.

2). A largura da linha de sinal CPCI na camada superficial é de 4,5 mils com sua impedância de 61,7 Ohms.

3). A largura da linha de sinal na camada interna é de 4,5 mils com sua impedância de 50,2 Ohms.

4). A largura das linhas na área BGA na camada interna e na camada superficial é de 4 mils com impedância da camada superficial de 64,6 Ohms e impedância da camada interna de 52,7 Ohms.

5). A largura da linha diferencial de microfita na camada interna é de 5mils com a distância entre as linhas de 6mils e impedância de 100,54Ohms.

6). A largura da linha diferencial stripline na camada interna é de 4,5 mils com a distância entre as linhas de 10 mils e impedância de 96,6 Ohms.

A distância entre as linhas é definida da seguinte forma:

1). A distância entre as linhas de sinal (5mils) na camada superficial é de 5,0mils.

2). A distância entre as linhas de sinal CPCI (4,5 mils) na camada superficial é de 9,0 mils.

3).. A distância entre as linhas de sinal (4,5 mils) na camada interna é de 7,0 mils.

4). A distância entre as linhas na camada superficial e na camada interna é de 4,0 mils.

5). A distância entre as linhas de sinal diferencial na camada interna e entre elas e outras linhas de sinal deve ser mantida em pelo menos 25mils.

6). A distância entre as linhas de sinal diferencial na camada superficial e entre elas e outras linhas de sinal deve ser mantida em pelo menos 20mils.

Após a impressão do PCB, a impedância da placa de teste é testada pelo testador de impedância POLAR-Cits500 com resultados na tabela a seguir. Os dados indicam que a impedância deve ser controlada na faixa de 50Ohmۯ%, 60Ohmۯ% e 100Ohmۯ% no processo de projeto e fabricação de PCB de alta velocidade.

| Impedância predefinida (Ohm) | Impedância prática (Ohm) |

| 50 | 47,52-52,33 |

| 60 | 57,65-61,35 |

| 100 | 93,65-106,35 |

LVDS e seu controle de impedância em PCBs

• LVDS

LVDS é um tipo de nível de transmissão de sinal serial de alta velocidade com vantagens de alta velocidade de transmissão, baixo consumo de energia, forte capacidade anti-interferência, longa distância de transmissão e correspondência viável. Os campos de aplicação do LVDS incluem informática, comunicação e consumo.

• Projeto de impedância de LVDS

O LVDS apresenta uma oscilação de tensão de apenas 350MV com a maior distância de transmissão de mais de 10 metros. Para garantir que os sinais não sejam influenciados pelo sinal refletido no processo de transmissão do sinal nas linhas de transmissão, a impedância das linhas de transmissão deve estar sob controle com impedância de linha única de 50 Ohms e impedância diferencial de 100 Ohms. Na aplicação prática, a impedância pode ser controlada definindo espessura de empilhamento razoável e parâmetros médios, ajustando a largura da linha e a distância entre as linhas e calculando a impedância de linhas simples e linhas diferenciais com a ajuda de algumas ferramentas de análise de simulação de alta velocidade.

No entanto, na maioria das vezes, é relativamente difícil atender aos requisitos de impedância de linha única e impedância diferencial. Por um lado, a faixa de ajuste da largura da linha W e da distância entre as linhas S é controlada pelo espaço físico do projeto. Por exemplo, o roteamento e a largura da linha nos conectores de margem com BGA ou DIP são influenciados pelo tamanho e pela distância do bloco. Por outro lado, a mudança de W e S influenciará o resultado de linha simples e impedância diferencial. Até agora, é fácil e conveniente descobrir a relação entre a largura da linha pré-definida e a distância da linha.

• Regras de roteamento LVDS

De um modo geral, o roteamento de sinal diferencial é implementado de acordo com as regras de projeto de impedância, o que é capaz de garantir a qualidade do LVDS. No roteamento prático, o LVDS deve obedecer às seguintes regras:

1). Os pares diferenciais devem ser o mais curtos possível, as linhas devem ser retas e o número de furos passantes deve ser reduzido. A distância entre as linhas de sinal em pares diferenciais deve ser a mesma. Todas essas regras contribuem para evitar longas rotas e vários desvios. Quanto aos desligamentos, o desligamento de 45 graus deve ser usado em vez de 90 graus.

2). A distância entre os pares diferenciais deve ser mantida mais de 10 vezes para diminuir a diafonia entre as linhas. Quando necessário, furos passantes de aterramento podem ser colocados entre pares diferenciais para isolamento.

3). O LVDS não pode ser dividido na superfície. Embora dois sinais diferenciais sejam caminhos de retorno mútuos, o caminho de retorno do sinal não pode ser cortado como resultado da divisão na superfície. No entanto, as linhas de transmissão possivelmente levarão à descontinuidade da impedância como resultado da falta de planos de imagem.

4). Evite sinal diferencial entre camadas. Durante a fabricação de PCB, a precisão de alinhamento de empilhamento entre camadas é muito menor do que a precisão de gravação na mesma camada mais a perda média durante o empilhamento, o que leva à alteração da impedância diferencial entre os pares diferenciais.

5). No projeto de impedância, o método de acoplamento deve ser usado.

6). A estrutura de empilhamento de PCB adequada deve ser definida para garantir o isolamento entre os sinais de nível de tensão e o LVDS. Quando possível, sinais como TTL/CMOS de alta velocidade podem ser configurados em diferentes camadas, isoladas do roteamento LVDS por camadas de terra e energia.

7). Os pares de sinais diferenciais devem ser compatíveis com o comprimento do roteamento.

Recursos úteis

• Elementos que afetam a impedância característica de PCB e soluções

• Considerações de projeto de impedância para PCB Flex-Rígida

• Como analisar e proibir a impedância de alimentação de PCB de alta velocidade

• Controle de impedância de vias e sua influência na integridade do sinal no projeto de PCB

• Serviço completo de fabricação de PCB da PCBCart - Múltiplas opções de valor agregado

• Serviço avançado de montagem de PCB da PCBCart - Comece a partir de 1 peça

Tecnologia industrial

- Software de layout de PCB

- Causas de corrosão do PCB

- Considerações de layout de PCB

- Considerações de projeto de impedância para PCB flexível

- Retrocessos e soluções no projeto de PCB de RF

- 3 técnicas de roteamento no projeto de circuito de sinal de alta velocidade PCB

- Dicas de layout de alta velocidade

- Análise de integridade de sinal e projeto de PCB em circuito misto analógico-digital de alta velocidade

- Desafios de projeto de PCB de alta velocidade sobre integridade do sinal e suas soluções

- Controle de impedância de vias e sua influência na integridade do sinal no projeto de PCB