Como analisar e proibir a impedância de alimentação de PCB de alta velocidade

Com o aumento da complexidade do design de PCB, a fonte de alimentação estável e confiável tornou-se uma nova tendência de pesquisa em design de PCB de alta velocidade. Especialmente quando o número de componentes de comutação continua melhorando constantemente e o Vcore diminuindo constantemente, a flutuação de energia tende a trazer uma influência mortal ao sistema. Portanto, tornou-se um ponto-chave no design de PCB de alta velocidade para manter a estabilidade do sistema de energia.

No entanto, como resultado da existência de impedância do sistema de potência, uma queda de tensão relativamente grande é gerada pela corrente transitória de carga na impedância do sistema de potência, o que leva à instabilidade do sistema. Para garantir que a energia normal seja fornecida a cada componente do início ao fim, a impedância no sistema de energia deve ser controlada, o que significa que a impedância deve ser diminuída o máximo possível.

A aplicação de capacitor de desacoplamento é uma forma eficaz de proibir a impedância no sistema de potência. Este artigo analisa as razões para a proibição de impedância no sistema de potência por desacoplamento de capacitor e lista métodos em termos de seleção de capacitor de desacoplamento. Além disso, pesquisa principalmente como determinar a posição do capacitor de desacoplamento com base na análise harmônica para maximizar a proibição de impedância no sistema de potência.

Análise de impedância

Potência e terra podem ser considerados como um grande capacitor de placa cuja capacidade é calculada com base na fórmula C=kAr/d

Nesta fórmula, k é 0,2249 polegada; A refere-se à área paralela entre dois planos; r refere-se à constante dielétrica do meio e é 4,5 para o material de placa FR4 comumente usado; d refere-se à distância entre energia e terra. Um PCB com o tamanho de 2x1 polegada é escolhido como exemplo. A capacitância do capacitor formado por potência e terra com área paralela de 20Mils é aproximadamente 0,2249x4,5x2x1/0,02=101,2pF. Com base nesta fórmula, pode-se indicar que a capacitância de desacoplamento no sistema de potência é tão pequena que a impedância correspondente será muito grande, geralmente alguns ohms. Portanto, está longe de ser suficiente diminuir a impedância através do autodesacoplamento no sistema de potência.

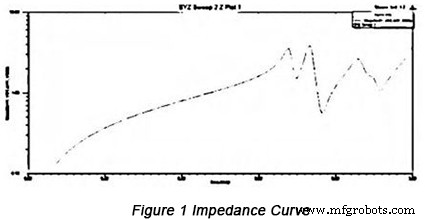

Uma ferramenta de simulação SIWAVE no nível 2.5D é aplicada para implementar a simulação de impedância no dispositivo ativo. A rede de energia e terra U41 é apanhada para calcular os parâmetros XYZ com uma faixa de varredura de 0 a 1GHz, através da qual é obtida uma curva de impedância na Figura 1 abaixo.

No diagrama, pode-se ver que a curva de impedância muda com a mudança de frequência e a impedância muda muito nos pontos de inflexão no valor de 670MHz, 730MHz e 870MHz.

Métodos de proibição

• Análise teórica sobre proibição de impedância por capacitor de desacoplamento

Como é impossível diminuir a impedância através do desacoplamento da própria energia, o capacitor de desacoplamento deve ser aplicado para proibir a impedância.

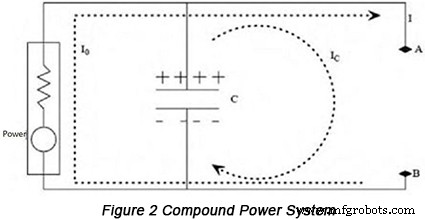

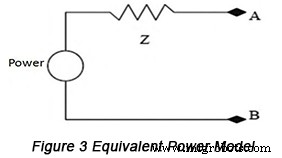

A Figura 2 é um diagrama do sistema de potência composto. A Figura 3 indica este sistema de potência em um modelo de potência equivalente.

Uma fórmula pode ser aplicada para representar este circuito:V=ZxL. Uma circunstância deve ser alcançada que, mesmo que a corrente transitória da carga mantenha uma grande mudança entre o ponto A e o ponto B, a mudança de tensão deve ser muito pequena entre os dois pontos. Com base na fórmula, este objetivo nunca pode ser obtido a menos que o valor da impedância (Z) seja suficientemente pequeno. Na Figura 3, a aplicação do capacitor de desacoplamento auxilia na implementação deste objetivo, pois pode-se indicar que o capacitor de desacoplamento é capaz de diminuir a impedância no sistema de potência do ponto de vista da equivalência. Além disso, da perspectiva dos princípios do circuito, a mesma conclusão pode ser mantida. Capacitor apresenta baixa impedância em sinais de corrente alternada. Como resultado, a participação do capacitor certamente diminuirá a impedância da corrente alternada no sistema de energia.

• Seleção da capacitância do capacitor de desacoplamento

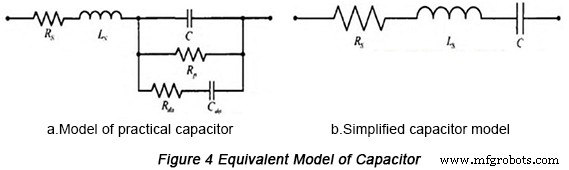

Nunca existe um capacitor ideal, ele sempre contém parâmetros parasitas. A maior influência no desempenho de alta frequência do capacitor deriva de ESR (Effective Series Inductance) e ESL (Effective Series Resistance). A Figura 4 mostra o modelo equivalente considerando os parâmetros parasitas.

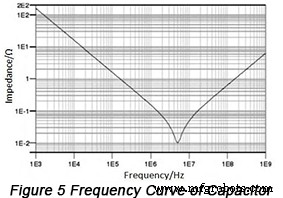

O capacitor também pode ser considerado como um circuito harmônico em série com a frequência harmônica em série seguindo a fórmula:f=1/2PIFC. Quando permanece na circunstância de baixa frequência, exibe capacitância. No entanto, quando a frequência aumenta, ele exibe constantemente sua indutância. Dito de outra forma, sua impedância aumentará primeiro e depois diminuirá com o aumento da frequência e o valor mínimo da impedância equivalente ocorre na frequência harmônica em série f0 . Neste momento, a reatância capacitiva e a reatância indutiva são corretamente compensadas, mostrando a equivalência entre o valor da impedância e ESR com a menor resistência equivalente do capacitor. A curva de frequência do capacitor é mostrada na Figura 5.

Portanto, no processo de seleção do capacitor, o ponto de frequência harmônico do capacitor escolhido cai adjacente ao ponto de frequência que sofrerá desacoplamento. Seu desempenho capacitivo deve ser totalmente aplicado e usado antes da frequência auto-harmônica sempre que possível.

Diferentes capacitores com diferentes capacitâncias são compatíveis com diferentes frequências auto-harmônicas são exibidas na tabela abaixo.

| Capacitância | DIP (MHz) | STM (MHz) |

| 1,0μF | 2,5 | 5 |

| 0,1μF | 8 | 16 |

| 0,01μF | 25 | 50 |

| 1000pF | 80 | 160 |

| 100pF | 250 | 500 |

| 10pF | 800 | 1,6(GHz) |

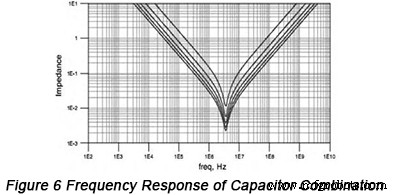

Geralmente, as propriedades harmônicas do capacitor de desacoplamento devem ser aplicadas e a impedância de entrada mais baixa é obtida através da combinação paralela de capacitores. A resposta de frequência paralela do mesmo tipo de capacitor é ilustrada na Figura 6 abaixo.

Com base neste método, ESR e ESL equivalentes podem ser bastante reduzidos. Para capacitores múltiplos (n) com a mesma capacitância, a capacitância equivalente C torna-se nC após a combinação, enquanto a indutância equivalente L torna-se L/n, ESR equivalente torna-se R/n. No entanto, a frequência harmônica permanece inalterada. Pode-se ver que, como as frequências auto-harmônicas são as mesmas para diferentes tipos de capacitores, quanto mais capacitores paralelos, menor a impedância na área capacitiva e indutiva, com o ponto de frequência auto-harmônica inalterado.

Em conclusão, no processo de seleção de capacitores de desacoplamento, a frequência de desacoplamento deve ser considerada como ponto de desacoplamento de frequência auto-harmônica para que o capacitor correspondente possa ser captado. Além disso, a aplicação paralela de múltiplos capacitores com a mesma capacitância é capaz de melhorar a capacidade de desacoplamento e reduzir a impedância.

• Determinação das posições dos capacitores de desacoplamento

Após a seleção dos capacitores de desacoplamento, suas posições devem ser levadas em consideração. O plano de potência e terra pode ser considerado como uma rede composta por múltiplos indutores e capacitores ou uma cavidade ressonante. Em uma determinada frequência, ocorre ressonância para indutores e capacitores, influenciando a impedância no sistema de potência. Com a melhoria da frequência, a impedância muda constantemente, especialmente quando a ressonância paralela se mantém notável, a impedância também aumenta notavelmente. Portanto, as posições específicas dos capacitores de desacoplamento devem ser asseguradas juntamente com a análise harmônica da PCB.

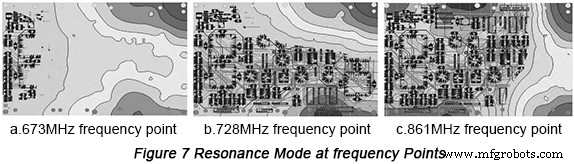

Com a função de análise de ressonância da ferramenta de simulação SIWAVE aplicada, parâmetros equivalentes são conduzidos incluindo resistência, capacitância e indutância. Além disso, a análise de ressonância do PCB deve ser implementada com o modo de ressonância em diferentes pontos de frequência obtidos, conforme mostrado na Figura 7.

Acoplado com a Figura 1, pode-se observar que vários pontos de frequência com impedância relativamente grande são compatíveis com pontos de frequência nos quais a ressonância é gerada. Portanto, com o resultado da análise de ressonância, pode-se concluir que na área com graves ressonâncias de desacoplamento devem ser colocados capacitores com capacitância adequada para reduzir a impedância.

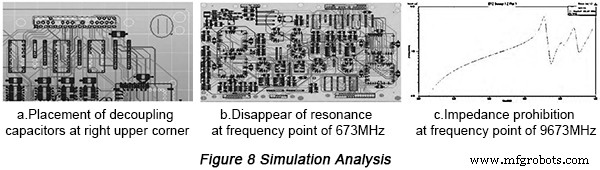

Tomando como exemplo o ponto de frequência de 673MHz, os capacitores de desacoplamento podem ser colocados em paralelo para que a ressonância seja encontrada perdida e a impedância correspondente seja proibida, conforme mostrado na Figura 8.

Com base na análise de ressonância do PCB, as posições correspondentes nas quais ocorre a ressonância podem ser determinadas, com base em quais capacitores com tamanho adequado são colocados em paralelo para proibir a impedância.

Recursos úteis

• Elementos que afetam a impedância característica de PCB e soluções

• Controle de impedância no projeto de PCB de circuito digital de alta velocidade

• Considerações de projeto de impedância para PCB Flex-Rígido

• Impedância Controle de Vias e Sua Influência na Integridade do Sinal no Projeto de PCB

• Serviço de Fabricação de PCB Completo da PCBCart - Várias opções de valor agregado

• Serviço Avançado de Montagem de PCB da PCBCart - Comece a partir de 1 peça

Tecnologia industrial

- Séries R, L e C

- Falhas na fonte de alimentação e como se proteger

- Sarampo e delaminação de PCB

- Como auditar um fornecedor de PCB

- Como fazer engenharia reversa de uma PCB

- Placas de circuito impresso e como elas funcionam?

- Discussão sobre potência e aterramento em compatibilidade eletromagnética de PCB

- Processamento isométrico diferencial e verificação de simulação de projeto de PCB de alta velocidade

- Desafios de projeto de PCB de alta velocidade sobre integridade do sinal e suas soluções

- Descarga eletrostática:o que é, como ocorre e como resolvê-lo?